## Universitá di Pisa Dottorato di ricerca in Ingegneria dell'Informazione

# DESIGN AND EXPERIMENTAL VERIFICATION OF IC TECHNIQUES FOR HARSH ENVIRONMENTS: AUTOMOTIVE, AEROSPACE AND HEP CASE STUDIES

DOCTORAL THESIS

Author Gabriele Ciarpi

Tutor Prof. Sergio Saponara

Reviewers Dr. PhD. Fabrizio Palla Dr. PhD. Tobias Erlbacher

The Coordinator of the PhD Program **Prof. Fulvio Gini**

Pisa, November 2019

XXXII Ciclo

"I am always doing what I cannot do yet, in order to learn how to do it." Vincent Van Gogh

# Acknowledgements

would like to express my sincere gratitude to my supervisor Prof. Sergio Saponara for the continuous support of my thesis and related research, for his patience, motivation, and experience. His guidance helped me in all the time of research and writing of this thesis.

My sincere thanks also goes to Dr. Fabrizio Palla who provided me the opportunity to join in INFN and CERN as intern, and who gave access to the laboratory and research facilities. Without his precious support it would not be possible to conduct this research.

I also thank the previous coordinator of the PhD program Prof. Marco Luise for his support to the PhD students in these years.

I thank my friends and fellow labmates: Gianmarco, Danilo, Simone, Alessio, and Pierpaolo for the stimulating discussions, for the sleepless nights, and for all the fun we have had during the last three years.

Last but not the least, I would like to thank my girlfriend and family: my parents, my brother and sister for supporting me spiritually throughout writing this thesis and my life in general.

## Summary

oday's incredible growth of the consumer electronics market is flanked by the pervasive diffusion of electronic devices in harsh environments. In these contexts, Integrated Circuits (ICs) have to withstand rugged conditions that affect the proper functioning of silicon devices. Different environments can be characterized by one or more harsh conditions that degrade the performances of the electronic devices. Although today's automotive and aerospace worlds are two of the most difficult environments where ICs can operate, the next generation of space and terrestrial vehicles will be ever-more managed by electronic systems. Indeed, they will be filled on a side by high-power systems used for electrical motors, traction, braking, and other functions, and on the other side by extremely sensitive sensors and circuits capable of detecting the minimal physical variation. This increment in the number of onboard electronic devices will require ever-more electric energy stored in batteries and everbetter management of them.

Today's onboard power management trend shows the coexistence of multi-levels voltage domains, such as 48 V, 12 V, and 5 V, to supply different electronic sub-systems. For these reasons, in this thesis work, techniques to withstand issues deriving from multi-voltage domains systems are proposed in an inductorless DC/DC converter design framework. The integrated DC/DC converter, designed in 0.35 µm HV technology, is able to convert a wide range of input voltages, from 6 V to 60 V, in two output points of loads, 5 V and 1.65 V, for sensors supply. At the best of the author's knowledge, this is the first silicon integrated inductorless DC/DC converter, in literature or market, able to convert such a wide input range. This wide range is managed using a multi-stage cascade architecture with reconfigurable switched capacitors stages and high-voltage MOSFETs. In addition, in response to strong fault-management requirements of safety-critical systems, an innovative and integrable fault-tolerant technique is proposed in this thesis. It, using the switched capacitors technique, is able to insulate the low-voltage loads from high-voltage inputs also in case of failures, avoiding the state-of-the-art use of cumbersome transformers.

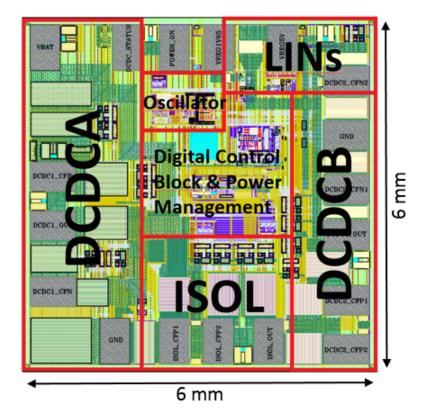

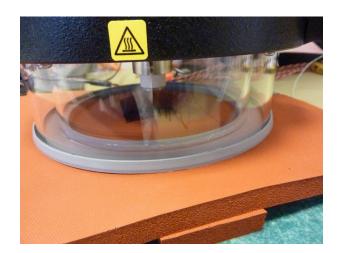

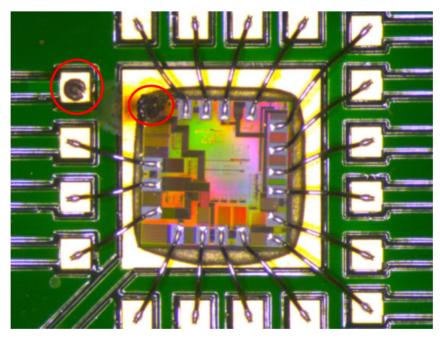

The IC DC/DC converter was implemented in  $6*6 \text{ mm}^2$  chip, and in response to the growing requirement of ever-more integration, the measurement campaign of the in-

ductorless DC/DC converter was focused on the comparison between the performances extracted from a classical 2D configuration, with external passives placed side-by-side with the IC, and an innovative 3D assembled structure, with silicon capacitors stacked on the chip of the DC/DC converter. The electrical measurements showed the feasible use of the compact 3D structure for area reduction purposes, maintaining nearly the same 2D conversion performances.

In order to verify compliance with the space environment, the designed IC DC/DC converter was exposed to cumulative dose and heavy-ions radiation tests. The first test, performed with X-rays exposure, showed a radiation-tolerant level up to 43 krad, highlighting the feasible use of the DC/DC converter for the Heart-Moon travels. The second test, used to generate random faults in the converter control strategy, showed the reliability of the insulation stage to prevent high-voltages damaging of the supplied loads.

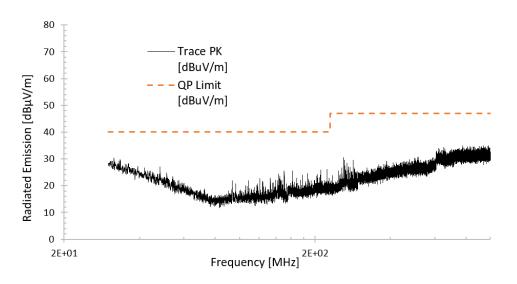

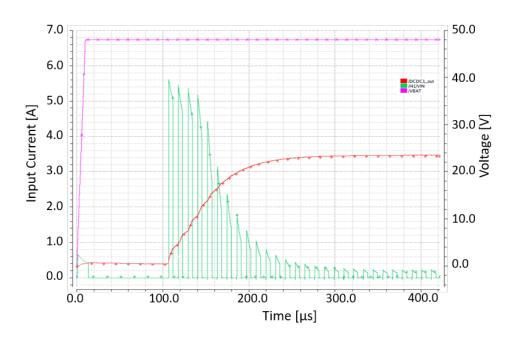

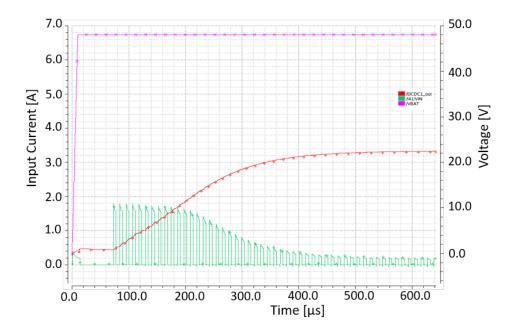

Since the ever-growing requirement of compact systems, the electromagnetic interaction between different devices is one of the hardest challenges in today's electronic design. Being the switching DC/DC converter one of the main generators of electromagnetic disturbances, some techniques to mitigate the generation of these disturbances have been adopted, in this thesis, at the ICs design level. In particular, techniques such as input filter and soft-start have been implemented to reduce conducted interference, instead low-switching frequency, inductorless architecture and spread spectrum techniques have been used to mitigate radiated interference.

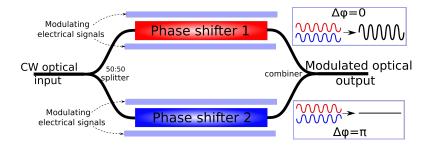

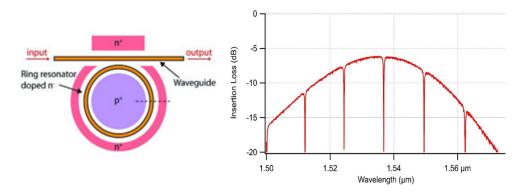

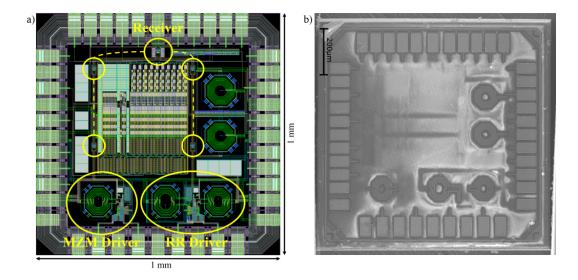

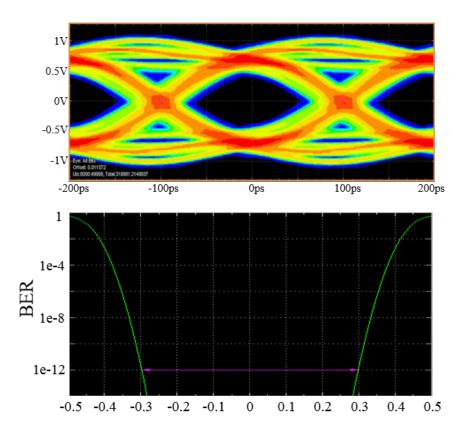

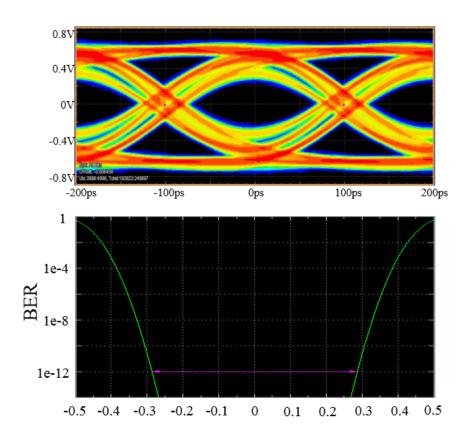

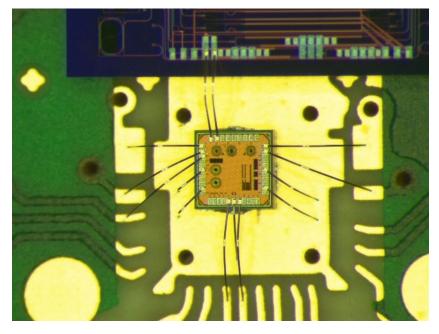

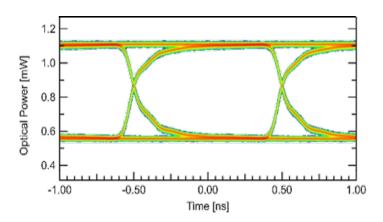

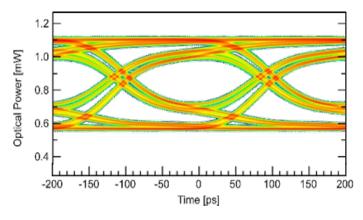

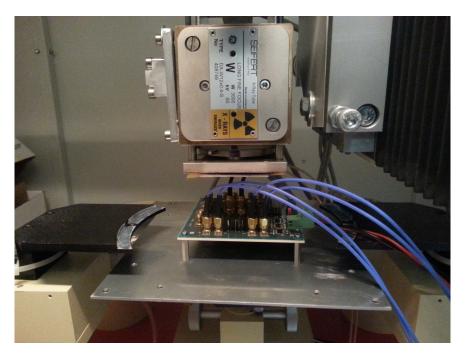

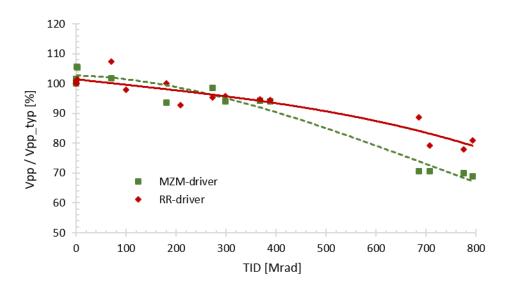

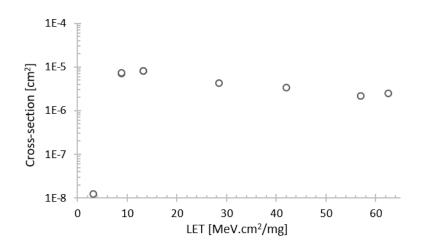

On the radiation side, the high-energy experiments, used by the particle physics for the verification of new theories, are characterized by radiation levels nearly three orders higher than that used for standard space applications. This extremely harsh condition heavily stresses the performances of state-of-the-art electronic devices used for particle detection. In order to guarantee the correct functioning of ICs when they operate in this challenging environment, in this thesis some Radiation Hardened By Design (RHBD) techniques to mitigate the radiation effects on silicon ICs are applied, such as current mode logic, double long MOSFETs and enclosed layout transistors. These RHBD techniques have been then used for the design of high-speed electro-optical modulator drivers in 65 nm CMOS technology. These multi-stage drivers, in addition to the rad-hard solutions, implement buffer chain and inductive peaking techniques for bandwidth extension. The drivers, realized in a 1\*1 mm<sup>2</sup> chip, were directly bonded on a carrier board and electrically tested, showing 5 Gbps data rate performances. The electron-optical modulators targeted in this work are the Mach Zehnder Modulator and the Ring Resonator, both realized on silicon-photonic technology. These modulators have shown higher radiation hardness property than the classical VCSEL (Vertical Cavity Surface Emitting Lasers), typically used on standard applications. The system-level test, performed bonding the silicon drivers chip with the silicon-photonics modulators chip through aluminum bonding wires, confirmed the achievement of a data rate up to 5 Gbps. In response to the radiation-hard requirement, the drivers chip was exposed to X-ray, showing its ability to work up to 800 Mrad, level of radiation that, today, no electronic device in literature or industry is able to reach.

# Sommario

'odierna incredibile crescita dell'elettronica di consumo è affiancata dalla pervasiva diffusione dei dispositivi elettronici negli ambienti più ostili. In questi contesti, i Circuiti Integrati (ICs) devono fronteggiare condizioni avverse che influiscono sul corretto funzionamento dei dispositivi in silicio. Ambienti differenti possono essere caratterizzati da una o più condizioni che degradano le prestazioni dei dispositivi. Nonostante gli attuali mondi automotive e aerospace siano due degli ambienti più ostili dove i ICs possono operare, la prossima generazione di veicoli terrestri e spaziali sarà sempre maggiormente gestita da sistemi elettronici. I veicoli saranno costellati, da un lato, da sistemi ad elevata potenza per la gestione dei motori elettrici, usati per la trazione, la frenata ed altre funzioni, e dall'altro lato, da sensori e circuiti estremamente sensibili in grado di rilevare la più piccola variazione fisica. L'incredibile numero di dispositivi elettronici a bordo richiederà una sempre maggiore quantità di energia elettrica immagazzinata nelle batterie e una sua sempre migliore gestione. L'attuale tendenza nella gestione della potenza di bordo mostra una coesistenza di diversi domini di tensione per l'alimentazione dei diversi sottosistemi elettronici, come 48 V, 12 V e 5 V. Per queste ragioni, in questo lavoro di tesi, alcune tecniche per affrontare gli effetti derivati da sistemi costituiti da domini multi-tensione sono proposti insieme alla progettazione di un convertitore DC/DC senza induttore. Il convertitore DC/DC, progettato nella tecnologia 0.35 µm HV, è in grado di convertire un ampio range di tensioni in ingresso, da 6 V a 60 V, in due punti di carico, 5 V e 1.65 V, per l'alimentazione di sensori. Dalla conoscenza dell'autore della letteratura e del mercato, questo è il primo convertitore DC/DC senza induttore in grado di convertire un range di ingresso così ampio. Questo ampio range è gestito usando un'architettura multi-stadio con stadi a condensatori commutati riconfigurabili e MOSFETs ad alta tensione.

In risposta ai pressanti requisiti per la gestione dell'errore in sistemi critici, un'innovativa e integrabile tecnica tollerante ai faults è proposta in questa tesi. Essa, usando la tecnica dei condensatori commutati, evita l'utilizzo degli ingombranti trasformatori usati nello stato dell'arte. Il convertitore è stato realizzato in un chip 6\*6 mm<sup>2</sup>, e in risposta alla crescente richiesta di sempre maggiore integrazione, la campagna di misura del convertitore DC/DC si è focalizzata sul confronto tra le prestazioni ottenute da una classica configurazione 2D, con i passivi situati a lato del chip, ed un'innovativa struttura 3D, con condensatori in silicio impilati sopra il chip. Le misure elettriche hanno mostrato la fattibilità dell'utilizzo della struttura 3D al fine di ridurre l'area occupata, mantenendo quasi le stesse prestazioni della configurazione 2D.

Per la verifica della compatibilità con l'ambiente spaziale del IC progettato, il convertitore è stato esposto a test di radiazione di dose accumulata e di ioni pesanti. Il primo test, eseguito con esposizione a raggi X, ha mostrato una tolleranza del convertitore DC/DC fino ad un livello di 43 krad, evidenziando la possibilità di un suo impiego per viaggi Terra-Luna. Il secondo test, usato per generare fallimenti casuali nella strategia di controllo del convertitore, ha dimostrato l'affidabilità dello stadio isolatore nella prevenzione dei danneggiamenti dei dispositivi alimentati dal convertitore. Data la sempre crescente richiesta di sistemi compatti, l'interazione elettromagnetica tra dispositivi differenti è una delle maggiori sfide nell'odierna progettazione elettronica. Essendo il convertitore DC/DC switching uno dei principali generatori di disturbi elettromagnetici, alcune tecniche per mitigare la generazione di questi disturbi sono state adottate in questa tesi, al livello di progettazione del chip. In particolare, tecniche come l'adozione di un filtro d'ingresso e il soft-start sono state implementate per ridurre le interference condotte, mentre techniche come una bassa frequenza di switching, un'architettura senza induttore e l'allargamento dello spettro sono state usate per la mitigazione delle interferenze irradiate.

Sul fronte radiazioni, gli esperimenti ad alta energia, usati nella fisica particellare per la verifica di nuove teorie, sono caratterizzati da livelli di radiazione quasi tre ordini di grandezza superi rispetto alle applicazioni spaziali standard. Queste estreme condizioni stressano pesantemente le prestazioni dei dispositivi elettronici dello stato dell'arte usati per la rilevazione delle particelle. Per garantire la corretta operazione dei ICs operanti in questo ambiente, in questa tesi sono state sviluppate alcune tecniche Radiation Hardened By Design (RHBD) per la mitigazione degli effetti sui ICs dovuti alle radiazioni, come la logica current-mode, una lunghezza dei MOSFETs doppia e l'enclosed layout dei transistors. Queste tecniche RHBD sono state utilizzate per la progettazione di drivers per modulatori elettro-ottici ad elevata velocità in tecnologia CMOS 65 nm. I driver multistadio, in aggiunta alle soluzioni per fronteggiare le radiazioni, implementano tecniche di buffer chain e inductive peaking per l'estensione della banda. I driver, realizzati in un chip 1\*1 mm<sup>2</sup>, sono stati connessi direttamente su una board e testati elettricamente, mostrando buone prestazioni fino a 5 Gbps. I modulatori elettro-ottici usati in questo lavoro sono il modulatore Mach Zehnder ed il Ring Resonator realizzati in tecnologia silicon-photonic, i quali hanno mostrato maggiori proprietà di resistenza alle radiazioni rispetto ai classici VCSEL (Vertical Cavity Surface Emitting Lasers), tipicamente utilizzati in applicazioni standard. I test a livello di sistema, eseguiti connettendo il chip in silicio dei drivers ed il chip in silicon-photonics dei modulatori attraverso bonds in alluminio, confermano il raggiungimento di una velocità di trasmissione di 5 Gbps. In risposta al requisito di tolleranza alle radiazioni, il chip dei drivers è stato esposto a raggi X, mostrando la sua abilità ad operare fino a 800 Mrad, livello di radiazione che oggi nessun altro dispositivo elettronico presente in letteratura o industria è in grado di raggiungere.

# List of publications

#### **International Journals**

- G. Ciarpi, G. Magazzù, F. Palla, S, Saponara: "Design, Implementation and Experimental Verification of 5 Gbps, 800 Mrad TID and SEU-Tolerant Optical Modulators Drivers", *IEEE Transaction on Circuit and System-I: Regular Papers*, 2019, n. 67, pp. 829-838.

- F. Palla, G. Ciarpi, G. Magazzù, S. Saponara: "Design of a High Radiation-Hard Driver for Mach-Zehnder Modulators based High-Speed links for Hadron Collider Applications", *Nuclear Instruments and Methods in Physics Research, Section A: Accelerators, Spectrometer, Detectors and Associated Equipment*, 2019, n. 936, pp. 303-304.

- S. Saponara, G. Ciarpi, T. Erlbacher, G. Rattman: "Integrated Passive Devices and Switching Circuit Design for a 3D DC/DC Converter up to 60 V", *Journal of Circuit, Systems and Computers*, 2019, vol. 29, n. 3.

- S. Saponara, G. Ciarpi: "IC Design and Measurement of an Inductorless 48 V DC/DC Converter in Low-Cost CMOS Technology Facing Harsh Environments", *IEEE Transaction on Circuit and System-I: Regular Papers*, Jan 2018, vol. 65, pp. 380-393.

- 5. S. Saponara, G. Ciarpi: "Electrical, Electromagnetic, and Thermal Measurements of 2-D and 3-D Integrated DC/DC Converters", *IEEE Transaction on Instrumentation and Measurement*, May 2018, vol. 67, pp. 1078-1090.

- S. Saponara, G. Ciarpi, V. Z. Groza: "Design and Experimental Measurement of EMI Reduction Techniques for Integrated Switching DC/DC Converters", *IEEE Canadian Journal of Electrical and Computer Engineering*, vol. 40, pp. 116-127, Spring 2017.

#### International Conferences/Workshops with Peer Review

7. G. Ciarpi, G. Magazzù, A. Kraxner, F. Palla, S. Saponara, C. Scarcella, J. Troska, F. Vasey, "Design and operation of radiation hard 65 nm drivers for Silicon Pho-

tonics based optical links", TWEEP2019, Topical Workshop on Electronics for Particle Physics.

- D. Monda, G. Ciarpi, G. Mangraviti, L. Berti, S. Saponara, "Analysis and Comparison of Ring and LC-tank Oscillators for 65 nm Integration of Rad-Hard VCO for SpaceFibre Applications", *Application in Electronics Pervading Industry Environment and Society*, 2019, SpringerNature Lecture Notes in Electronical Engineering 2019.

- G. Ciarpi, S. Cammarata, S. Faralli. P. Velah, G. Magazzù, F. Palla, F. Di Pasquale, S. Saponara, "Design, Operation and BER Test of Multi-Gb/s Rad-Hard Drivers in 65 nm Technology for Silicon Photonics Optical Modulators", *Application in Electronics Pervading Industry Environment and Society*, 2019, SpringerNature Lecture Notes in Electronical Engineering 2019.

- S. Di Pascoli, G. Ciarpi, S. Saponara: "Sound-based detection and ranging system as example application of a rapid prototyping and low-cost technology for boardlevel electronic systems education", *Lecture Notes in Electronical Engineering*, 2019, vol. 550, pp. 421-427.

- S. Saponara, G. Ciarpi, F. Giannetti: "Analysis and simulations of mmW transceiver for System-in-Package communications", *Lecture Notes on Electrical Engineering Springer*, vol. 512, pp.99-106, 2019.

- G. Ciarpi, S. Saponara, G. Magazzù, F. Palla: "Radiation Hardness by Design Techniques for 1 Grad TID Rad-Hard Systems in 65 nm standard CMOS Technologies", *Lecture Notes in Electronical Engineering*, 2019, vol. 550, pp. 421-427.

- G. Meoni, L. Pilato, G. Ciarpi, A. Palla, L. Fanucci: "Fully Digital Low-Power Implementation of an Audio Front-End for Portable Applications", *Lecture Notes in Electronical Engineering*, 2019, vol. 550, pp. 437-443.

- 14. G. Magazzù, G. Ciarpi, S. Saponara: "Design of a radiation-tolerant high-speed driver for Mach Zehnder Modulators in High Energy Physics", *IEEE International Symposium on Circuit and Systems (ISCAS)*, May 2018.

- 15. S. Saponara, G. Magazzù, G. Ciarpi: "A high-speed driver for silicon photonics Mach-Zehnder modulator for high data-rate transfer of particle collision images in high-energy physics and in medical physics", *SPIE Real-Time Image and Video Processing 2018*, May 2018.

- G. Ciarpi, G. Magazzù, F. Palla, S. Saponara: "Design of Radiation Hard MZM Drivers", *IEEE/AEIT 20th Italian National Conference on Photonic Technologies* (Fotonica 2018), May 2018.

- 17. S. Saponara, G. Ciarpi, B. Neri: "System-level modelling/analysis and LNA design in low-cost automotive technology of a V2X wireless transceiver", *IEEE Research and Technologies for Society and Industry*, September 2017.

- S. Saponara, G. Ciarpi: "Electrical and electromagnetic measurements of an inductorless DC/DC converter", *IEEE International Instrumentation and Measurement Technology Conference (I2MTC)*, May 2017.

- 19. S. Saponara, G. Ciarpi, L. Fanucci: "Failure Analysis of Plastic Packages for Low-Power ICs", *Lecture Notes on Electrical Engineering Springer*, vol. 429, pp.160-166, 2017.

- 20. S. Saponara, G. Ciarpi: "Universal and inductorless DC/DC converter for multioutput power supplies in sensor and actuator networks", *SPIE Microtechnologies*, May 2017.

- A. Sisto, S. Saponara, G. Ciarpi, L. Fanucci: "Testing of DC/DC Converters for 48 V Electric Vehicles", *Lecture Notes on Electrical Engineering Springer*, vol. 429, pp.86-92, 2017.

- 22. S. Saponara, G. Ciarpi, C. Mattaliano, L. Fanucci, V. Groza: "Improving electromagnetic compatibility of integrated switching converters for hybrid/electric vehicles", *IEEE Electrical Power and Energy Conference*, October 2016.

# Contents

| 1 | Introduction                                                      | 1  |

|---|-------------------------------------------------------------------|----|

|   | 1.1 Open Challenges on ICs Operating in Harsh Environments        | 1  |

|   | 1.2 Thesis structure                                              | 3  |

| 2 | IC Design Challenge in Automotive, Aerospace and HEP Environments | 4  |

|   | 2.1 Automotive                                                    | 4  |

|   | 2.2 Aerospace                                                     | 6  |

|   | 2.3 High Energy Physics                                           | 8  |

| 3 | High-Voltage and Fault Mitigation Design Techniques               | 10 |

|   | 3.1 Switched Capacitor Converters                                 | 10 |

|   | 3.2 Converter Architecture                                        | 12 |

|   | 3.3 Circuit/Transistor-Level Converter Sizing                     | 14 |

|   | 3.3.1 Eqivalent Output Resistance of each SC stage                | 14 |

|   | 3.4 Switches typologies                                           | 16 |

|   | 3.5 First DC/DC converter stage                                   | 20 |

|   | 3.6 Second DC/DC converter stage                                  | 24 |

|   | 3.7 Insulator stage                                               | 25 |

|   | 3.8 Linear Regulators                                             | 28 |

|   | 3.9 Gate drivers                                                  | 28 |

|   | 3.10 Control Unit                                                 | 29 |

|   | 3.11 IC Layout and Post-Layout Simulations                        | 30 |

| 4 | High-Voltage and Fault Mitigation Design Techniques Verification  | 33 |

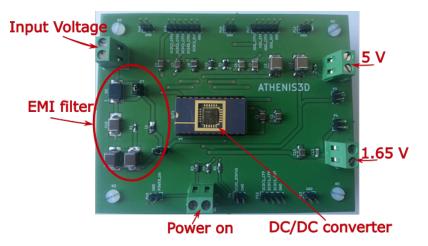

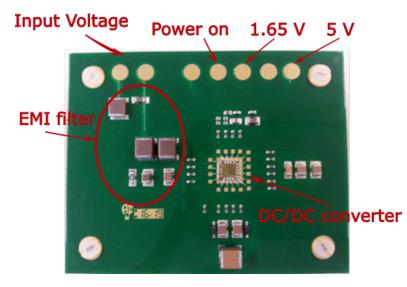

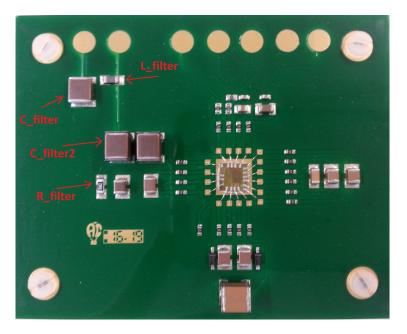

|   | 4.1 Testing Boards Implementations                                | 34 |

|   | 4.2 Electrical Measurements                                       | 35 |

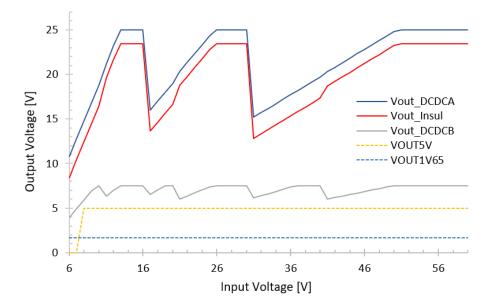

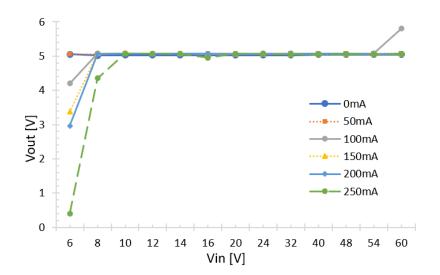

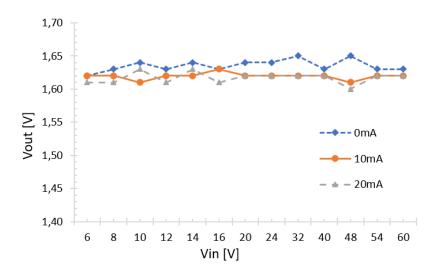

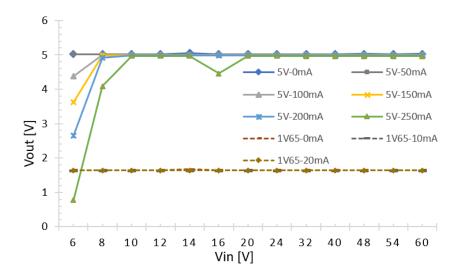

|   | 4.2.1 Line Regulation                                             | 36 |

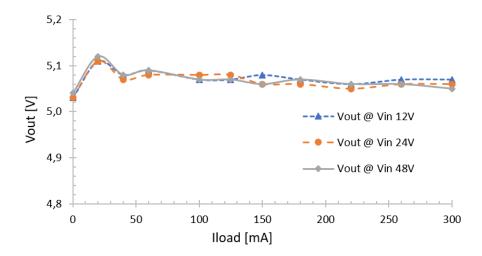

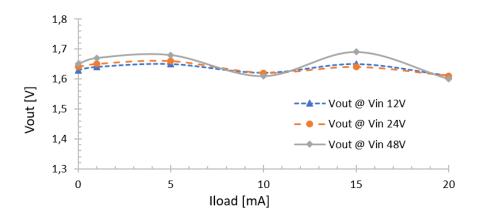

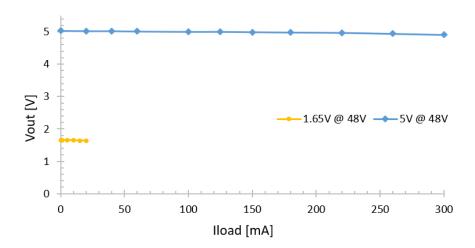

|   | 4.2.2 Load Regulation                                             | 36 |

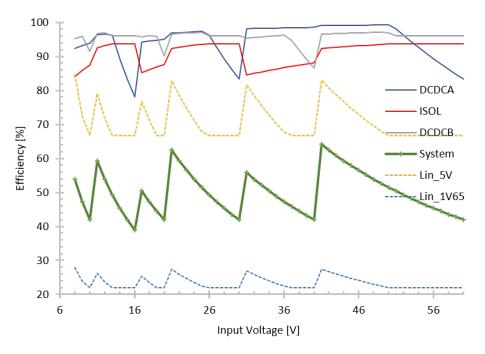

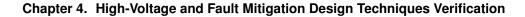

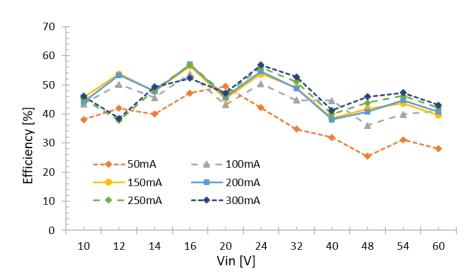

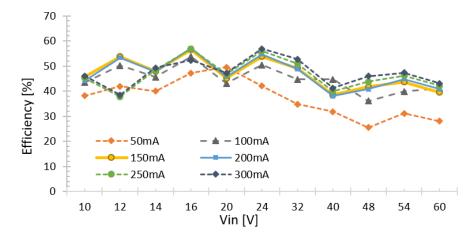

|   | 4.2.3 Efficiency                                                  | 37 |

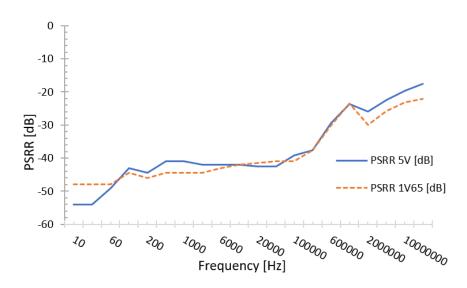

|   | 4.2.4 Power Supply Rejection Ratio                                | 39 |

|   | 4.3 Insulator Test                                                | 41 |

#### Contents

|   |      | 4.3.1 Overvoltage Fault Test                                                      | 42  |

|---|------|-----------------------------------------------------------------------------------|-----|

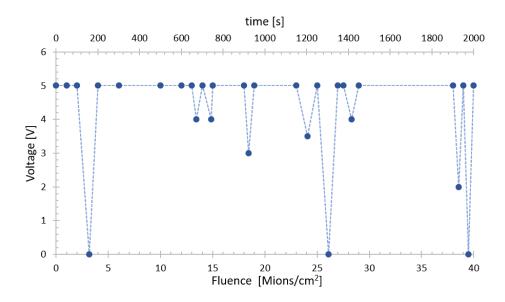

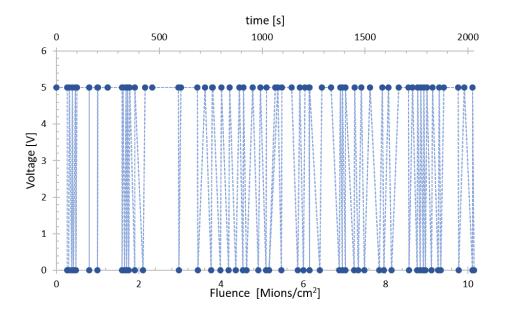

|   |      | 4.3.2 Single Event Effect Fault Test                                              | 43  |

|   |      | 4.3.3 Total Ionizing Dose Effects                                                 | 45  |

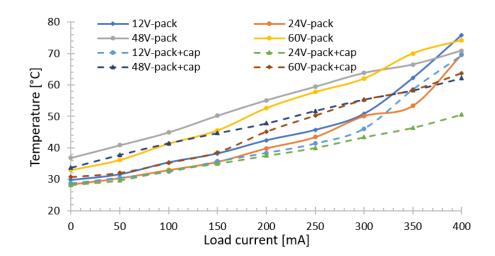

|   | 4.4  | Thermal Measurements                                                              | 46  |

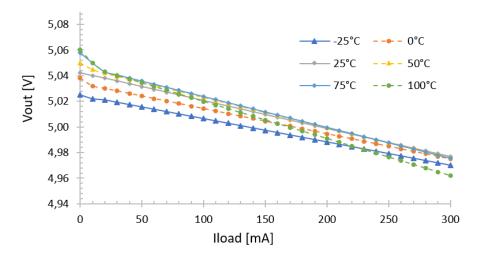

|   |      | 4.4.1 Performances at Different Environment Temperatures                          | 46  |

|   |      | 4.4.2 Thermal Profile of the Converter                                            | 46  |

|   | 4.5  | Electrical Comparison to State-of-the-art                                         | 49  |

| 5 |      | tromagnetic Interference reduction techniques, Development and Verification       | 51  |

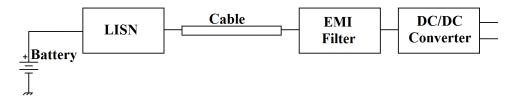

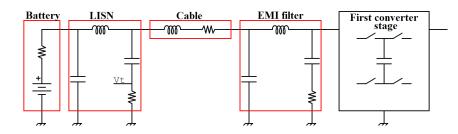

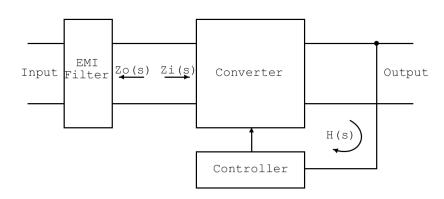

|   |      | Front-end and DC/DC Converter Models                                              | 51  |

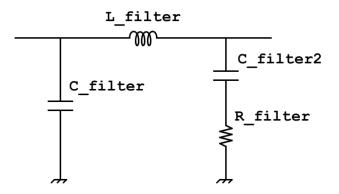

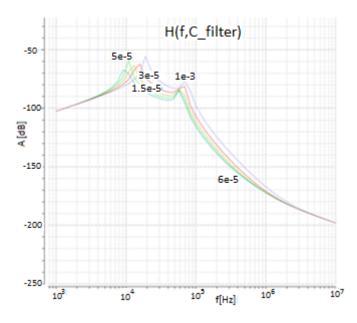

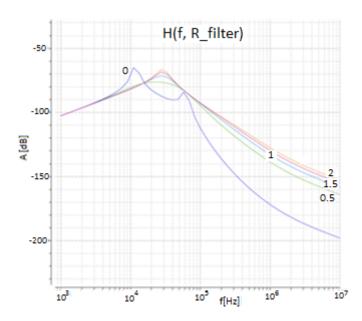

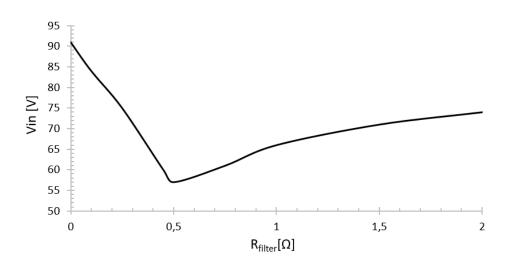

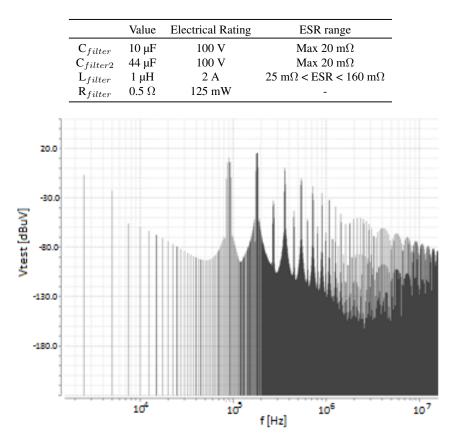

|   | 5.2  | Design of an Anti-conducted EMI Filter                                            | 52  |

|   |      | 5.2.1 Classic Approach                                                            | 53  |

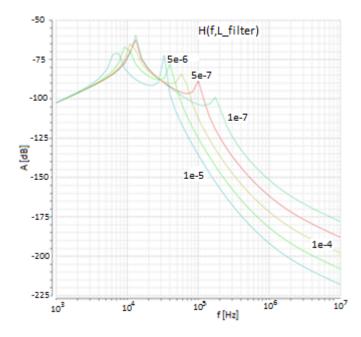

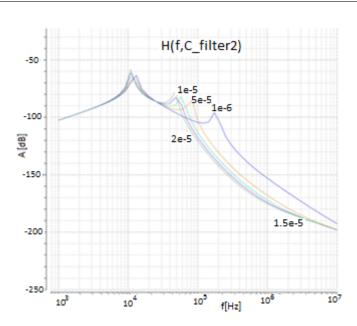

|   |      | 5.2.2 EMI Filter Design                                                           | 53  |

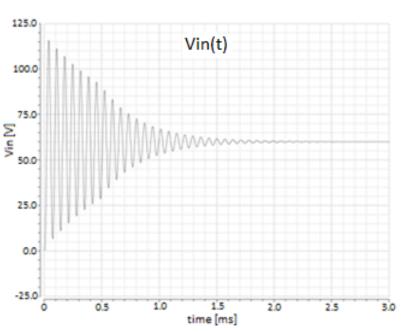

|   |      | 5.2.3 Filter Effects on the Converter System                                      | 58  |

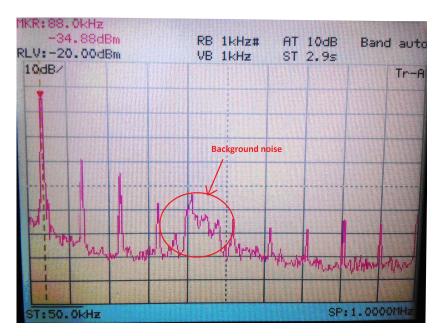

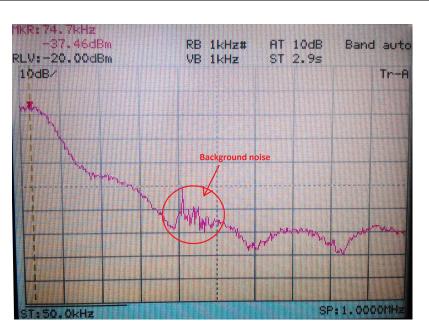

|   |      | Experimental Measurements of Conducted Electromagnetic Emissions .                | 62  |

|   |      | Effects of SKIP Algorithm on the Conducted EMI                                    | 63  |

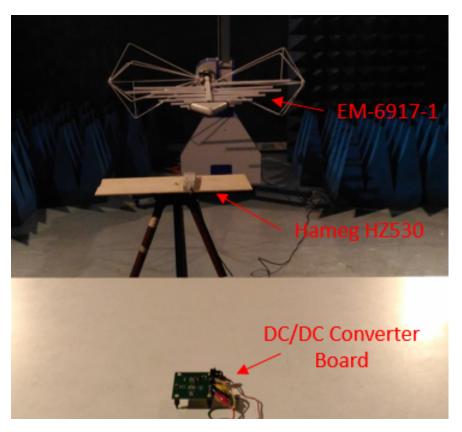

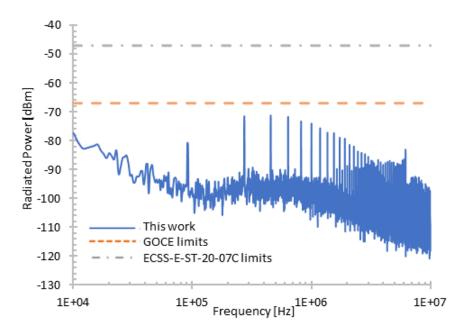

|   | 5.5  | Measurements of Radiated Interference                                             | 65  |

|   |      | 5.5.1 EMC Standard Test                                                           | 68  |

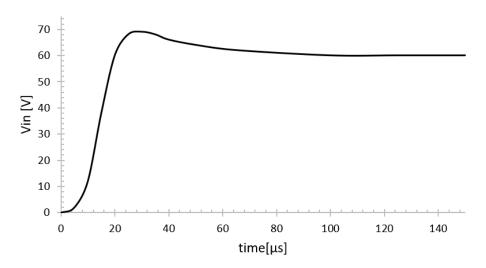

|   |      | Soft-Start Techniques to Reduce Peak Currents                                     | 68  |

|   | 5.7  | Electromagnetic Interface Comparison to State-of-the-art                          | 69  |

| 6 | TID  | and SEU Mitigation Techniques                                                     | 72  |

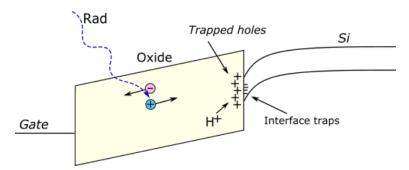

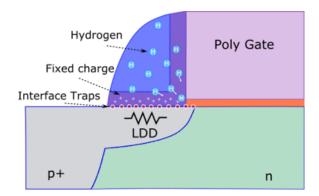

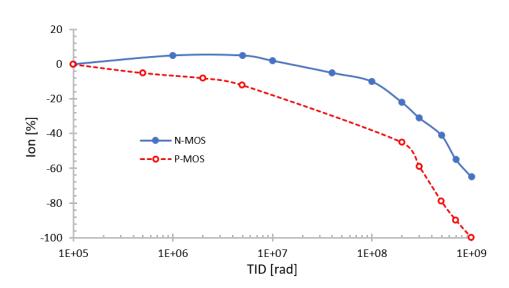

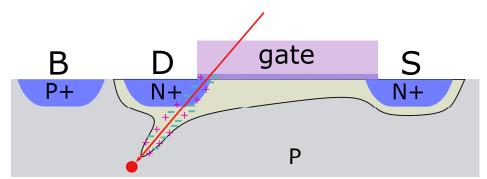

|   | 6.1  | Total Ionizing Dose Effects                                                       | 73  |

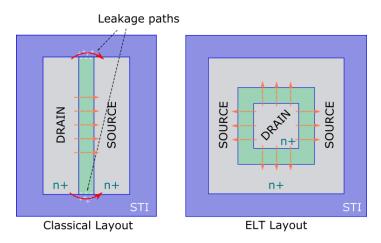

|   | 6.2  | IC techniques to face TID effects                                                 | 74  |

|   |      | 6.2.1 Enclosed Layout Transistors                                                 | 75  |

|   |      | 6.2.2 Minimum Length                                                              | 75  |

|   |      | 6.2.3 CMOS vs. CML approach                                                       | 76  |

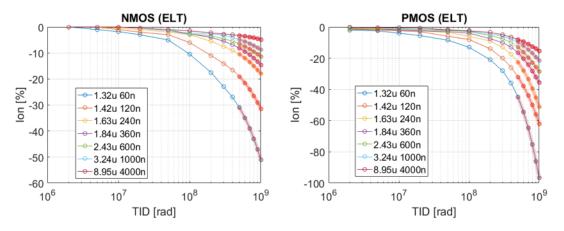

|   |      | 6.2.4 1 Grad (SiO <sub>2</sub> ) MOSFET models development $\ldots \ldots \ldots$ | 78  |

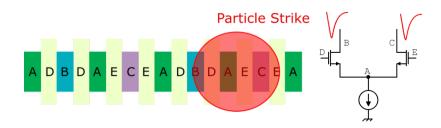

|   |      | Single Event Effects                                                              | 80  |

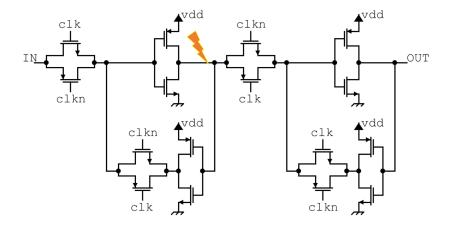

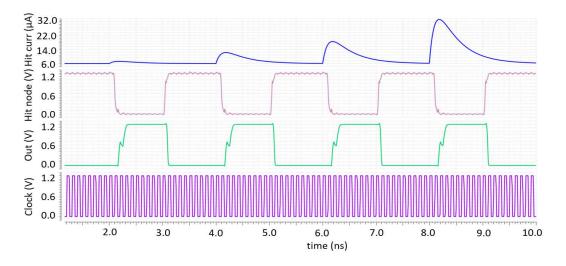

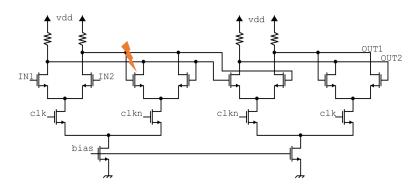

|   | 6.4  | IC techniques to face SEE effects                                                 | 81  |

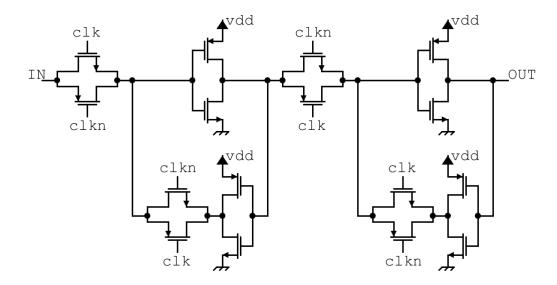

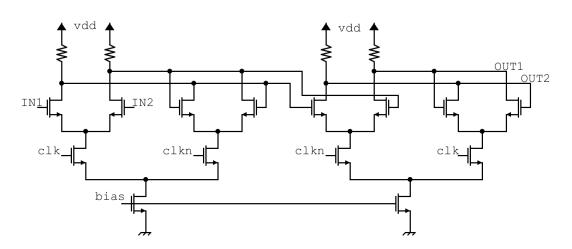

|   |      | 6.4.1 CMOS-DFF and CML-DFF SEE Comparison                                         | 82  |

| 7 | High | n-speed Electro-Optical Modulator Drivers Design                                  | 87  |

|   | 7.1  | MZM and RR                                                                        | 87  |

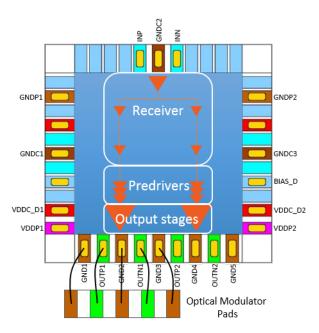

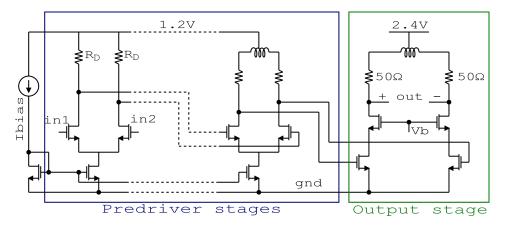

|   | 7.2  | Drivers Design                                                                    | 89  |

|   |      | 7.2.1 Output stages design                                                        | 90  |

|   |      | 7.2.2 Pre-driver stages design                                                    | 91  |

|   |      | 7.2.3 Receiver                                                                    | 92  |

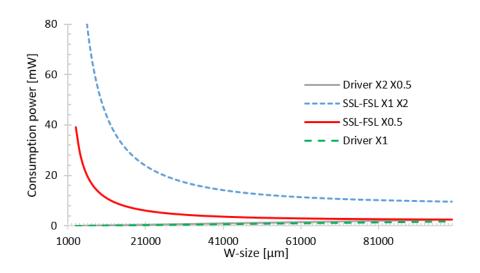

|   |      | 7.2.4 Power Consumption and Power Supply Rejection Ratio                          | 92  |

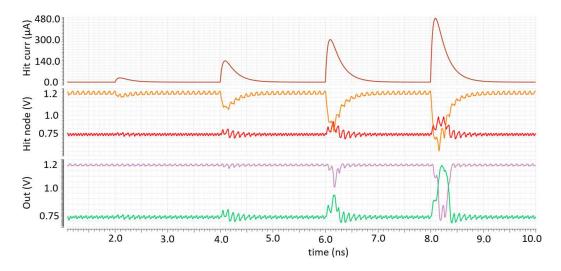

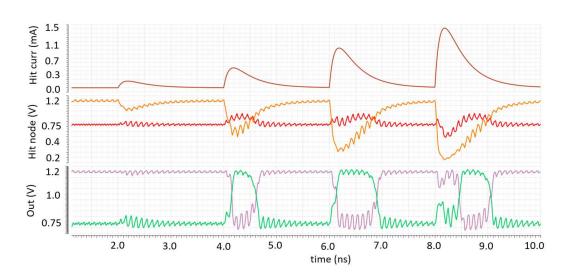

|   |      | 7.2.5 SEE Simulations                                                             | 93  |

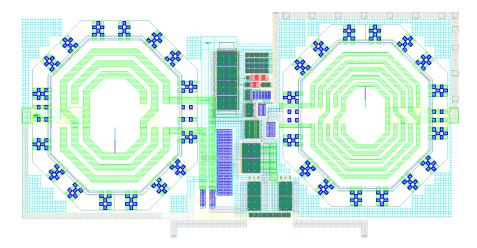

|   |      | 7.2.6 Chip Layout                                                                 | 94  |

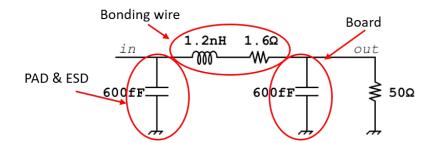

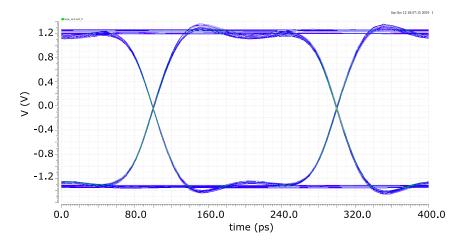

|   |      | Chip-Board Co-Simulations                                                         | 95  |

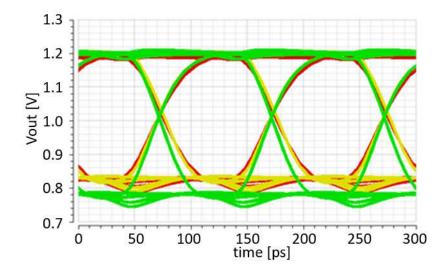

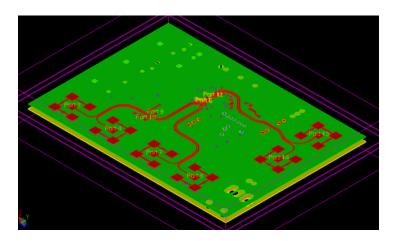

|   | 7.4  | Drivers Measurements                                                              | 97  |

|   |      | 7.4.1 Frequency Domain Measurements                                               | 97  |

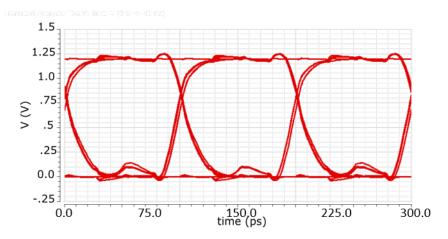

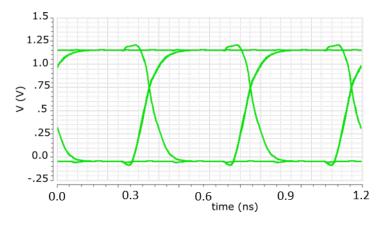

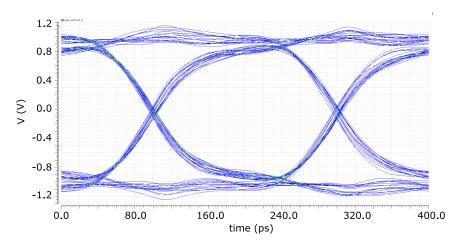

|   |      | 7.4.2 Time Domain measurements                                                    | 98  |

|   |      |                                                                                   | 102 |

|   | 7.5  | State-of-the-art Comparison                                                       | 106 |

Contents

| 8   | Conclusions | 107 |

|-----|-------------|-----|

| Bik | bliography  | 110 |

# CHAPTER 1

# Introduction

## **1.1** Open Challenges on ICs Operating in Harsh Environments

In the last fifty years, electronics have pervaded every aspect of our lives. Its uncontrollable diffusion has involved every space of our daily life. From smartphones to smartwatches, from smart-televisions to smart-kitchens, from electric-bikes to electricskateboards, every device around our life is or could be equipped with some electronic "intelligence". Consumer electronics has been, unquestionably, one of the most flourishing markets of the last years. But electronics is also making inroads in harsh environments: those environments that with their rugged characteristics, could reduce the lifetime of electronic devices. While many devices on the market are not designed for harsh environments, many others must operate effectively while being jostled, dampened, heated, irradiated, and more.

A lot of rugged conditions could be considered harsh for human life, but what environments should be labeled "harsh" for electronic Integrated Circuits (ICs) systems? These environments can be identified for the nature of the rugged physics phenomenons at which they are exposed:

• *Chemical Attack*: the materials used in the manufacture of ICs, such as silicon for dies, plastic or ceramic compounds for packages and metals for electrical connections, can be attacked by special chemicals in form of gaseous vapor and liquid. A classic example is the vulnerability of the wide diffused plastic packages to moisture. Indeed, thanks to the porosity of plastic mold, it can easily diffuse into the package, where, in case of temperature excursion, it can create delaminations, crack and popcorn effects (so-called for its classic 'pop' sound). These unwanted effects could directly damage the package leadframe or create wide access used by corrosive chemical elements to damage the internal die. For this reason, the ICs

are sold in moisture-proof packs and, if they are stored for an important period, they should be treated with decontamination processes [1]. Even more aggressive are the exhausts fume of combustion engines or the corrosive fume of lead-acid batteries that ICs devices have to face when operating in automotive environments.

- Mechanical Stresses and Vibration: even mechanical stress could seriously damage ICs. Being the ICs micro-systems composed of different materials, as a consequence of temperature or pressure changing, several stresses can appear. The bonding wires or solder bumps, used to connect the ICs to the outside world, are extremely sensitive to stress, which can reduce their conductive property and even break them under fatigue. Indeed, 32.3% of the failure of the ICs encapsulation is due to bonding faults and 15.5% to die cracking [2, 3]. The MEMSs (Micro Electron-Mechanical Systems), typically used as sensors for the revelation of accelerations, pressures, and angles, are especially sensitive to vibration and can experience damage under strong vibration and impact stresses.

- Electromagnetic Disturbs: since the advent of electronics, the main trend, towards the development of new technologies, has been the ever-more increasing integration. It started with the integration of as many transistors as possible on the same chip and it is followed with the integration of as many heterogeneous systems as possible in the smallest area. Complex systems integrated into an incredibly small area influence each other, creating unwanted system behaviors. The main physical interactions, between these systems, are due to electromagnetic fields, whose confinement in a limited area is extremely challenging. Therefore, this ever-increasing integration leads ICs to have to work surrounded by strong variable electromagnetic fields, which can induce voltage variations in some nodes of electrical circuits, altering the system functionality or disturbing the radio communication between transceivers. In order to limits these heavy disturbs, the European Community has released the CISPR standard [4]. It imposes strict limits on the maximum conducted and radiated interference emissions of each device, diversifying the limits value for residential, industrial, automotive, research and lightning environments. The difficulty to confine the electromagnetic disturbs and the strong requirements imposed by CISPR laws pave the way to new design techniques that go beyond the electrical ICs design. Some of these techniques are analyzed in this thesis in Chapter 5.

- High-Temperature Environments: since ICs are manufactured using high-energy processes, they are also susceptible to high-energy. Indeed, running an IC at high junction temperatures will degrade its working life. The rapid thermal changes, as previously reported, are also the main responsible for mechanical stress generation and its negative consequences. The temperature range, in which the IC device has to work, is one of the classical discriminators between consumer devices and ICs designed for harsh environments. Indeed, today's de facto temperature range for consumer standard is from 0 °C to 70 °C while the industrial standard constraint is from -40 °C to 125 °C, making challenging the ICs design [5].

- *Radiation and Ions Exposition*: radiation exposure and ions interactions heavily affect the ICs performance when they are in sufficient quantity and with enough

energy to interact with the silicon material. These interactions can reduce the performance of analog circuits and cause data loss in digital systems. The continuous exploration of new planets and deep space poses new challenges in radiation hardness electronics. Indeed, the Total Ionizing Dose (TID) level required in the space missions has increased from a few hundred krad to 1 Mrad in the last few years [6]. Radiation levels are even more demanding in the field of physics experiments, where the discoveries of new properties of matter require the use of ever-greater energies. The same discoveries and technologies carried out in physics experiments are then applied in medical physics, paving the way for new illness treatments. Therefore, the growing demand for higher radiation hardness levels opens the research for new techniques for radiation-tolerant systems, some of which are discussed in Chapter 6.

The design of ICs is incredibly demanding for the nature of the interaction between harsh conditions and the electrical world. Most workbenches are temperature controlled, static-free, dry and radiation-proof areas, but the real world is not as forgiving. It is filled with harsh conditions that make challenging the proper operation of ICs. Depending on the harsh application, the ICs designer has to address one or more of the previous rugged characteristics.

## 1.2 Thesis structure

In this thesis work, some techniques to improve the performances of ICs operating in harsh environments are developed. In particular, these techniques aim to increase the hardness and reliability of ICs operating in the automotive, aerospace and HEP (High Energy Physics) environments. In Chapter 2 the main challenges in today's Automotive, Space and HEP environments are reported, focusing on the effort paid by the research to address them.

In response to today's challenges, introduced in Chapter 2, Chapter 3 deals with the design of an inductorless DC/DC converter compliant with the automotive world, focusing on the development of high and low voltage compatibility techniques and their fault-tolerant solutions. This IC device and its implemented techniques are then experimentally verified with an accurate measurement campaign, reported in Chapter 4, with electrical and thermal results. Considering the strategic importance of the electromagnetic compatibility and its role in the interaction between ever-more integrate systems, the techniques developed to keep under control the electromagnetic emission end their verification are reported in the dedicated Chapter 5.

The continuous research of new physics theories requires extremely challenging verification experiments, which put under intensive stress today's state-of-the-art technologies, as reported in Chapter 2. In this framework, in Chapter 6 some ICs design techniques for enabling silicon technology to work in an extremely irradiated environment are analyzed. These techniques are then used in the design of the first 800 Mrad tolerant chip, whose design and tests are reported in Chapter 7. The conclusions on the developed techniques to sustain the functionality and the reliability of ICs operating in such hostile conditions are drawn in Chapter 8.

# CHAPTER 2

# IC Design Challenge in Automotive, Aerospace and HEP Environments

## 2.1 Automotive

Today, the automotive industry is a fast-growing market no longer driven by mechanical or hydraulic onboard systems improvements, but by the development of new safety and infotainment functions integrated into a vehicle. A quote from Daimler-Chrysler executives says that more than 80% of innovation in the automotive domain concerns electronic components [7]. In the last fifty years, the number of electronic devices and control units in the automotive environment has steadily increased, and today, hundreds of different ECUs can be found in a modern vehicle, each one specialized to provide a different task [8,9]. This has led to the need to develop automotive-specific ICs, which have to operate in one of the harshest environments, being characterized by corrosive chemical species, strong vibrations, heavy electromagnetic disturbs and wide temperature swings, which have already been summarized in the Chapter 1. The pervasive diffusion of electronics in vehicles is confirmed by the 2020 market forecasts, where the 50% of the vehicle cost is estimated to be due to electronic devices [10]. According to current European regulations, since 2015, a target CO<sub>2</sub> emission of 130 g/km is required to carmakers. This threshold is even decreased to 95 g/km by 2020 [11]. Which corresponds to fuel consumption of around 4.1 l/100 km of petrol or 3.6 l/100 km of diesel. If the average  $CO_2$  emissions of a manufacturer's fleet exceed its target in a given year, the manufacturer has to pay an excess emissions premium for each car registered. Therefore, an increased level of electrification in cars, towards fully electric vehicles (EVs), is needed to meet strict pollution limits.

In hybrid and electric vehicles, micro/mild power applications have appeared, like startand-stop, regenerative braking and torque assist. These systems repeatedly stress the onboard electrical systems with load dumps and transients each time that they are activated. For instance, the start-and-stop system, implemented in engine vehicles to increase gas mileage, shutting the engine off at stop signs and then restarting it, within a fraction of a second when the driver steps on the gas pedal, strong stresses the vehicle power bus in stop-and-go traffic. Therefore, even if, in principle, the vehicle is battery powered and thus has a stable and quiet DC source, the reality is quite different. The basic DC rail of the car is noisy, with large and sudden drops when starting the car (cold-cranking) which can drop the rail to a few voltages. At the other extreme, the rail can spike when loads are suddenly removed (called "load dump") causing transients as high as 60 V.

In response to the ever-higher electrical power needed onboard of vehicles for the supply of the growing electrical systems and the ever-lower vehicle weight for fuel-saving, the automotive systems are migrating toward the 48 V DC power bus standard. After the first revolution of the automotive electrical bus, in 1965, when the power net doubled from 6 V to 12 V [12], today, the voltage level is further increasing from 12 V up to 48 V [13–15], to achieve the onboard power increment of factor four with equal current levels. For instance, the start-and-stop system, already used in 12 V vehicles, requires a power level up to 2 kW, which corresponds to 166 A and 90 mm<sup>2</sup> cable area. Using a 48 V DC power bus the current level is reduced to 41.5 A and the cable area is reduced to 25 mm<sup>2</sup>. Therefore, the weight, space occupation, and cost of the onboard wiring system is reduced moving from 12 V to 48 V DC power bus [16, 17]. At the state-of-art, the progression towards the 48 V is characterized by the coexistence of the two voltage domains. Indeed, the major automobile manufacturers including BMW, Daimler, and VW are implementing a two voltage level network standard, inside the same vehicle [13]. Low power loads such as sensors, memories, processors, analog front-ends (requiring regulated voltages of few Volt, and current levels of few hundreds of mA) are typically supplied starting from the main 48 V power source after many conversion steps, each implemented using discrete and inductor-based DC/DC converters. For example, a first 48 V to 12 V unit is followed by another 12 V to 5 V unit, and finally, a dedicated point-of-load linear converter is used for each of the regulated voltages. Such an approach leads to cumbersome and costly conversion systems. On the contrary, an integrated solution could ensure reduced size and weight, and low cost in large volume markets.

Since the electronics on vehicles are widely used to control safety-critical systems, like braking and steering systems (e.g. X-by-wire systems), their devices have to guarantee the highest quality level and a "zero defect" rate during all the lifetime of those safety-related systems. The fault-tolerant protections have to be integrated into each device. These are typically provided with triple redundancy, spatial or temporal, or with error detection ed correction code in case of data transmissions [18]. For DC/DC switching converter, the fault-tolerant characteristic is guaranteed by the use of galvanic coupling in transformers. In the optic of all integrated DC/DC converter in a single IC, the use of these elements should be avoided, for their difficult integration property. It is for this reason that in Chapter 3 an innovative insulation solution is proposed as technique to make DC/DC converters fault-tolerant.

The ever increasing demand for new functions in a vehicle is making the space-saving a fundamental constraint for the design of future applications. In this direction, the elec-

#### Chapter 2. IC Design Challenge in Automotive, Aerospace and HEP Environments

tronic components are ever-more placed one side-to-side to the other, leading to electromagnetic compatibility problems. One of the most common and most electromagnetic noisy devices is the DC/DC switching converter. These converters are distributed in all the vehicles to efficiently provide the supply voltage to all the electric systems, starting from the main power bus (e.g. 12 V, 36 V, 48 V). Since their onboard extensive use and their generation of electromagnetic noise, the design of these DC/DC converters continues to be one of the challenges of today's electronics [19–22]. For these reasons some techniques for electromagnetic noise mitigation, in DC/DC integrated converters, are proposed in Chapter 5.

The ever-pressing request for integration is leading to new challenging technology solutions. The design of ICs, which is by its nature a planar technology, is evolving in a three-dimensional solution [23]. One of the most feasible 3D solutions is the stacking of more ICs one on the other, using interposer layers, as insulating layers, and Through Silicon Vias (TSV), as electrical conducting elements.

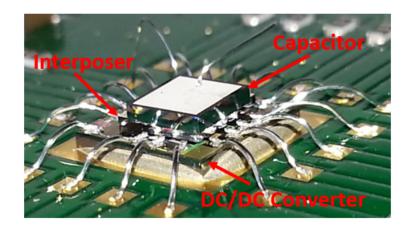

In this framework was born the ATHENIS3D FP7 EU project (Automotive Tested High-voltage and Embedded Non-volatile Integrated SoC platform with 3D technology) that partially founded this thesis work. It aims at providing new enabling technologies for high-voltage and high-temperature applications, tested for power systems of new hybrid/electrical vehicles. Innovation is exploited at the process/device level (3D chip stacking, wafer-level packaging, trench capacitors integrated into the interposer) and circuit-level (inductorless high-voltage DC-DC converter, high-temperature System-on-Chip platform) [24].

To this aim, this thesis work presents, in Chapters 3 and 4 the design, implementation and experimental characterization results of an inductorless DC/DC converter and the techniques implemented to address wide voltage conversion range.

## 2.2 Aerospace

Aerospace is a flourishing moving industry comprising aeronautics and astronautics. In just five decades from the Apollo 11 mission, which first landed humans on the moon, the space economy has grown from a handful of nations to over 60 nations active in space-related activities worldwide and the trend is still growing. The growing space market value is confirmed by the recently born notion of Space 4.0. Analogous to Industry 4.0, which is the collective term for transformations across automation and data exchange in manufacturing technologies and processes, Space 4.0 focus is on interconnecting science, industry, politics and society in new ways [25, 26]. In the Space 4.0, space is evolving from being the preserve of few nations governments to a situation in which there is a continuous increase in space partners, including industry, participation with universities and private companies, in digitization and global interaction. The growing variety of services, required by the increasing number of space actors, creates challenges in the satellite and space vehicles design. Current trends in satellites show a rapid increase in data traffic and digital processing. The throughput of nextgeneration digital telecommunications satellites will exceed terabits per second of data, which have to be processed on board. For instance, the high-resolution cameras and synthetic aperture radars need high-speed communications between the instruments and storage [27]. Optical technology, thanks to its high bandwidth-length product, the lightweight cabling, and electromagnetic hardness, can potentially be the solution for data-rate increment in the satellite. In this direction, the European Space Agency (ESA) has recently released the new SpaceFibre standard for onboard satellite communication up to 6.25 Gbps [28]. Hence, new electro-optical space compliant circuits have to be designed to meet the growing speed demand.

Analogous to the automotive sector, described in the previous section, the satellites are space-hungry systems, where the ever-higher integration of heterogeneous functions creates electromagnetic interaction demanding issues. The electric energy generated by the solar cells array feeds the Power Conditioning and Distribution Unit, which is composed of several modules (regulator, protection devices, battery regulators, power distribution for equipment/propulsion, etc.) devoted to electric power management. Then the power is sent to different functional units using power bus with fixed voltages, typically between 28 V and 50 V. Finally, DC/DC converters inside each functional unit are used to obtain the desired voltage level (e.g., 5 V, 3.3 V, 1.65 V) to feed specific circuit modules. The switching activity of inductor-based DC/DC converters generates EMI (ElectroMagnetic Interference) emission that potentially poses a threat to the correct operation of sensitive electronic equipment [29, 30]. Since the fundamental role that EMI has on the onboard satellite devices, techniques to mitigate EMI generation should be adopted, as shown in Chapter 5.

In terms of space exploration, today's debate has been dominated by future human space travel. Should it be toward the Moon or Mars? Since 2005, there has been a trend in favor of the Moon, although plans for future Moon and Mars missions have been designed simultaneously. Indeed, NASA has expressed its intention to land American astronauts on the Moon by 2024 [31]. ESA chief Jan Worner with the idea of the 'Moon Village' makes the Moon the next goal of international collaboration in space exploration [32]. Even private companies like Blue Origin and SpaceX are focusing on making lunar exploration an economic opportunity [33]. The Moon choice is probably driven by the lower harsh conditions and cost that the missions should address concerning the Mars target. Indeed, one of the biggest challenges of solar system exploration is the variety of extreme environments that astronauts, satellites, and probes must encounter and survive. For example, exploration of the Venus surface requires systems and instruments that can withstand intense heat (480 °C) and pressure (92 bar). In these severe conditions, where the reliability of the silicon technology is questioned, one of the most promising solution able to operate in this environment is the new high-gap 4H-SiC JFET integrated technology. Recent studies on this technology have demonstrated the feasibility of a ring resonator able to withstand 460 °C at 93 bar for 60 days [34] and the promising performance of a highly sensitive high-temperature sensor operating at temperature up to 460 °C and more [35].

Instead, a spacecraft on Jupiter must be designed to handle an extremely harsh radiation environment. Indeed, the currently most radiated mission was NASA's Europa Clipper mission, which aimed to send a spacecraft into orbit around Jupiter to perform forty-five repeated close science flybys of the icy moon, Europa. The goal was to produce high-resolution images of Europa's surface and determine its composition. The space-craft was expected to withstand a total ionizing dose of 2.7 Mrad(Si), throughout the mission. It was designed with 12.7 mm aluminum walls to house most of the spacecraft and payload reducing to 150 krad(Si) the TID inside shields. Therefore, the electronic

#### Chapter 2. IC Design Challenge in Automotive, Aerospace and HEP Environments

devices were designed with a Radiation Design Factor (RDF) of two, to be compliant to 300 krad(Si) at the part location [36, 37]. If the electronic devices of the next spacecrafts overcome the technical radiation-tolerant challenge lower shields thickness and weigh could be used, reducing the enormous spacecraft launch cost and enabling the exploration of new cosmic spaces characterized by high-radiation levels.

In the optic of design radiation hard electronic devices, one of the most challenging terrestrial applications is made by high-energy experiments of particle physics, which require devices able to withstand even much higher radiation levels than current space missions.

## 2.3 High Energy Physics

Particle physics is the branch of physics that studies the basic constituents of matter and their interactions. Its research focuses on subatomic particles, including electrons, protons, neutrons, photons, neutrinos, and muons. Since many elementary particles rarely appear and fast decay under normal circumstances in nature, to allow their study, they are generated and detected by high-energy collisions of other particles in particle accelerators. Particle physics aims to investigate the fundamentals of matter in order to address unanswered key questions about the nature and origin of the Universe and to find the final general theoretical model, which overcome the issue related to the discrepancies between the theory of general relativity and the quantum mechanical. The main instruments for High Energy Physics are particle accelerators, which employ electric and magnetic fields to accelerate and focus particle beam again a fixed target or another particle beam. The high-energy particle interaction generates new particles and events that are detected and studied. The CERN (European Organization for Nuclear Research), located near Geneva, Switzerland, is equipped with the LHC (Large Hadron Collider) that is, currently, the world's most energetic accelerator. The particle detectors, inside the LHC, are made by different layers of sub-detectors. The innermost layer (the nearest to the interaction point) is the tracking device, that aims to reveal the paths of electrically charged particles through the trails they leave behind, instead, the calorimeters, placed in the outer layers, have the task to measure the energy lost by particles that go through them. The detector includes magnetic fields that bend the path of charged particles in a way that it is possible to calculate the particle momentum which helps in identifying the particle type. The information about particles is extracted by the combination of charge detected by sensors and its trajectory inside the detectors layer. When a particle passes through sensors (i.e. complex silicon diode structure) release energy-generating charge. This charge is collected by the front-end electronics, which properly condition the information signals, performing amplification, shaping, buffering, analog to digital conversion, and then the information is transmitted to remote data acquisition systems for data analysis and storage. The most recent significantly LHC discovery is the decay of one Higgs boson into four leptons or two photons that led to the discovery of the Higgs boson, also called the "God Particle", in 2012, which validated the Standard Model [38]. The probability of generating one of these interesting events in the interactions of two beams is extremely rare and is proportional to the luminosity of the collider. It corresponds to the number of particles per second in one beam multiplied by the number of collisions per unit area in the other beam at the crossing point. To increase the probability to detect physically interesting events, the

CERN's roadmap forecast an increasing luminosity of the LHC up to 5e-34 cm<sup>-2</sup>s<sup>-1</sup> in the High Luminosity LHC (HL-LHC), foreseen by 2025 [39, 40]. For example, the extremely rare generation of two Higgs bosons and their decay into two pairs of photons has a probability of one event every 21.4 months, considering the LHC luminosity in 2012. This probability will be reduced to 2.5 months in the next HL-LHC scenario. The increase of power in future accelerators experiments requires the re-design of the detector front-end electronics to face high data rates and high radiation levels, e.g. up to 5 Gbps for a module including 4 pixel-detector CHIPIX65 readout ICs, each up to 1.2 Gbps [41], and a TID in the range from 800 Mrad to 1 Grad (SiO2) in the inner layers of the Silicon Trackers. This value is three order of magnitude higher than highspeed rad-hard link designed at the state-of-the-art, such as the Versatile link in [42] having roughly the same speed of 4.8 Gbps but with a radiation hardness of 500 kGy (i.e. 50 Mrad (SiO2), being 1 Gy = 100 rad). To be noticed that concerning today's most radiation-hard spacecraft, see Section 2.2, the TID level required in the HL-LHC is more than three thousand times higher, creating extreme challenges in electronic design. To the best of the author's knowledge, today in literature, there are not electronic systems able to operate at 1 Grad TID and there are only a few data of single transistors measurements at such high TID. The 65 nm CMOS technology seems to be the promising technology for these TID levels, therefore in this thesis, in Chapter 6 the main effects that such extreme radiation level generates on this technology are highlights. In response to these effects, some radiation-hard techniques are proposed and verified in the drivers design discussed in Chapter 7.

# CHAPTER 3

# High-Voltage and Fault Mitigation Design Techniques

The state-of-the-art conversion from nominal 48 V to low output voltages with a few hundred mA load requirements is dominated by inductor-based DC/DC switching converters [15, 17]. They provide high power efficiency conversion, but, on the other hand, are cumbersome and difficult to be integrated into embedded systems. Linear regulators are typically used only in very low power systems since they have a low power efficiency that depends on the Vout/Vin ratio [43]. When the power source provides up to 60 V, and the required output regulated voltages amount to a few voltages, then the power efficiency of linear regulator amounts to a few per-cent points. Integrated solutions can be achieved by relying on SC (Switched Capacitor) DC/DC converters. They have been proposed in literature mainly for low-voltage inputs, e.g. step-down regulation of Li-ions battery input voltages (below 5 V) to low-voltage and low-power loads in consumer devices (e.g. smartphone) [44-48] or as step-up converters for nonvolatile memories and energy harvesting [49, 50]. To overcome the state-of-the-art limits this chapter presents the techniques used to manage a wide voltage range from 6 V to 60 V in an inductorless switching DC/DC converter design framework. In addition, in response to strong requirements of fault-prevention, fault-detection and faultmanagement of safety-critical systems, an innovative and integrable fault-tolerant technique is proposed, avoiding the state-of-the-art use of cumbersome transformers [51].

## 3.1 Switched Capacitor Converters

Despite the evolution of integrated technology has made enormous progress, going to use special materials with ferromagnetic properties and moving from two-dimensional solutions to three-dimensional ones. The realization of integrated inductors with good features still presents great obstacles [52,53]. This difficult integration of inductors and transformers in silicon technology and the growing need for ever-higher integration, drive the converter architecture choice towards the SC converter topology. The SC DC/DC converters are characterized by the repetitive change in the circuit structure, and by using only capacitors, as energy storage elements, which are more suitable for a complete converter integration.

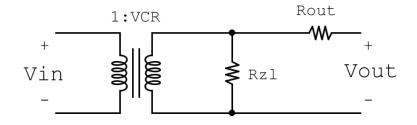

Two types of capacitive elements are used in SC DC/DC converters: flying capacitors, used to transfer the charge from input to output ports, and buffer capacitors, which stores the charge at the output port and mainly influence the steady-state ripple characteristics and the wake-up phase of the converter [54, 55]. SC converters, in stationary conditions, can be modeled as in Fig. 3.1, which includes:

- an equivalent ideal transformer with a turn ratio VCR (Voltage Conversion Ratio).

- an equivalent output resistor R<sub>OUT</sub> representing all converter losses proportional to the load current.

- an equivalent parallel resistor  $R_{ZL}$  representing the losses in the zero-load current condition.

The  $R_{ZL}$  value depends on the power wasted by switches drivers and by auxiliary systems, such as the oscillator or the control system. The effect of the  $R_{ZL}$  is typically negligible compared to the  $R_{OUT}$  losses [47]. The value of  $R_{OUT}$  depends on the switching frequency, on the values of the capacitors and that of the switches ON-resistance. Instead, the VCR value depends on the selected circuit topology. According to Eq. 3.1 when a load is applied to the converter an output voltage drop is observed, due to the output resistor  $R_{OUT}$ .

Figure 3.1: SC converter equivalent model.

$$V_{out} = VCR \cdot V_{in} - R_{OUT} \cdot I_{load} \tag{3.1}$$

As already highlighted, the strength of SC converters is their suitability for monolithic integration, as they only require native components for an integrated circuit technology: capacitors and switches. On the other hand, a lossless conversion can only be achieved by using an infinitely large amount of capacitance and ideal switches with zero ON-resistance, making  $R_{OUT}$  in Eq. 3.1 negligible. In addition, while inductive DC/DC converters can implement a continuous voltage conversion ratio by using PWM (Pulse Width Modulation) technique, in SC converters the VCR is mainly determined by its topology, consisting of two or more specific configurations that are time alternated in a two-phase (or more phases) operation scheme. Therefore, only discrete

#### Chapter 3. High-Voltage and Fault Mitigation Design Techniques

VCR values can be achieved in SC converters. The greater is the VCRs number used for the conversion, the smaller is the voltage oscillation step around the target voltage value. The Makowski and Maksimovic's theorem [54] explains the maximum number of VCRs that is possible to obtain in a network, as a function of the fly capacitors number:

"The realizable conversion ratio of a two-phase switched-capacitor dc-dc converter with a single dc voltage source, is given by a common fraction in the form:

$$M_i(k) = \frac{P[k]}{Q[k]}$$

Where P[k] and Q[k] are integers that satisfy:

Max[Abs(P[k]), Abs(Q[k])] < F[k]

Min[Abs(P[k]), Abs(Q[k])] > 1

k is the total number of capacitors, and F[k] is the k-th Fibonacci number. The minimum number of switches to have all possible VCRs is equal to 3k+2."

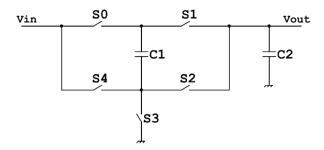

Since this theorem, it is possible to predict that using only one fly capacitor and a buffer capacitor, in an SC DC/DC converter circuit, the available VCRs are 1/2, 1 and 2, and a minimum number of five switches has to be used. While using two fly capacitors and a buffer capacitor the VCRs number increases to seven (1/3, 1/2, 2/3, 3/2, 1, 2, 3) and the minimum switches number grows to eight. In addition to the implementation of discrete VCRs, in order to achieve finer control of the output voltage, other control techniques can be realized, such as frequency sweep, PWM, switches ON-resistance control, SKIP [54]. The common denominator of these further techniques is their inefficiency action modality, indeed they regulate the converter output voltage changing the  $R_{OUT}$  of the model in Fig. 3.1. This, on a side, allows getting a fine control, but on the other side decreases the converter efficiency, exactly in the same way performed by linear converters.

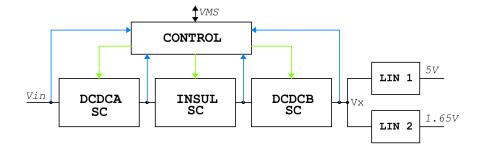

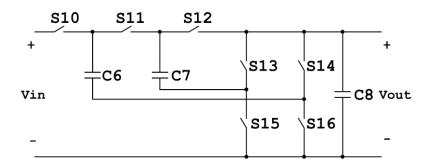

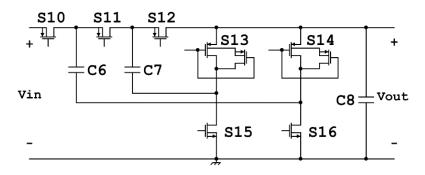

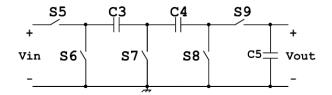

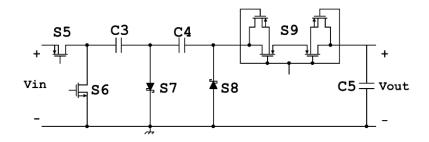

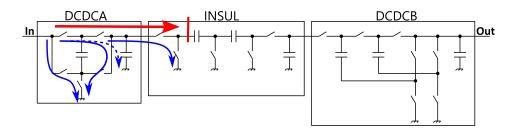

## 3.2 Converter Architecture

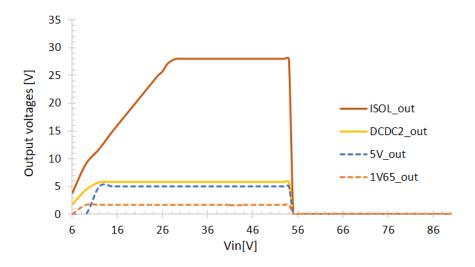

Following the above-described design principles of the SC DC/DC converters, and the consideration in Chapter 2, an SC DC/DC converter was designed in 0.35  $\mu$ m HV-CMOS AMS technology. As a case study, the DC/DC converter should regulate a wide input voltage range to two output points of load, 5 V and 1.65 V, for sensors and ECUs supply with power up to 2 W. In addition, it should ensure input-output insulation from input overvoltages or control strategy faults. In order to withstand the application requirements, the multistage converter in Fig. 3.2 is designed. The architecture is the cascade of three SC circuit stages and two linear regulators, whose aims are:

• regulating a wide input voltage range, from 6 V up to 60 V, to a value  $V_X$  of about 6 V.

- ensure high regulation performance from  $V_X$  to the two points of load, 5 V and 1.65 V.

- providing isolation between input and output for fault mitigation.

Figure 3.2: Converter architecture.

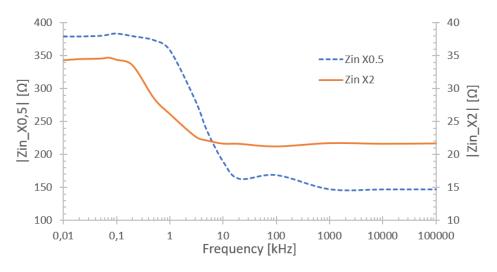

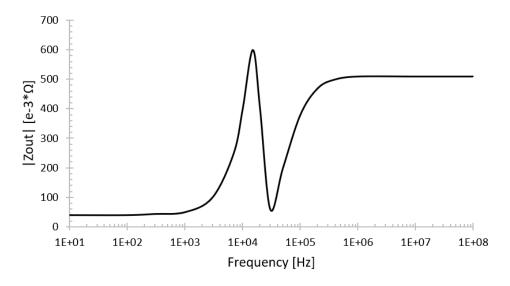

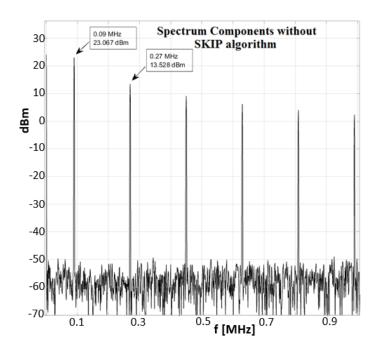

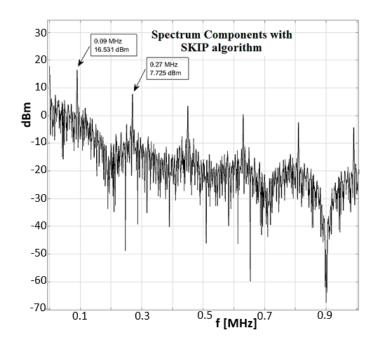

The use of a cascade of three SC stages allows distributing the wide input voltage on different voltage domains, making it easier for their management. The pre-regulated voltage, Vx in Fig. 3.2, is further regulated by two linear regulators, which work in parallel to achieve the two desired DC output values for ECUs and sensors supply. The linear regulators, in the last stage of the cascade, use a pass element to obtain the desired output voltage and an impedance modulation technique to achieve a low ripple level and good performance in terms of line/load regulation and PSRR (Power Supply Rejection Ratio). Since Vx is close to the target output voltages the linear converter efficiency, which depends on the ratio Vout/Vx still be acceptable. The control unit in Fig. 3.2 supervises the behavior of all stages, in all operating modes (waking phase, normal operation, under/over-voltage), and manages the VCRs selection taking into account the input voltage of each stage. In addition, it provides a communication interface for diagnostic and configuration towards an external host. The architecture, in Fig. 3.2, is scalable and parametric in terms of the number of SC stages in the cascade and of linear regulators working in parallel at the end of the cascade, adapting the converter to the application constraints. Indeed, together with the automotive world and satellites, displayed in Chapter 2, the number of applications moving towards 48 V power supply systems is growing rapidly: the networking and communication systems, today, use 48 V power buses to supply their devices [56] and the ETSI (European Telecom Standard Input) defines the 48 V level as the nominal voltage level but a wide range from 36 V to 60 V could be assumed by the bus [57].

With reference to Fig. 3.2:

- the first conversion stage (DCDCA) is a step-up/down converter designed to manage a wide input dynamic voltage.

- the insulator stage (INSUL) provides insulation between the input and the output ports of the system.

- the second conversion stage (DCDCB) reduces the output resistance of the SC converter part to ensure the correct operation of the point-of-load linear converters.

#### Chapter 3. High-Voltage and Fault Mitigation Design Techniques

• two linear regulators meet the nominal outputs (1.65 V with a load current from 0 to 50 mA, and 5 V with a load current from 0 to 400 mA) and ripple requirements.

Table 3.1, for each SC stage in Fig. 3.2, shows the implemented conversion ratios and the voltage range where they are applied. For example, in ideal condition, neglecting the converter losses, if a 48 V is applied at the designed converter the stage DCDCA will work as step-down (VCR = 1/2) generating 24 V output voltage. This voltage will not be altered by the insulator and will be the input of the DCDCB, which will divide it for a factor 3 generating a Vx of 8 V. Then the two linear converters will generate the target output voltages.

| Stage | Input Voltage [V]                                                                 | VCR | Output Voltage [V]               |

|-------|-----------------------------------------------------------------------------------|-----|----------------------------------|

|       | 6 <vin <15<="" td=""><td>2</td><td>12 <vout <30<="" td=""></vout></td></vin>      | 2   | 12 <vout <30<="" td=""></vout>   |

| DCDCA | 15 <vin <29<="" td=""><td>1</td><td>15 <vout <29<="" td=""></vout></td></vin>     | 1   | 15 <vout <29<="" td=""></vout>   |

|       | 19 <vin <60<="" td=""><td>1/2</td><td>14.5 <vout <30<="" td=""></vout></td></vin> | 1/2 | 14.5 <vout <30<="" td=""></vout> |

| INSUL | 12 <vin <30<="" td=""><td>1</td><td>12 <vout <30<="" td=""></vout></td></vin>     | 1   | 12 <vout <30<="" td=""></vout>   |

| DCDCB | 12 <vin <18<="" td=""><td>1/2</td><td>6 <vout <9<="" td=""></vout></td></vin>     | 1/2 | 6 <vout <9<="" td=""></vout>     |

| DCDCB | 18 <vin <30<="" td=""><td>1/3</td><td>6 <vout <10<="" td=""></vout></td></vin>    | 1/3 | 6 <vout <10<="" td=""></vout>    |

| LIN 1 | Vx >6                                                                             | -   | 5                                |

| LIN 2 | Vx >3                                                                             | -   | 1.65                             |

|       |                                                                                   |     |                                  |

**Table 3.1:** VCRs and input-output voltages of the three SC stages and of the two linear converters.

### 3.3 Circuit/Transistor-Level Converter Sizing

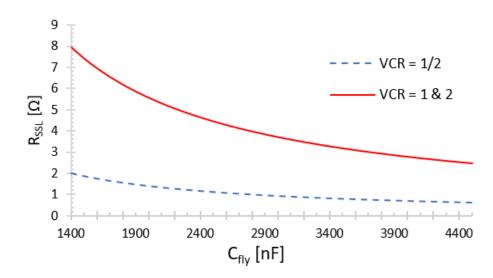

#### **3.3.1** Eqivalent Output Resistance of each SC stage

The design of each single SC circuit is performed following a top-down approach. The constraints of each stage were derived considering the maximum equivalent output resistance of the whole converter system that allows meeting the system requirements. Eq. 3.2 shows the maximum equivalent  $R_{OUT}$  of the SC sub-system that allows a correct functionality in these worst conditions:

- minimum input voltage  $Vin_{min} = 7 V;$

- maximum load current  $Iload_{max} = 300 \text{ mA};$

- minimum output of the 3 SC stages  $Vx_{min} = 5.3$  V. The value of  $Vx_{min}$  is obtained considering the 5 V output plus 0.3 V drop on the pass-transistor of the LIN regulators.

$$R_{OUT-max} = \frac{V_{in-min} - Vx_{min}}{I_{load-max}} = 5.67\Omega$$

(3.2)

With the selected  $R_{OUT-max}$ , if the DC/DC converter is used to supply higher currents than  $I_{load-max}$  used above, the correct convert functioning is guaranteed, but with higher input voltages than the target  $V_{in-min}$  level. Furthermore, if the input voltage

drops below 7 V, the converter continues to work providing lower current levels then  $I_{load-max}$ . For example, if the loads require 400 mA current, the minimum input voltage, to ensure the correct operation of the converter, is 7.57 V. Instead, if the input power bus drops to 6 V, the converter is able to provide currents below 125 mA.

The value in Eq. 3.2 is obtained considering a requirement of 5 V regulated output. For the 1.65 V output  $V_{x-min}$  is about 2 V, and with  $I_{load-max} = 50$  mA and  $V_{in-min} = 3$  V a less stringent  $R_{OUT-max}$  value of about 20  $\Omega$  is obtained.

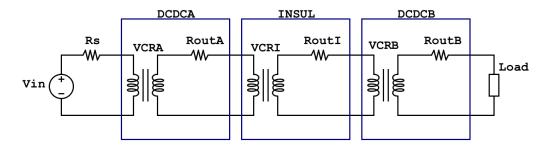

Considering the equivalent model in Fig. 3.1 for a generic SC converter, the system in Fig. 3.2 is modeled like in Fig. 3.3 neglecting the  $R_{ZL}$  resistors.

Figure 3.3: Converter equivalent circuit.

The overall equivalent output resistance is calculated as in Eq. 3.3. In the worst conversion condition, when  $V_{in-min}$  drops down to 6 V the DCDCA stage works in step-up mode (see Table 3.1) and the DCDCB stage performs a VCR = 1/2, then Eq. 3.4 can be derived.

$$R_{OUT} = \left[ \left( R_s \cdot VCR_A^2 + R_{OUTA} \right) \cdot VCR_I^2 + R_{OUTI} \right] \cdot VCR_B^2 + R_{OUTB}$$

(3.3)

$$R_{OUT-MAX} = \frac{4R_s + R_{OUTA} + R_{OUTI}}{4} + R_{OUTB} \approx \frac{R_{OUTA} + R_{OUTI}}{4} + R_{OUTB}$$

(3.4)

The use of a cascade approach, with a step-down converter as the last stage, relaxes the equivalent resistance of the other SC stages, being it multiplied for the VCR<sup>2</sup><sub>B</sub> of the last stage, whose value in the worst case is equal to 1/4, see Eq. 3.4. Table 3.2 shows the resistance values chosen for each stage after iterative simulations and taking into account the different MOSFETs used. Indeed, the use of a cascade architecture allowed using different high-voltage MOSFETs in the converter design, and the lower is the maximum voltage that they can sustain and the lower is their ON-resistance, reducing conversion losses and increasing the converter performance.

Table 3.2: Target output equivalent resistor of the 3 SC stages

|           | DCDCA          | INSUL         | DCDCB          |

|-----------|----------------|---------------|----------------|

| $R_{OUT}$ | $7.5 \ \Omega$ | $10 \ \Omega$ | $1.2 \ \Omega$ |

### 3.4 Switches typologies

The choice of the converter switches is a key element and depends on the maximum voltages required by the application. The use of N-MOSFETs is preferred for their lower ON-resistance compared to P-MOSFETs one (by a factor 2.5 due to higher mobility of electrons than holes, see Table 3.3). However, to avoid the use of charge pumps to turn on the transistors, N-MOSFETs are used only to replace the switches with the source connected to GND.

Table 3.3: N- and P-MOSFET characteristics in 0.35 µm HV technology.

|          | $ V_{DS} max [V]$ | Vthltyp [V] | $\mathbf{R}_{ON} \left[ \mathbf{k} \Omega \cdot \mu m \right]$ |

|----------|-------------------|-------------|----------------------------------------------------------------|

| P-MOSFET | 71                | 0.6         | 46                                                             |

| N-MOSFET | 55                | 0.4         | 21                                                             |

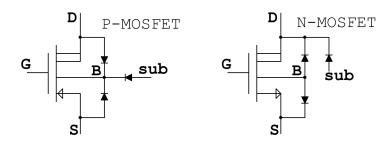

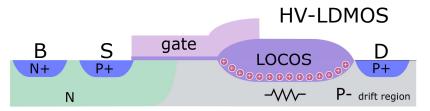

One of the main problems to design a circuit able to performs both step-up and step-down conversions (e.g. DCDCA stage) is the drain-source voltage polarity of its switch elements. Indeed, an incorrect polarization of pass elements leads to current injection in the substrate. Fig. 3.4 shows the electrical equivalent models of the N and P high-voltage MOSFETs (known in the literature as LDMOSFETs, Lateral Diffusion MOSFETs) in the 0.35  $\mu$ m AMS technology. When these transistors are used as power switches the following issues arise:

- For the N-MOSFET in Fig. 3.4, if the bulk is connected at its source and the drain voltage is lower than the source voltage the current flows in the bulk-drain parasitic diode. In this case, the switch may remain ON regardless of the gate voltage. Moreover, the substrate-drain diode can turn ON and injects charge in the substrate. For the N-MOSFET, the countermeasure used to mitigate this effect is decreasing the ON-resistance of the N-MOSFET, thus reducing the negative V<sub>DS</sub> on the MOSFET below the threshold voltage of the parasitic diode.

- For the P-MOSFET in Fig. 3.4, if its bulk is connected at the source of the MOS-FET, then in some phases it can have a lower potential than the drain. In this case, the current can flow inside the drain-bulk parasitic diode and it is not possible to turn OFF the MOSFET using the gate voltage. Furthermore, the parasitic vertical PNP BJT may inject current in the substrate. This BJT has good emitter efficiency because the drain has P-plus doping and the thin well creates a short base. This current injection, if not avoided, could have destructive effects. To mitigate this issue two new circuit topologies are proposed hereafter.

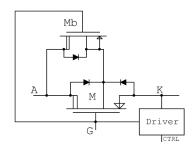

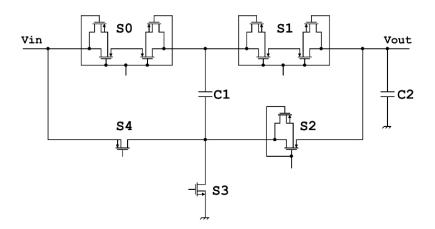

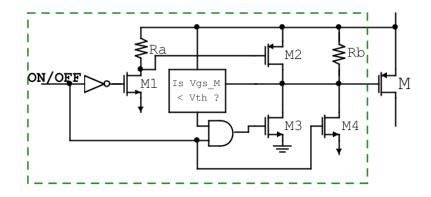

Fig. 3.5 shows the first topology used for the design of the switches. In this configuration, the Mb MOSFET connects the bulk of the pass MOSFET (M MOSFET) to his drain (node A) to bypass the drain-bulk parasitic diode. The driver unit is connected between the gate and the source (node K) of the M pass element to handle its  $V_{GS}$ . Therefore, when the driving signal is low (OFF) the gate is connected at the source of the MOSFET and this creates a diode configuration.

The proposed solution is different from known approaches in the literature, where the diode configuration is made connecting the gate with the drain and hence  $V_{GS}$  =

Figure 3.4: HV-PMOSFET and HV-NMOSFET equivalent circuits.

Figure 3.5: MOSFET switch in controlled diode topology.

$V_{DS}$ . However, for the used HV-MOSFET, which should sustain  $V_{DS}$  values up to 70 V, this conventional solution cannot be adopted, since the maximum voltage on the gate-source junction can not exceed 3.6 V. Instead, the diode configuration in Fig. 3.5 is obtained connecting in the pass element M the gate with the source. This circuit solution protects the gate-source junction from high voltages. A reduction of the ON-resistance of the M pass element in Fig. 3.5 is obtained increasing the overdrive with a P-MOSFET driver.

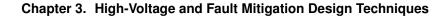

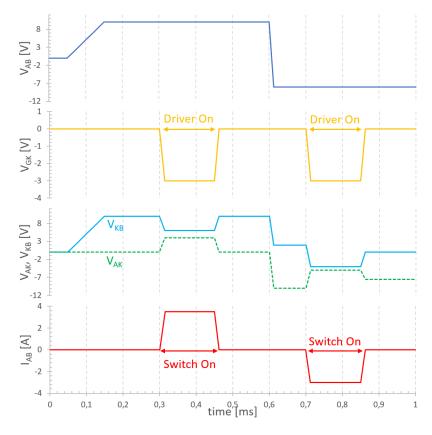

Fig. 3.6 shows the operative modes of the circuit in Fig. 3.5. The dotted green and red lines are the test bench signals: the first is the voltage across the equivalent diode ( $V_{AK}$ ), and the second is the control signal of the driver ( $V_{GK}$ ). The solid blue signal  $I_{AK}$  in Fig. 3.6 is the current value inside the pass element M. If the  $V_{AK}$  voltage drop is higher than a threshold voltage Vth, the M and Mb MOSFET transistors turn ON thanks to the diode effect and the current flows regardless the driver state (solid blue signal  $I_{AK}$  from 0.0625 ms to 0.6 ms in Fig. 3.6). Of course, when the driving signal enables the driver, the MOSFET transistors are in deep conduction and their ONresistance is lower, and the current increases (solid blue signal  $I_{AK}$  from 0.3 ms to 0.45 ms in Fig. 3.6). If the  $V_{AK}$  voltage drop is negative, the proposed circuit topology does not allow the flow of current (solid blue signal  $I_{AK}$  from 0.6 ms to 0.7 ms and from 0.85 ms to 1 ms) unless the driving signal enables the driver and the current is different from zero (solid blue signal  $I_{AK}$  from 0.7 ms to 0.85 ms in Fig. 3.6).

The Mb MOSFET drives the bulk of the M MOSFET to avoid that the drain-bulk parasitic diode turns ON and that the parasitic PNP bipolar transistor (drain-bulk-substrate) injects current in the substrate. If the bulk of the MOSFET has a small size, then its ON-resistance is high and consequently, the voltage drop is high. The size of the Mb in comparison with the size of M is chosen following the Eq.3.5.

Figure 3.6: Test of circuit in Fig. 3.5.

$$M_{b-size} = \frac{M_{size}}{10} \tag{3.5}$$

The 1:10 ratio has been found considering the charge injected into the bulk and substrate (Qb in Table 3.4, the ON-resistance of the Mb device ( $R_{ON}$  in Table 3.4), and the voltage drop (Vdrop in Table 3.4) between the drain-bulk junction for different ratios of Mb and M. Table 3.4 shows some simulation results. For the small size of Mb (e.g. ratio 1/200) the voltage drop is too high, so the parasitic bipolar turns ON and injects charge in the substrate. Increasing the size of Mb (e.g. reducing the size ratio from 1/200 to 1/10) the voltage drop decreases and the charge injected in the substrate decreases. On the other side, by increasing the size of Mb the bulk width of Mb increases and, beyond the 1/10 ratio, a higher charge is required. Therefore, a 1/10 ratio is chosen to size the MOSFETs.

Table 3.4: Mb and M MOSFETs size ratio.

| Size ratio | Qb [pC] | $\mathbf{R}_{ON}$ [ $\Omega$ ] | Vdrop [mV] |

|------------|---------|--------------------------------|------------|

| 1/200      | 460     | 380                            | 798        |

| 1/20       | 206     | 47                             | 228        |

| 1/10       | 26      | 22                             | 122        |

| 1/5        | 52      | 12                             | 56         |

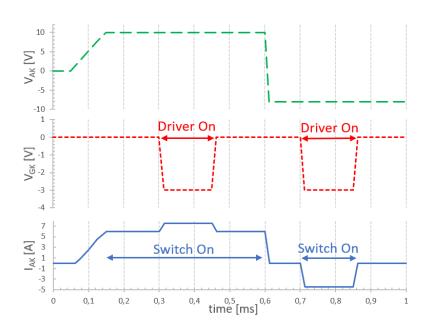

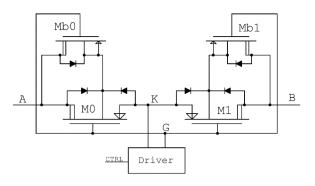

Not all the switches of this converter can be replaced with the circuit in Fig. 3.5, because they are also controlled by the  $V_{AK}$  voltage and not only by driving signals. One solution to solve this issue is the use, as in Fig. 3.7, of the back-to-back two-diode structure, with external drains to protect the low-voltage junctions (the voltage across the source-gate and the source-bulk junctions cannot exceed 3.6 V). Fig. 3.8 shows the signals of the operative modes of the back-to-back circuit in Fig. 3.7. The blue and

orange lines are the test bench signals applied at the switch. The light blue and dotted green signals are the voltages  $V_{AK}$  and  $V_{KB}$  on the single diode topology. The red signal  $I_{AB}$  is the current value that flows in the two-pass elements M0 and M1.

Figure 3.7: Back-to-Back diode topology.

Figure 3.8: Test of circuit in Fig.3.7.

The advantage of the circuit in Fig. 3.7 respect to Fig. 3.5 is the following: the positive  $V_{AB}$  voltage that turns ON the M and Mb MOSFETs in Fig. 3.5, in Fig. 3.7 turns ON the M0 and Mb0 MOSFETs ( $V_{AK} = 0$  so they are ON), but M1 and Mb1 are in inverse polarization ( $V_{KB} \neq 0$ ) so the current cannot flows (red signal  $I_{AB}$  until 0.3 ms in Fig. 3.8). To turn ON the whole circuit of Fig. 3.7 it is necessary driving the elements with an external driver, which creates a controlled voltage drop between the gate and

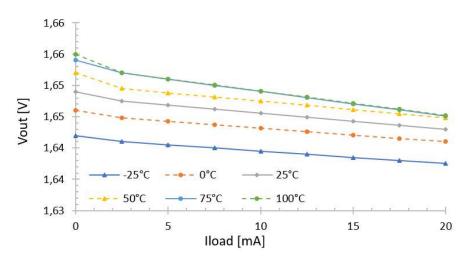

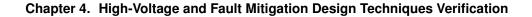

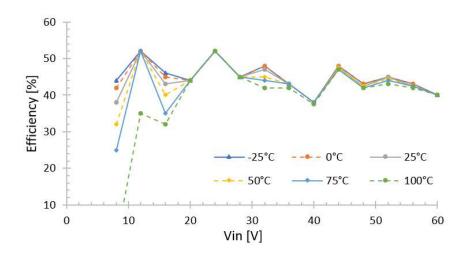

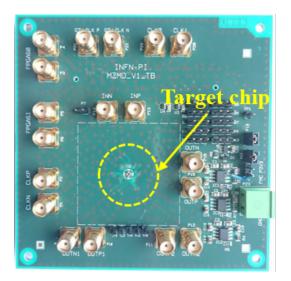

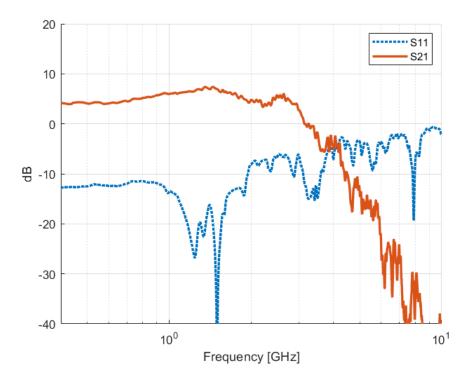

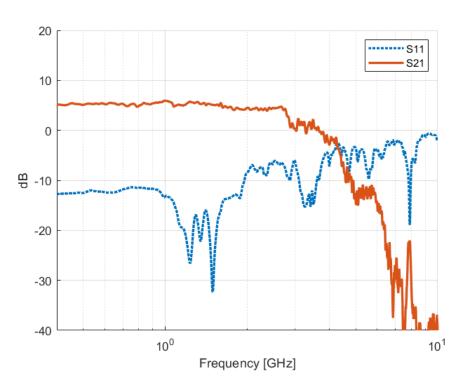

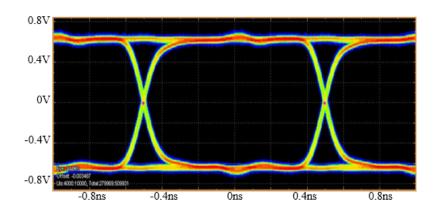

#### Chapter 3. High-Voltage and Fault Mitigation Design Techniques