# Università di Pavia

# Frequency Doublers and Phase Shifters for D-band Phased Arrays in SiGe BiCMOS Technology

DEPARTMENT OF ELECTRICAL, COMPUTER AND BIOMEDICAL ENGINEERING

Ph.D. Degree in Microelectronics

Supervisor: Ch.mo Prof. Andrea Mazzanti Ph.D. Candidate:

Lorenzo Piotto

# **Abstract**

The continuous growth in the demand for seamless and high-data-rate mobile connectivity is setting severe requirements to the network infrastructure for 5G and beyond. The development of technologies capable of working above 100 GHz opens with confidence to mm-Wave and sub-THz bands, promising to achieve data rates above 100 Gbps with wireless links, giving the advantage of reduced deployment costs and higher flexibility compared to fiber solutions. On the other hand, with the increasing path loss and limited output power achievable by single amplifiers, phased-array systems become the only solution to increase EIRP, providing both high antenna gain and power combining. At the same time, the system gains the flexibility of beam steering, relaxing the challenges of TX-RX antenna alignment, and opening to a reconfigurable network interconnection.

The need for high performance transceivers has to cope with the challenge of operating at frequencies in the range of one half or one third of the  $f_{max}$  of currently available silicon technologies, negatively affecting the key performance metrics, as output power, low noise, wide bandwidth and efficiency.

The three years research activity focused on the development of key building blocks in SiGe BiCMOS technology, targeting D-band phased array transceivers for backhaul communications.

The first part concentrates on the need for wideband and high efficient frequency multipliers, proposing a novel mixer based frequency doubler architecture. The conversion gain is improved by applying a DC offset to the switching-quad transistors, such that the duty-cycle is reduced and the output current assumes an almost square-wave shape at twice the input frequency. The DC offset is self-adjusted by a low-frequency feedback loop to maintain optimal performance against input power and PVT variations.

A proof of concept design in K-band demonstrates a remarkable 85% fractional bandwidth along with a  $P_{\rm sat} = 5.7$  dBm, 17% collector efficiency and better than 40 dB rejection of the fundamental component. The concept is validated also in D-band, with experimental results showing a peak output power of 6.5 dBm at 148 GHz with 7.4% power conversion efficiency and 8 dB of conversion gain. The -3dB bandwidth is from 125 GHz to 170 GHz and output power remains greater than 0 dBm over the full D-band, from 110 GHz to

#### 170 GHz.

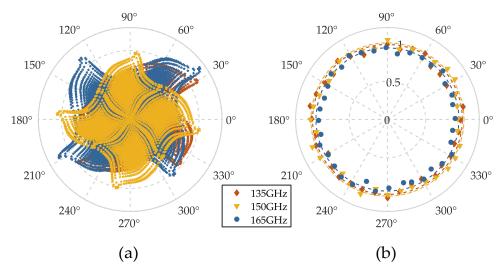

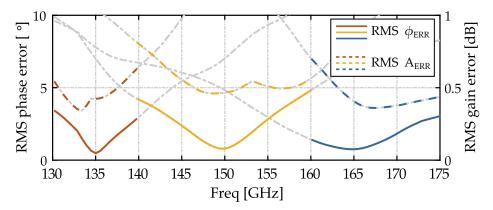

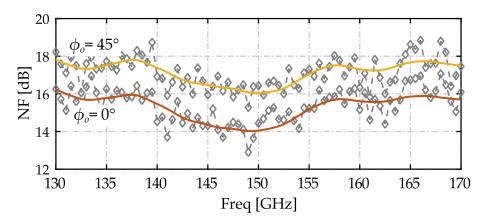

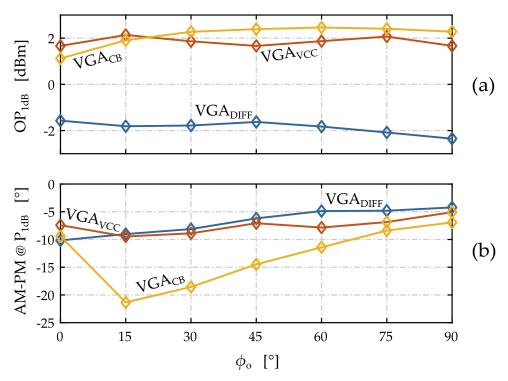

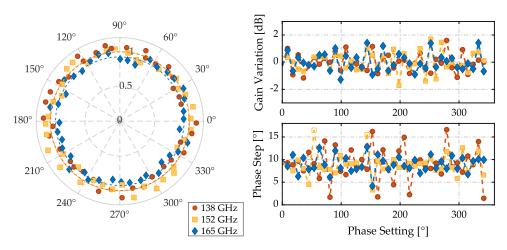

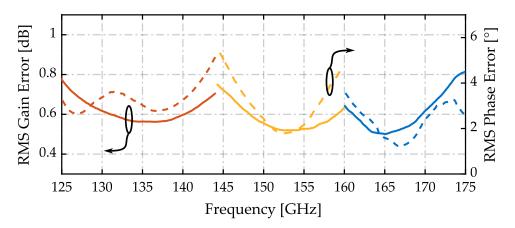

The second part of the thesis focuses on phase shifters. First, the vector interpolation principle is investigated, with particular care on the AM-AM and AM-PM distortion mechanisms introduced by the need for high dynamic range variable gain amplifiers (VGAs). A testchip proves [130 - 175] GHz bandwidth along with the highest reported  $OP_{1dB} = 1.8$  dBm and collector efficiency,  $\eta = 2.4\%$ , against vector interpolation phase shifters operating in the same frequency range, and low RMS amplitude and phase errors of 0.8 dB and 5°, respectively.

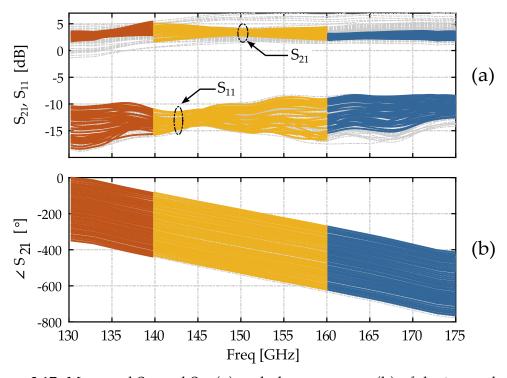

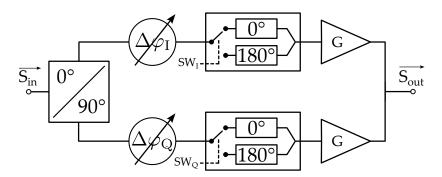

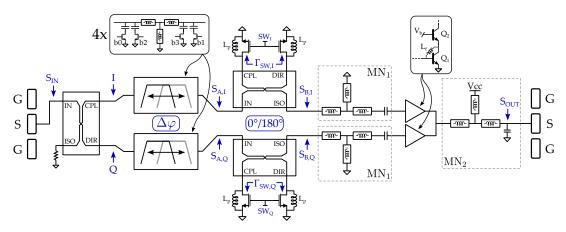

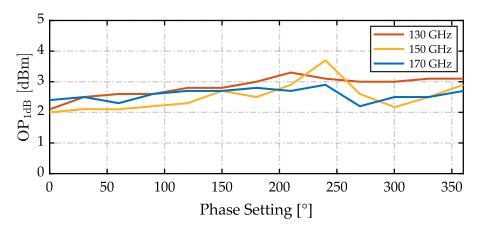

To further increase the limited efficiency of the vector interpolation scheme, and both the bandwidth and high-insertion-loss limitations of fully-passive solutions, a novel phase shifter architecture is proposed. The input signal is split into I/Q vectors which are shifted with passive fine step phase shifters, passed through  $0^{\circ}/180^{\circ}$  passive phase inversion blocks, and finally combined by a pair of amplifiers operated at constant gain for optimal linearity. The relative phase shift between the I and Q vectors is exploited for gain and phase errors corrections, avoiding the need of VGAs. Measurement results on a SiGe BiCMOS test-chip working in D-band compare favorably against previous works, demonstrating [130 - 170] GHz bandwidth, a superior  $OP_{1dB}$  above 2 dBm and with the highest power efficiency of 5%.

This work has been carried out at the Analog Integrated Circuits (AIC) Laboratory of University of Pavia, and received funding from the Commission of the European Union within the H2020 DRAGON project (Grant Agreement No. 955699) and KDT SHIFT project (Grant Agreement No. 1010962). The definition of system requirements was carried out in collaboration with the group of Huawei Milan, Italy.

# **Contents**

| A | bstra                    | ct      |                                                         | 3  |  |  |  |

|---|--------------------------|---------|---------------------------------------------------------|----|--|--|--|

| 1 | Intr                     | oductio | on                                                      | 1  |  |  |  |

|   | 1.1 The backhaul network |         |                                                         |    |  |  |  |

|   | 1.2                      | Phase   | ed Array Systems                                        | 3  |  |  |  |

| 2 | Free                     | quency  | Doublers                                                | 7  |  |  |  |

|   | 2.1                      | Propo   | sed Frequency Doubler                                   | 10 |  |  |  |

|   |                          | 2.1.1   | Operation Principle                                     | 10 |  |  |  |

|   |                          | 2.1.2   | Duty-cycle Control Mechanism                            | 13 |  |  |  |

|   |                          | 2.1.3   | Robustness to Input Amplitude Variation and Phase Skew  | 15 |  |  |  |

|   | 2.2                      | K-Ban   | nd Frequency Doublers - Circuit Design                  | 17 |  |  |  |

|   |                          | 2.2.1   | Quadrature-driven Gilbert-cell Frequency Doubler        | 17 |  |  |  |

|   |                          | 2.2.2   | Gilbert-cell Frequency Doubler with Self-Adjusted Duty- |    |  |  |  |

|   |                          |         | cycle                                                   | 19 |  |  |  |

|   |                          | 2.2.3   | Loop Gain Analysis and Design Considerations            | 20 |  |  |  |

|   |                          | 2.2.4   | Experimental Results                                    | 23 |  |  |  |

|   | 2.3                      | D-Bar   | nd Frequency Doubler                                    | 29 |  |  |  |

|   |                          | 2.3.1   | Circuit Description and Implementation                  | 29 |  |  |  |

|   |                          | 2.3.2   | Experimental Results                                    | 33 |  |  |  |

|   | 2.4                      | Chapt   | ter Summary                                             | 37 |  |  |  |

| 3 | Pha                      | se Shif | ters                                                    | 39 |  |  |  |

|   | 3.1                      | Vector  | r-interpolation phase shifter                           | 41 |  |  |  |

|   |                          | 3.1.1   | Operation principle and AM-AM and AM-PM Distortion      | 41 |  |  |  |

|   |                          | 3.1.2   | Comparison of VGA Topologies                            | 44 |  |  |  |

|   |                          | 3.1.3   | Circuit Design                                          | 52 |  |  |  |

|   |                          | 3.1.4   | Experimental Results                                    | 60 |  |  |  |

|   | 3.2                      | Digita  | al D-band phase shifter                                 | 66 |  |  |  |

|   |                          | 3.2.1   | Operation Principle                                     | 67 |  |  |  |

|   |                          | 3.2.2   | Circuit Design                                          | 68 |  |  |  |

|   |                          | 3.2.3   | Measurement Results                                     | 70 |  |  |  |

|   | 3.3                      | Chapt   | ter Summary                                             | 74 |  |  |  |

#### Contents

| 4 Conclusion         | 75 |

|----------------------|----|

| List of Publications | 77 |

| List of Figures      | 79 |

| Bibliography         | 83 |

Introduction

his dissertation summarizes the three years activity carried out while pursuing the Ph.D. at the Analog Integrated Circuit Laboratory, supervised and mentored by Prof. Andrea Mazzanti and with a fruitful cooperation with various colleagues and friends.

Most of the research work focused on developing key building blocks targeting D-Band phased array transceivers for backhaul communication, operating in the frequency range [130-175] GHz. In particular, the first part of the activity concentrated on frequency doublers, while the latter on phase shifters.

The dissertation is organized as follows:

Chapter one gives a brief introduction on the backhaul network, investigating why in D-band we will probably need phased arrays and what benefits/challenges they bring along.

*Chapter two* focuses on frequency doublers, introducing an architecture which is inherently broadband. A proof of concept is tested at low frequency to demonstrate the performance, while a second test chip extends the results in D-band.

Chapter three concentrates on phase shifters, with two implementation in D-band. The first is based on the vector interpolation principle, with a study of the distortion mechanisms that impair linearity. The second overcomes the linearity bottleneck in the vector interpolation approach, i.e. the VGAs, by leveraging a combination of passive phase shifting networks and active circuits, organized in order to minimize losses and avoid the need of gain control within the amplifying stages.

*Chapter four* eventually draws the overall conclusion.

#### 1.1 The backhaul network

Ever since, the challenges of new generation communication standards are pushing for higher data-rates, supporting massive number of connected devices, lowering latency and improving quality of service.

Among other important changes, one structural key aspect to accomplish this is to increase the number of radio nodes (base stations) distributed across the

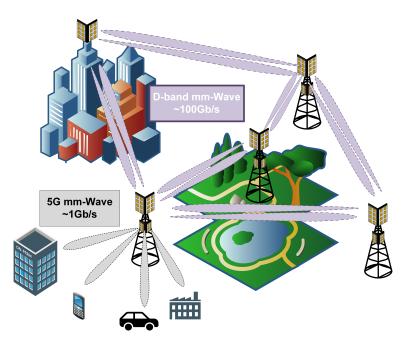

Figure 1.1: Network infrastructure: in gray the base station serving users and, in purple, the backhaul interconnection links

network, requiring a complex interconnecting mesh, aka *backhaul network*, as visible in Fig. 1.1. High research effort is involved on this topic in order to move backhaul communications from optical fiber (highly performing but expansive to lay) to wireless. [1] estimates more than a factor of 20 in cost between a point to point connection based on fiber optics with respect to a wireless link, not mentioning the deployment time and permission constraints.

The concept is not new and already in place for many years with commercial links up to the range of [10-25] Gbps at E-band frequencies ([71-86] GHz), exploiting channel bandwidths up to 2 GHz or, at lower bandwidth, higher spectrally efficient modulation schemes up to 1024-QAM. Being this a well established solution, research is pushing toward the next generation of backhaul links that is planned to be in D-band ([130-175] GHz), supporting frequency division duplexed (FDD) links with up to 5 GHz bandwidth, or time division duplexing (TDD) up to 10 GHz and throughput >100 Gbps.

This change brings few challenges. First of all, the so called free space path loss increases due to the scaling of the antenna size with frequency. Along with the wider channel bandwidth and a degraded receiver noise figure, this forces the need for higher EIRP for a given link distance. This may be mitigated by increasing the antenna directivity (i.e. scaling less the antenna size), at the expense of a narrower beam aperture which, considering an antenna gain of  $[30-40]\,\mathrm{dB}$ , is already in the order of few degrees, increasing the challenges of antenna alignment. The increased EIRP requirement sets a second issue, given by the limited output power achievable by a single power amplifier (PA) at these frequencies, even exploiting the more performing III-V technology nodes,

as done in the current E-band links.

These two limitations can be overcome by introducing the concept of phased arrays, already well explored in radars and satellite communications, where the single-front-end-single-antenna architecture is split into multiple front-ends (FE) and multiple radiating elements. The overall antenna directivity scales with the number of elements ( $G_{ANT} = 10 \log N + G_E$ , N being the number of elements and  $G_E$  the antenna gain of the single element) and the same advantages of increased EIRP at the TX side and increased SNR at the RX side are maintained with respect to a single high directivity antenna. At the same time, given we now have multiple (M) transmitters, the EIRP increases by another factor ( $10 \log M$ ) due to the over-the-air power combining, meaning we are not anymore limited by the output power of a single device. Moreover, by controlling the relative delays between the various radiating elements, the radiation pattern can be electronically steered, easing the issue of TX-RX antenna alignment and compensating for mechanical vibration of the antenna mounting point [2].

This architecture, along with the larger production scale, enables the use of silicon based technologies, with most focus, for now, on the SiGe BiCMOS that offers high speed/medium power heterojunction bipolar transistors (HBTs) with low power CMOS nodes, fundamental for the backbone of the transceiver (digital, biasing, monitoring etc.). If the volumes allows for it, fully CMOS solutions will probably follow. However, also hybrid architectures based on chiplets may have a future, leveraging the high performance of compound semiconductor technologies (e.g. InP) in the critical blocks, as the PA or the low noise amplifier (LNA), along with a scaled CMOS core which may become dense of functionalities.

# 1.2 Phased Array Systems

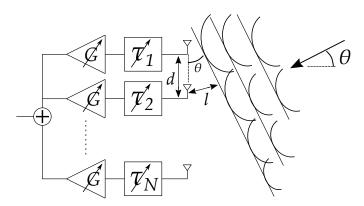

Figure 1.2: Phased Array structure

Figure 1.2 depicts a one dimensional structure of a phased array, where multiple antenna elements, usually spaced by a distance of  $d = \lambda/2$ , are fed by

multiple transceivers, also called beamformers, which may control the relative delay  $\tau$  and, as second order requirement, the relative gain G of the signal feeding each element. Figure 1.2 represents an RX scenario where the incoming wave arrives with an angle  $\theta$  with respect to the normal plane of the array. From purely geometrical considerations, between one element and the successive, the wave has to travel a further distance  $l = d \cdot \sin \theta$ , introducing a delay  $\tau' = c/l$ , with c being the speed of light as we assume we are in air. It is therefore clear that, to achieve constructive summation at the "+" node, the relative delay between adjacent channels needs to be  $\tau_m - \tau_{m-1} = \tau'$ . To point the antenna along one direction, i.e. perform the beam steering, it is therefore sufficient to change the value of the relative delay. The more the antenna elements, the higher the selectivity of the constructive/destructive interference, which leads to narrower beam aperture and higher the antenna directivity. The concept is extended in the two dimensions applying the same approach on both azimuth and elevation.

As said, a second desired feature is relative gain control among the channel. This is used to improve the radiation pattern of the antenna by reducing the undesired side lobes [3] that arise, especially when the beam steering angle is increased.

We have seen that, by its nature, a phased array requires a progressive delay among the different channels, which is proportional to the number of elements and the desired beam steering range, also called scan angle of the array. This may be in the order of many periods of the RF frequency and it is normally unpractical to achieve in the analog domain, requiring digital or hybrid beamforming architectures. On the other hand, these solutions are more complex, power hungry and difficult to be realized at mm-Wave bands, as the required delay resolution scales with frequency.

We all know that, at a single frequency, the delay can be substituted by a phase shift. This has the major benefit of being periodic, thus it does not scale with the array size, and easily implementable in RFICs. However, this simplification can be employed only when the fractional bandwidth of operation is narrow, as typically the case in communication systems (e.g. in D-band the instantaneous channel BW is 5 GHz over a 150 GHz carrier), since, in general, it introduces undesired impairments as beam squinting, a modulation/broadening of the pointing angle of the antenna  $\theta$  [4], and signal distortion, similar to the intersymbol interference introduced when not fulfilling the Heaviside condition [5].

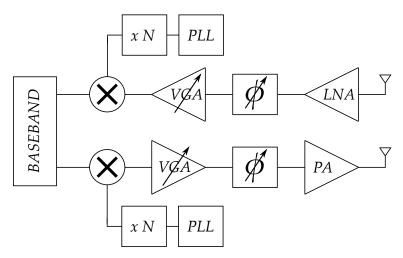

Figure 1.3 shows a simplified block diagram of a wireless communication system. This is not a general picture, as many variants on the architecture are possible. Blocks are divided into the TX and RX chains, which, in the case of an FDD system, may be connected to separate antennas. The RX chain starts

Figure 1.3: Wireless communication system block diagram

with the low noise amplifier (LNA) required to minimize the noise figure of the receiver, maximizing the sensitivity. Then, phase shifter and the variable gain amplifier (VGA) are used to support beamforming. Later, the RF signal is downconverted at lower, or, as in this case, baseband frequencies, where it is processed by the baseband unit, also in charge of controlling all the blocks. The same concept, but in reverse, is used in the TX side, which ends with the power amplifier (PA), in charge of maximizing the power to the antenna, and, in general, it is the block dominating the overall power efficiency of the TX chain.

On top and bottom are the frequency synthesizer, formed by a phase locked loop (PLL), normally working in sub mm-Wave frequencies, and a frequency multiplier to generate the high frequency LO.

Frequency Doublers

requency synthesis is a key function in RF and mm-Wave wireless communication and sensing. In this framework, the development of wideband components and systems is presently driving intense research activity for applications such as dual band 5G transceivers [6], [7] and high resolution imaging in industrial [8], [9], medical [10], [11] and scientific fields. Typically, RF frequency synthesis is based on a Phase-Locked Loop (PLL) with a Voltage-Controlled Oscillator (VCO) operating at the target output frequency. However, the design of PLL components is made challenging when the operating frequency is increased towards the mm-Wave band, and this approach limits the overall synthesizer performance. As an example, mm-Wave frequency dividers are narrow-band or power hungry, while integrated VCOs display the best performance (efficiency, phase noise and tuning range) in a frequency range that is typically below 15 GHz [12].

Moving towards mm-Wave, a more efficient synthesis solution consists of employing frequency multipliers, cascaded to a lower frequency PLL, to reach the target band.

Frequency doublers (and in general even-order multipliers realized by cascading doublers) are commonly preferred over odd-order multipliers because of their intrinsic performance advantage. Multiple topologies are available, but they can mostly be classified into push-push rectifiers and multiplier-based frequency doublers.

Push-push topologies, whose concept is depicted in Fig. 2.1a, are based on a pair of class-B biased transistors, driven by anti-phase signals, which behave as full-wave rectifiers. Albeit very simple, this solution has several shortcomings. First, the conversion efficiency is limited; moreover, it needs a differential input while delivering a single-ended output, and it suffers from poor rejection of the fundamental frequency component. In fact, the input common mode arising from amplitude and phase unbalances on the (ideally balanced) driving signals is directly transferred to the output current. Different approaches have been investigated to mitigate the drawbacks of this structure. Push-push circuits combined with injection-locked oscillators have been proposed to boost the conversion gain and efficiency at the expense of bandwidth [13], [14], [15].

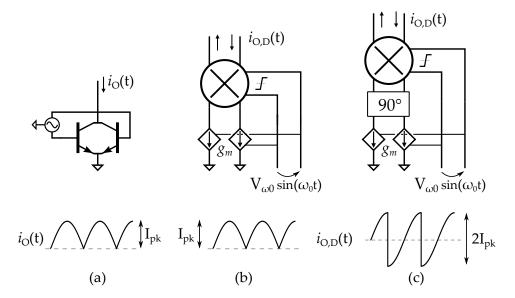

Figure 2.1: Frequency doubler architectures. Push-push pair (a) and Gilbert-cell mixer driven by in-phase (b) and in-quadrature (c) signals.

Solutions to attenuate the fundamental frequency at the output through harmonic traps, by cancelling the input common-mode, or by driving push-push structures with quadrature signals require tuned circuits [16], complex baluns [17] or hybrid couplers [18], thus again limiting the operation bandwidth or with a penalty in output power and efficiency [19]. Waveforms shaping [20] or the addition of a balancing branch to the push-push pair [21] display enhanced fundamental frequency rejection and broadband operation at the expense of reduced conversion gain or even high conversion loss [20].

Frequency doublers can also be realized with analog multipliers. When both the input ports are fed with signals at angular frequency  $\omega_0$ , the fundamental component of the output signal contains a component at  $2\omega_0$ . Double-balanced Gilbert-cell mixers are the natural implementation of analog multipliers, where one ports is linear with the input signal while the other operates in saturation. As shown in Fig. 2.1b, when both the inputs are driven by the same signal, the mixer provides a full-wave rectified output current as in the case of the push-push doubler. But, contrary to the push-push rectifier, a double-balanced Gilbert cell operates with fully differential input and output signals, thus it is ideally insensitive to the input common-mode. This feature grants an advantage on the rejection of the input-frequency component and all odd harmonics in general. The architecture in Fig. 2.1b is intrinsically broadband, as confirmed by the design in [22] which targets ultra-wide operation bandwidth. The major limitation of an in-phase-driven Gilbert cell is the relatively low  $2^{nd}$  harmonic conversion coefficient,  $\alpha_2$ , defined as the fundamental Fourier component of

the output current (at  $2\omega_0$ ) normalized to the peak input amplitude  $I_{pk}$ . As for the push-push rectifier,  $\alpha_2=0.42$ . In addition, looking at the waveform in Fig. 2.1b, a strong DC component is present in the differential output current with a value, normalized to  $I_{pk}$ , equal to  $\alpha_0=0.63$ . The non-zero mean current might be problematic when resistive loads are employed in ultra-wideband designs [22], [23].

These issues are solved driving the two ports of the mixer with quadrature signals, as shown in Fig. 2.1c. The previously considered rectified output current is here chopped at half the period, producing a symmetrical signal with zero DC component ( $a_0 = 0$ ). Noticing that the two waveforms at the bottom of Fig. 2.1b and 2.1c have the same total energy,  $a_0 = 0$  in Fig. 2.1c implies a higher harmonic content. In fact, by computing the Fourier components,  $a_2 = 0.85$ , i.e. the harmonic conversion gain of the quadrature-driven Gilbert-cell is doubled. On the other hand, the frequency doubler architecture of Fig. 2.1c needs a quadrature phase-shifting block, commonly implemented with a polyphase filter [24] or with a hybrid coupler [25], which sets an intrinsic bandwidth limitation along with the addition of losses and area occupation.

In [26], [27] we have proposed a novel approach to improve the overall performance of a Gilbert-cell based frequency doubler. If the saturated port of the mixer is driven at a deliberately reduced duty-cycle, the DC component on the output current is removed while simultaneously boosting the second harmonic conversion gain. The reduced duty-cycle is self-adjusted by a low-frequency feedback loop to maintain optimal operating conditions. The proposed approach still shows a good odd-harmonics suppression, typical of Gilbert-cell frequency doublers, combined with the high conversion efficiency of the solution in Fig. 2.1c. In addition, by avoiding quadrature generation, it allows for wideband operation.

The operation principle is first demonstrated at low frequency, with a doubler covering the full K-band [27], where transistor parasitics and interconnections do not introduce significant phase shifts. A direct comparison with a conventional mixer based frequency doubler driven by quadrature signals is carried out with the same technology and core structure. The results show a performance advantage in terms of bandwidth, gain and efficiency. The same concept is then implemented at sub-THz frequency with a doubler covering the D-band [28]. In this case, the RF core is modified to account for the relevant and unavoidable phase shifts introduced by parasitic components, ensuring an in-phase driving of the mixer input ports.

The chapter starts with explaining the operation principle of the proposed frequency doubler and its robustness against impairments. Then the design of the K-band frequency doublers is described, including thorough design

consideration for the feedback loop controlling the duty-cycle, followed by measurements and comparison table. Later, the D-band implementation of the same operating principle is reported along with the measurement results, eventually followed by the conclusion.

Figure 2.2: Frequency doubler based on a Gilbert-cell mixer.

# 2.1 Proposed Frequency Doubler

## 2.1.1 Operation Principle

The proposed frequency doubler is built around a conventional double-balanced Gilbert-cell mixer with the core schematic drawn in Fig. 2.2. The current sources  $\mathfrak{i}_{P/N}(t)$  represent the tail transconductors, operating in class-A with a DC current  $I_{DC}$  and injecting sinusoidal differential currents with amplitude  $I_{pk}$  at angular frequency  $\omega_0$ :

$$\begin{cases} i_{P}(t) = I_{DC} + I_{pk} \sin(\omega_{0}t) \\ i_{N}(t) = I_{DC} - I_{pk} \sin(\omega_{0}t) \end{cases}$$

(2.1)

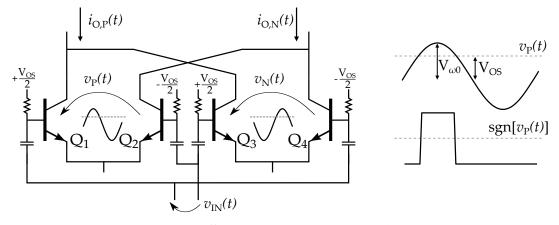

The switching-quad transistors  $Q_{1,2}$  -  $Q_{3,4}$  are assumed to be driven with sufficiently large signals,  $\nu_P(t)$ ,  $\nu_N(t)$ , to operate as ideal current switches or, equivalently, the differential driving signals  $\nu_P(t)$  and  $\nu_N(t)$  are considered as square waves with duty-cycle  $\delta$ . With the assumption above, the differential output current is:

$$i_{O,D}(t) = \frac{1}{2} (i_{O,P}(t) - i_{O,N}(t))$$

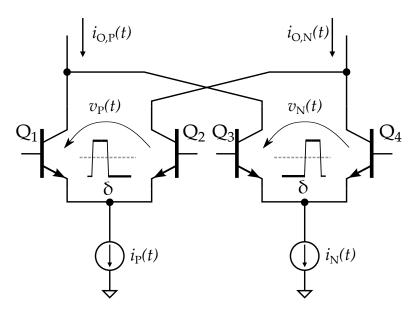

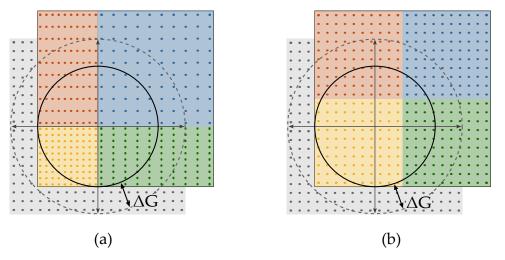

Figure 2.3: Waveforms with (a)  $\delta = 50\%$ , (b)  $\delta = 25\%$ .

$$\label{eq:iono} \begin{split} & \rightarrow i_{O,D}(t) = \frac{1}{2} \big( i_P(t) \cdot sgn[\nu_P(t)] + i_N(t) \cdot sgn[\nu_N(t)] \big) \end{split}$$

where  $sgn[\cdot]$  denotes the well-known sign function.

The resulting characteristic waveforms with a switching-quad duty-cycle of  $\delta = 50\%$  are plotted in Fig. 2.3a. In this situation, the Gilbert-cell mixer operates as a full-wave rectifier, with the output current given by:

$$i_{O,D}(t) = \frac{1}{2} |i_P(t) - i_N(t)| = |I_{pk} \sin(\omega_0 t)|$$

(2.3)

The fundamental component,  $I_{O,2\omega0}$ , is at twice the input frequency and the second-harmonic current conversion gain, defined as the ratio between  $I_{O,2\omega0}$  and the amplitude of the input current,  $I_{pk}$ , is:

$$a_2 = \frac{I_{O,2\omega 0}}{I_{pk}} = \frac{4}{3\pi} \sim 0.42 \tag{2.4}$$

The circuit performance can be improved by reducing the switching-quad duty-cycle to  $\delta = 25\%$ , as shown by the waveforms in Fig. 2.3b. In this case, by using (2.2), the output current  $i_{O,D}(t)$  can be written as:

$$i_{O,D}(t) = \begin{cases} \frac{1}{2} (i_{P}(t) - i_{N}(t)) = I_{pk} \sin(\omega_{0}t) & t \in T_{1} \\ \frac{1}{2} (-i_{P}(t) - i_{N}(t)) = -I_{DC} & t \in T_{2} \end{cases}$$

(2.5)

The bottom plot in Fig. 2.3b shows  $i_{O,D}(t)$  assuming the Gilbert-cell transconductors are operating at the edge of Class-A, i.e. with  $I_{pk} = I_{DC}$ .  $i_{O,D}(t)$

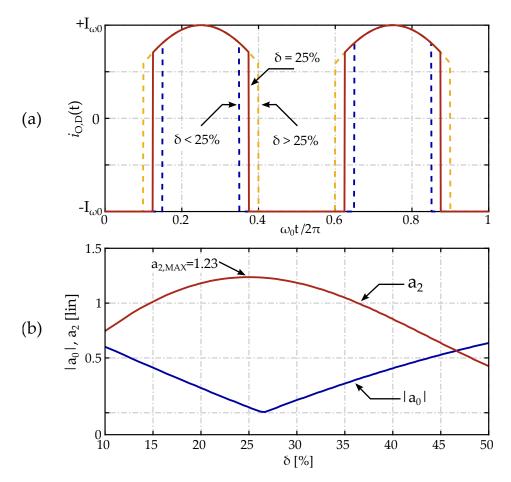

Figure 2.4: (a) Time domain waveforms vs duty-cycle  $\delta$ , (b) DC ( $\alpha_0$ ) and second harmonic ( $\alpha_2$ ) coefficients against duty-cycle  $\delta$ .

assumes an almost square-wave shape with a fundamental component at twice the input frequency. Approximating the waveform as a perfect square wave, the second-harmonic current conversion gain can be roughly estimated as  $\alpha_2 \sim \frac{4}{\pi} = 1.27$ .

Still considering  $I_{pk} = I_{DC}$ , to gain more insight, Fig. 2.4a shows graphically how the switching-quad duty-cycle modifies the shape of  $i_{O,D}(t)$  by modulating the duration of  $T_1$  and  $T_2$ , thus impacting on the mean value of the waveform,  $\overline{i_{O,D}(t)}$ , and its fundamental component,  $I_{O,2\omega0}$  (at twice the input frequency). Fig. 2.4b plots the normalized DC component of  $i_{O,D}(t)$  ( $a_0 = \overline{i_{O,D}(t)}/I_{pk}$ ) and the second-harmonic current conversion gain ( $a_2$ ), versus  $\delta$ .  $\delta = 25\%$  gives  $a_{2,MAX} = 1.23$  which is an increase of 3 times (9.5 dB) compared the case of  $\delta = 50\%$  duty-cycle previously considered (eq.(2.4)), and yet a remarkable 1.5x (3.5 dB) over the implementation shown in Fig. 2.1c where the input transconductors and the switching quad are driven by signals in quadrature phase. Still looking at Fig. 2.4b, at  $\delta = 25\%$  the DC component of  $i_{O,D}(t)$  is almost zero.  $a_0$  is perfectly nulled at a slightly higher duty-cycle ( $\delta \sim 26\%$ ) because the shape of  $i_{O,D}(t)$  is not exactly a square wave.

In summary, a reduced duty-cycle (ideally  $\delta = 25\%$ ) for the Gilbert-cell frequency doubler yields an output signal almost free of DC offset and a remarkable improvement of the harmonic conversion gain. It is also worth noticing that, regardless of the actual duty-cycle, the proposed approach preserves the fully balanced topology of the circuit, and thus an enhanced robustness to the leakage of the input signal and odd harmonics.

#### 2.1.2 Duty-cycle Control Mechanism

Generating and distributing a square-wave signal to drive the switching quad at the desired duty-cycle is obviously not feasible at RF and mm-Wave, given the high harmonic content it involves.

A more practical solution consists in exploiting the large signal behavior of the switching quad. In fact, provided the driving signal amplitude is sufficiently large, the two differential pairs in Fig. 2.2  $(Q_{1,2} - Q_{3,4})$  are sensitive to the sign of the differential signals  $\nu_P(t)$ ,  $\nu_N(t)$  and, ideally, not to the amplitude. Therefore, as shown in Fig. 2.5, the switching-quad duty-cycle can be reduced by applying a positive differential DC offset voltage,  $V_{OS}$ , to the base of the differential-pair transistors.

If  $v_{IN}(t) = V_{\omega 0} \sin(\omega_0 t)$  is the voltage feeding the mixer, the signals at the base of  $Q_{1,2}$  and  $Q_{3,4}$  in Fig. 2.5 are:

$$\begin{cases} v_{P}(t) = V_{OS} + V_{\omega 0} \sin(\omega_{0}t) \\ v_{N}(t) = V_{OS} - V_{\omega 0} \sin(\omega_{0}t) \end{cases}$$

(2.6)

and the offset voltage which gives the desired switching duty-cycle (i.e.  $\delta$  = 25%) can be immediately calculated:

$$V_{OS} = V_{\omega_0} \cos(\pi \delta) \Rightarrow V_{OS} \Big|_{\delta = 25\%} = \frac{V_{\omega_0}}{\sqrt{2}}$$

(2.7)

Notably, if  $v_{IN}(t)$  is the same signal driving the transconductors of the Gilbert cell, the addition of  $V_{OS}$  allows a simple regulation of the switching-quad

Figure 2.5: Offset-Duty cycle control mechanism.

duty-cycle while maintaining the correct timing shown in Fig. 2.3b, where the high-state of the equivalent square-wave switching signal is aligned to the peaks of the tail currents  $i_{P,N}(t)$ .

Eq.(2.7) shows that  $V_{OS}$  cannot be statically set, being dependent on the driving signal amplitude,  $V_{\omega_0}$ , which is in general not precisely defined and subject to low-frequency drift. The use of an envelope detector to generate  $V_{OS}$  proportional to  $V_{\omega_0}$  could be an option, with the drawback of high sensitivity to components spread and to the accuracy of the detector itself. Moreover, this open-loop approach is sub-optimal, not providing any correction to the non-ideal behavior of the switching quad, which becomes sensitive to the driving signal level when the amplitude is reduced.

A more robust and effective approach is suggested by noticing in Fig. 2.4 that, opposite to the case of  $\delta = 50\%$ ,  $\delta = 25\%$  leads to a quasi square-wave output current  $i_{O,D}(t)$  with almost zero DC component. Being the mean value of the  $i_{O,D}(t)$  relatively easy to measure, a low-frequency feedback loop can be closed to automatically adjust  $V_{OS}$  in order to null the DC component  $\overline{i_{O,D}(t)}$ . This technique yields a robust and nearly optimal performance, also compensating the real behavior of the switching quad at low driving amplitude  $V_{\omega_0}$ .

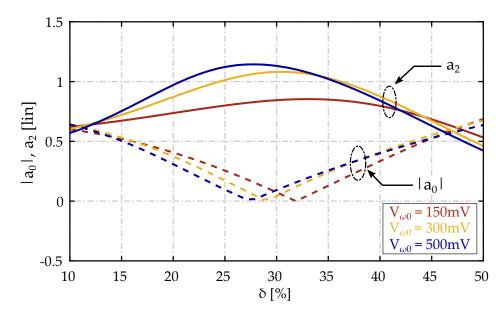

To gain further insight, Fig. 2.6 plots the normalized DC component of  $i_{O,D}(t)$  ( $\alpha_0$ ) and the second-harmonic current conversion gain ( $\alpha_2$ ) derived from simulations of the circuit in Fig. 2.5 at different  $V_{\omega_0}$ . The equivalent duty-cycle on the horizontal axis is regulated by changing  $V_{OS}$  and calculated with (2.7). With large amplitude (grey curves) the switching-quad behavior is close to the ideal case and the maximum conversion gain is achieved close to  $\delta=25\%$ . When  $V_{\omega_0}$  is reduced (orange and red curves),  $Q_{1,2}$  -  $Q_{3,4}$  no longer behave

Figure 2.6: Simulated DC and second-harmonic coefficients,  $a_0$ ,  $a_2$ , of the differential output current  $i_{O,D}(t)$  versus  $\delta$  for different  $V_{\omega_0}$ .

as ideal switches and  $a_2$  is maximized with a higher duty-cycle. Although  $a_2$  is relatively flat around the points of maxima, the different curves in Fig. 2.6 show that the notches of  $a_0$  track the peaks of  $a_2$ . Hence, by setting  $V_{OS}$  to null the DC component of the output differential current, the circuit is forced to operate at the points of maximum second-harmonic conversion gain, granting robustness and optimal performance against variation of  $V_{\omega_0}$ .

Finally, it is worth mentioning that the proposed approach for the switching-quad duty-cycle control is not sensitive to phase variations of the input signal and, more importantly, it does not affect the phase of the output signal. In fact, recalling Fig. 2.4a, the variation of duty-cycle modulates the duration of the high and low levels of the switching waveform,  $T_1$  and  $T_2$ , without impacting on the phase of the fundamental current component. This leads to the important observation, confirmed by simulations, that the loop parameters (such as gain, bandwidth and noise) do not impair the phase noise of the output signal.

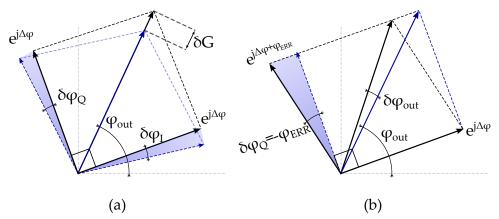

# 2.1.3 Robustness to Input Amplitude Variation and Phase Skew

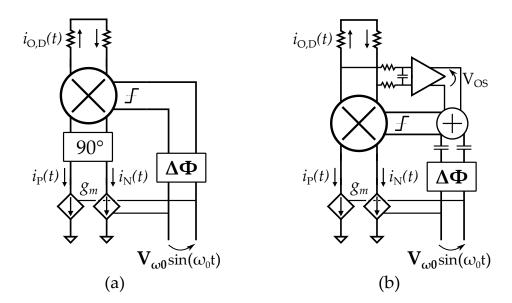

The output signal amplitude of Gilbert-cell frequency doublers is penalized by a reduction of the input driving level and by unwanted phase delay between the signals feeding the two input ports of the mixer. The robustness against these two impairments is evaluated in this section comparing the performance of a frequency doubler based on a Gilbert cell driven by quadrature signals (which features higher conversion gain, compared to in-phase driving) and the proposed architecture implementing a loop with self-adjusted switching-quad duty-cycle.

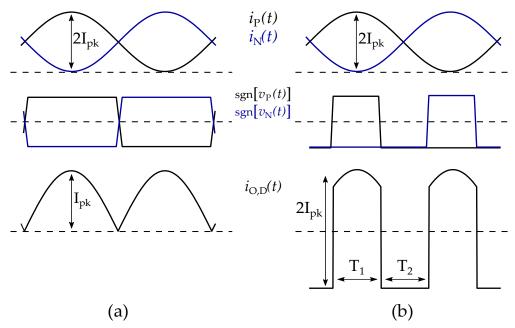

The detailed block diagrams of the two architectures are reported in Fig. 2.7. In both cases, a differential transconductor  $(g_m)$  driven by the input voltage  $v_{\rm IN}(t) = V_{\omega 0} \sin(\omega_0 t)$  generates the currents  $i_P(t)$ ,  $i_N(t)$  given by (2.1). In Fig. 2.7a the voltage  $v_{\rm IN}(t)$  feeds directly the hard-switching port of the mixer while the two currents  $i_P(t)$ ,  $i_N(t)$  are 90° shifted before the injection into the linear port. In Fig. 2.7b the linear and saturated ports of the mixer are ideally driven in phase. A DC voltage,  $V_{\rm OS}$ , generated by a low-frequency feedback loop, is added to  $v_{\rm IN}(t)$  at the hard-switching port, to null the output DC component by reducing the switching-quad duty-cycle.

In both architectures an unwanted phase shift  $\Delta\Phi$  is added to  $v_{\rm IN}(t)$  along the path toward the switching quad. This  $\Delta\Phi$ , unavoidable in practice, represents for example the delay added by routing parasitics in circuit layout. For the frequency doubler in Fig. 2.7a,  $\Delta\Phi$  has obviously the same effect of a phase error of the 90° phase shifter on the input currents. The impact of the input amplitude,  $V_{\omega0}$ , and  $\Delta\Phi$  on the output signal amplitude is now evaluated.

Figure 2.7: Block diagrams of the quadrature-driven Gilbert-cell based frequency doubler (a) and the presented reduced duty-cycle solution (b).

Assuming hard-switching operation of the mixer, the output differential current for the quadrature-driven Gilbert cell in Fig. 2.7a is given by:

$$i_{O,D}(t) = I_{pk} \cos(\omega_0 t) \cdot \text{sgn}[\sin(\omega_0 t + \Delta \Phi)]$$

(2.8)

with  $I_{pk} = g_m V_{\omega 0}$ . The magnitude of the fundamental component of  $i_{O,D}(t)$ ,  $I_{O,2\omega 0}$ , can be derived considering the  $1^{st}$  and  $3^{rd}$  order components of the Fourier expansion of the sign function. With some algebraic and trigonometric manipulations:

$$I_{O,2\omega 0} = I_{pk} \frac{4}{3\pi} \sqrt{4\cos^2(\Delta\Phi) + \sin^2(\Delta\Phi)}$$

(2.9)

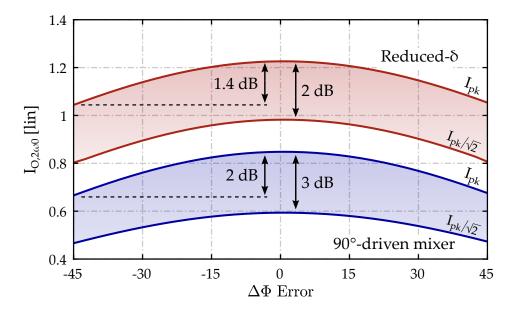

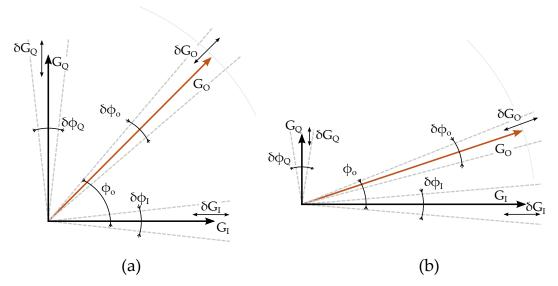

From (2.9), the output amplitude of a quadrature-driven mixer is proportional to the input signal amplitude (being  $I_{pk}=g_mV_{\omega0})$  and the harmonic conversion gain is reduced from its maximum (a\_2,\_MAX = 8/3 $\pi$  ~ 0.85) when  $\Delta\Phi=0$ , reaching a minimum for  $\Delta\Phi=\pm90^\circ$  (i.e. when the two ports of the multiplier are driven in phase). To gain insight, the impact on the output second harmonic component  $I_{O,2\omega0}$  of a 3 dB reduction in  $I_{pk}$  and  $\pm45^\circ$  in  $\Delta\Phi$  is graphically shown by the blue area on the plot in Fig. 2.8.

The same analysis in closed-form cannot be carried out for the proposed frequency doubler architecture in Fig. 2.7b, since  $V_{\omega 0}$  and  $\Delta \Phi$  influence both the fundamental and DC components of the output, thus affecting the steady-state  $V_{OS}$  and switching-quad duty-cycle set by the feedback loop. The impact

Figure 2.8: Simulated second-harmonic component  $I_{O,2\omega0}$  of the reduced duty-cycle and quadrature-driven mixer based frequency doublers against amplitude (3 dB) and phase ( $[-45,45]^{\circ}$ ) variations from the ideal values.

of the two parameters is evaluated with numerical simulations and the results are plotted in the red area of Fig. 2.8. Comparing the blue and red curves, the proposed frequency doubler architecture displays a slightly lower sensitivity to both  $\Delta\Phi$  and input amplitude reduction, with respect to the conventional solution of Fig. 2.7b.  $\Delta\Phi=\pm45^\circ$  leads to a conversion gain penalty of 1.4 dB (instead of 2 dB) while a reduction of 3 dB of the input signal level causes 2 dB (instead of 3 dB) attenuation of the output amplitude. Intuitively, the enhanced robustness to the impairments can be explained looking back at the expression of the output differential current given by (2.5):  $i_{O,D}(t)$  is sensitive (proportional) to the input signal only during  $T_1$ , while in the other part of the period  $(T_2)$  it is set by the DC bias current  $I_{DC}$  and not affected by  $V_{\omega0}$  and  $\Delta\Phi$ .

# 2.2 K-Band Frequency Doublers - Circuit Design

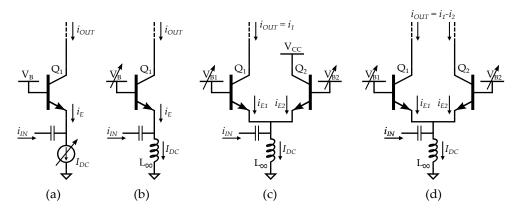

A conventional quadrature-driven Gilbert-cell frequency doubler and the proposed self-adjusted reduced duty-cycle architecture have been designed for experimental performance comparison. The circuits are implemented in a BiC-MOS  $0.13\mu m$  technology process and the design is presented in this section.

## 2.2.1 Quadrature-driven Gilbert-cell Frequency Doubler

Various quadrature-driven Gilbert-cell mixers are proposed in the literature, with the main difference in the position and implementation of the 90° phase

Figure 2.9: Schematic of the quadrature-driven Gilbert-cell frequency doubler.

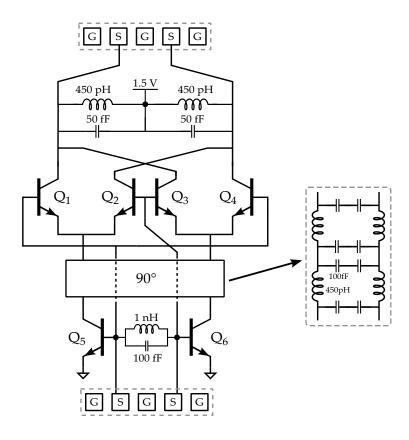

shifter. As an example, in [25] a hybrid coupler generates the voltage signals in quadrature to drive the two input ports of the mixer. In [29], [30] the 90° phase shift is implemented in the current domain and placed between the commonemitter input devices and the switching-quad transistors of the Gilbert-cell. In this case, the impedance transformation performed by the phase shifter yields some current gain, improving the overall frequency doubler conversion gain. The schematic of the quadrature-driven mixer is shown in Fig. 2.9, where biasing circuits are omitted for simplicity and readability. The Gilbert-cell switching quad is formed by  $Q_{1,2}$  -  $Q_{3,4}$  while  $Q_{5,6}$ , in common-emitter configuration, implement the input transconductors. All the transistors have the same emitter area of 8 µm x 0.13 µm. A lumped-element delay line is inserted between the common emitter devices and the switching quad to introduce a 90° phase shift at the nominal center input frequency of 10 GHz. The line, with characteristic impedance  $Z_{0,D} = 100 \Omega$ , is realized with two C-L-C sections where the capacitors also absorb the equivalent parasitic capacitances at the collectors of  $Q_{5,6}$  and at the emitter nodes of the switching quad. The simulated insertion loss of the delay line is ~0.9 dB. Resonant networks are used for input matching and to provide the optimal load impedance at the output in order to maximize the saturated power, Psat. The DC current of the input transistors,  $Q_{5,6}$ , is  $2 \times 7$  mA and the supply voltage is  $V_{CC} = 1.5$  V.

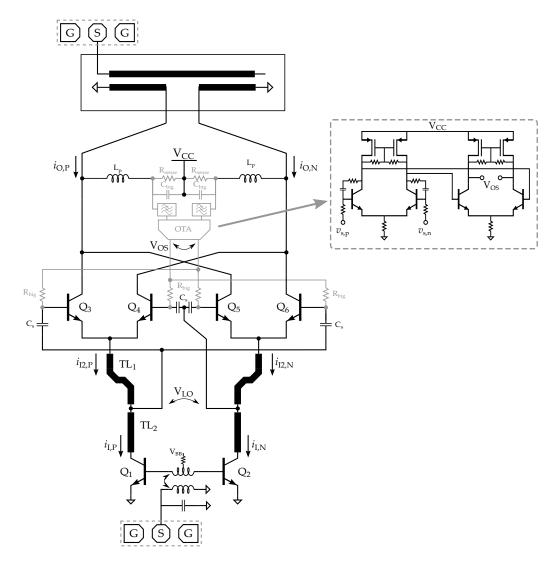

Figure 2.10: Schematic of the proposed reduced duty-cycle mixer based frequency doubler. Components in blue are part of the baseband feedback loop.

# 2.2.2 Gilbert-cell Frequency Doubler with Self-Adjusted Duty-cycle

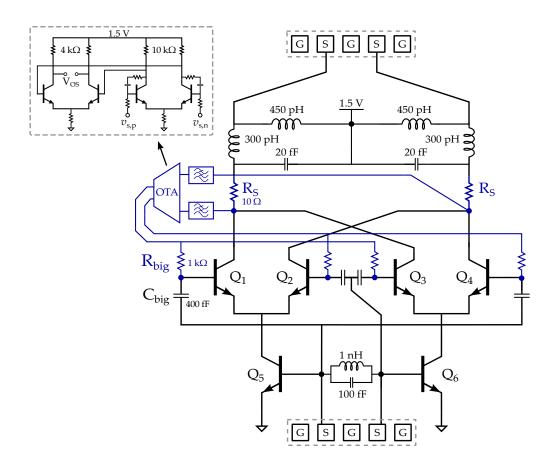

The schematic of the proposed frequency doubler architecture is shown in Fig. 2.10. The size of the transistors in the Gilbert cell, the DC currents and the supply voltage are the same used in the quadrature-driven mixer doubler previously described. The output network is slightly modified to match the optimal load without penalizing the wider circuit bandwidth, no more limited by the use of a 90° phase shifter.

The low-frequency feedback loop controlling the switching-quad duty-cycle is implemented with a fully-differential OTA which senses the DC output current through a pair of resistors,  $R_S$ , and provides a differential  $V_{OS}$  DC component to the base of  $Q_{1,2}$  and  $Q_{3,4}$ . The value of resistors  $R_S = 10\,\Omega$  is chosen as a compromise between low DC voltage drop and robustness against the input offset voltage of the OTA. The OTA is designed with 1.25 V output common mode voltage such that the DC voltage at the base of  $Q_{1,2}$  -  $Q_{3,4}$  can range from 1 V to 1.5 V, corresponding to a maximum  $V_{OS} = 500\,\text{mV}$ . Choke resistors  $R_{\text{big}} = 1\,\text{k}\Omega$  are used to feed the DC base voltage to the switching-quad transis-

tors while the input signal is coupled through capacitors  $C_{\text{big}} = 400 \text{ fF}$ .

The schematic of the OTA is shown as an inset in Fig. 2.10. It is composed of two cascaded differential stages with bipolar input transistors to benefit from the high transconductance and low offset voltage. The current consumption is 200  $\mu$ A from 1.5 V supply. Miller capacitors with zero-nulling resistors are placed across the first stage with the dual purpose of limiting the loop bandwidth and, together with resistors in series to the input of the OTA, to suppress the RF signal at the sense nodes ( $\nu_{S,P}$ ,  $\nu_{S,N}$ ), avoiding the saturation of the OTA input pair due to the excessive RF voltage swing. The gain of the OTA and the size of Miller capacitors are carefully selected not to compromise the loop stability while maintaining sufficiently high loop gain, as discussed in the following sub-section.

The DC power consumption of the proposed frequency doubler is 21 mW from 1.5 V supply. The voltage drop across the sense resistors and the power consumption of the OTA are responsible for roughly 1 mW, i.e. only 5% of the total.

#### 2.2.3 Loop Gain Analysis and Design Considerations

Figure 2.11: Differential-mode half-circuit schematic of the low frequency feedback loop.

At low frequency, within the bandwidth of interest for the loop-gain analysis, inductors and capacitors in the output matching network of the circuit in Fig. 2.10 can be considered short- and open-circuits, respectively. Therefore, the feedback loop can be analyzed considering the simplified schematic in Fig. 2.11, where the Gilbert-cell is replaced with a differential-mode equivalent

half-circuit. The loop gain T(s) can be written as:

$$T(s) = R_S \cdot G(s) \cdot G_m \tag{2.10}$$

where G(s) represents the OTA open-loop transfer function and  $G_m$  is the equivalent transconductance of the transistors  $Q_1$  and  $Q_3$ . For simplicity, all the poles of T(s) are concentrated within the OTA, including also the decoupling network  $R_{big}$ - $C_{big}$ . The poles introduced by the switching-quad transistor parasitics appear at a much higher frequency and can be neglected.

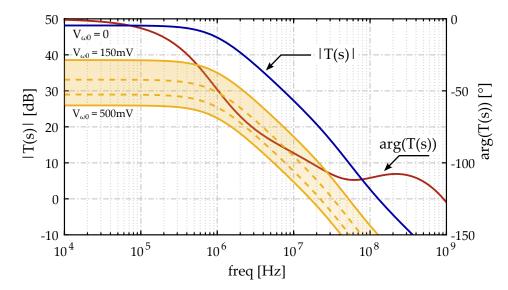

At the quiescent point, i.e. without the input signal applied to the frequency doubler, the equivalent transconductance  $G_m$  simplifies to the small-signal transconductance of  $Q_{1,3}$ :

$$G_{m} = G_{m,SS} = 2g_{m1,3} \tag{2.11}$$

The small-signal loop gain T(s) is shown in Fig. 2.12 with  $T(0) = 48 \, dB$  and a cut-off frequency  $(0 - dB \, gain)$  of  $\sim 150 \, MHz$ . Miller capacitors are not sufficient to ensure a dominant pole compensation, therefore the nulling resistance is used to move its associated zero to the left half-plane and cancel the second pole, providing a safe stability margin of  $\sim 70^\circ$ .

When the input signal is applied to the frequency doubler, the large-signal operation of the switching quad affects the loop gain. To take this effect into account, the equivalent transconductance  $G_m$  to be used in (2.10) must link the variation of the DC component in the output differential current,  $\overline{i}_{O,D}(t)$ , to a variation of the voltage  $V_{OS}$  applied by the OTA to the base of  $Q_{1,2}$  -  $Q_{3,4}$ . Assuming hard-switching operation of the switching quad, the large-signal  $G_m$  can be evaluated by first linking the mean value of the output current to a variation of the switching-quad duty-cycle  $\delta$ .  $i_{O,D}(t)$  is given by (2.5) and the effect of  $\delta$  on its shape is shown graphically in Fig. 2.4a. By integrating the waveform, the mean value is:

$$\overline{\mathfrak{i}_{\mathrm{O},\mathrm{D}}(\mathsf{t})} = \mathrm{I}_{\mathrm{pk}}\left(2\delta - 1 + \frac{2}{\pi}\sin(\pi\delta)\right) \tag{2.12}$$

while the relation between  $\delta$  and  $V_{OS}$  is derived from (2.7):

$$\delta = \frac{1}{\pi} \cos^{-1} \frac{V_{OS}}{V_{OO}}$$

(2.13)

where  $V_{\omega 0}$  is the amplitude of the RF signal driving the switching quad, which corresponds to the input amplitude of the frequency doubler. Combining (2.12) and (2.13), the equivalent large-signal transconductance can be expressed as:

$$G_{m} = G_{m,LS} = \frac{\partial \overline{i_{O,D}(t)}}{\partial V_{OS}}$$

(2.14)

Figure 2.12: Bode plot of the Loop Gain T(s). Red curve - small signal loop gain magnitude. Yellow area - Large signal loop gain magnitude with  $V_{\omega 0} = [150 - 500]$  mV.

Linearizing around the nominal operating regime of  $\delta = 25\%$  and replacing  $V_{OS} = \frac{V_{\omega 0}}{\sqrt{2}}$  from (2.7),

$$G_{m,LS} \sim 1.5 \frac{I_{pk}}{V_{\omega 0}} \tag{2.15}$$

The equation above can be further elaborated to achieve a more insightful comparison of the loop gain in large and small signal regimes. At large signal the transconductors  $Q_{5,6}$  in Fig. 2.10 inject into the switching quad a signal current  $(I_{pk})$  nearly equal to the DC current  $I_{DC}$ . Substituting  $I_{pk} = I_{DC}$  and noticing that the DC current in each transistor of the switching quad is  $I_{DC}/2$ , thus  $g_{m3,5} = (I_{DC}/2)/\nu_t$  (being  $\nu_t = 25\,\text{mV}$  the thermal voltage), (2.15) can be rewritten as:

$$G_{m,LS} \sim 1.5 \frac{I_{DC}}{V_{\omega 0}} = 1.5 \frac{2v_t}{V_{\omega 0}} g_{m1,3} = 1.5 \frac{v_t}{V_{\omega 0}} G_{m,SS}$$

(2.16)

Eq. (2.16) shows that when the frequency doubler is driven by a signal with amplitude larger than few tens of mV, the equivalent large-signal transconductance drops quickly below the small-signal level and the loop gain reduces with the inverse of  $V_{\omega 0}$ . Because all the poles/zeros in the loop gain belong to the OTA transfer function, the singularities of T(s) are not affected and thus the closed loop bandwidth is reduced when  $V_{\omega 0}$  increases. To gain further insight, the Bode plot of T(s) is shown in Fig. 2.12 at the quiescent point  $(V_{\omega 0}=0)$  and with  $V_{\omega 0}$  from 150 mV to 500 mV. Increasing  $V_{\omega 0}$ , both the loop gain magnitude and the gain cross-over frequency (i.e. the closed loop bandwidth) decrease, while the poles/zeros positions and the phase response are not affected. Simulations also confirm quantitatively the result predicted by (2.16). With  $V_{\omega 0}=500$  mV, (2.16) predicts a decrease in loop gain of 22 dB and, assuming a single-pole 20 dB/dec slope, the closed-loop bandwidth is

reduced by roughly a factor of 10.

In summary, from a design perspective, the presented analysis reveals that, if a sufficient phase margin is achieved at the quiescent point, the stability is not compromised during operation. On the other hand, the target loop gain required to meet a desired performance (i.e. accuracy on the steady-state duty-cycle) has to be sized at the maximum expected input signal amplitude, where the loop gain is minimum. As an example, looking at the simulations in Fig. 2.6, a 10% relative error in the duty-cycle from the optimal value (i.e.  $\delta \sim [23-29]\%$ ) leads to a negligible degradation in terms of harmonic conversion gain. At the same time, a 10% error in the duty-cycle corresponds to a roughly 10% error in the output DC component  $\overline{i}_{O,D}(t)$ . Being the steady-state error on  $\overline{i}_{O,D}(t)$  equal to 1/|T(0)|, the loop gain must remain greater than 20 dB, when the signal is present, to set  $\overline{i}_{O,D}(t)$  with the accuracy of 10%.

The same consideration can be applied to evaluate the effect of the OTA equivalent input offset voltage,  $V_{os}$ . From Monte Carlo simulations,  $V_{os}$  at 3- $\sigma$  is  $\pm 1.5$  mV, corresponding to a differential DC output current error of  $\pm 150$   $\mu A$ . The previously considered 10% error on the duty-cycle results in a differential DC component of 450  $\mu A$ , meaning that the OTA input offset voltage has a negligible impact on the overall doubler performance.

Moreover, as introduced in Sec. 2.1.2, the control of the duty-cycle does not change the phase of the second harmonic component of the output signal (Fig. 2.4a), meaning that impairments in the feedback loop, including the noise introduced by the OTA, may not degrade the phase noise performance of the frequency doubler.

## 2.2.4 Experimental Results

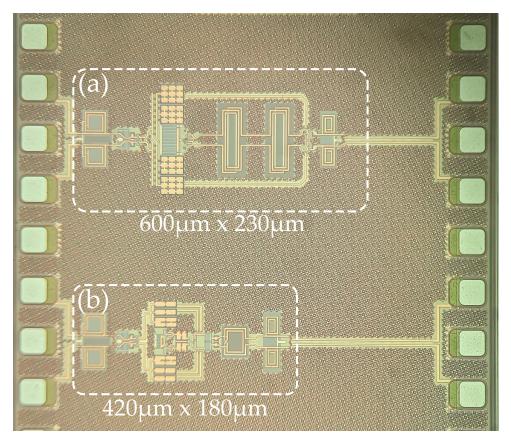

The photograph of the two realized frequency doublers is shown in Fig. 2.13. The core area occupation is  $600~\mu m \times 230~\mu m = 0.14~mm^2$  and  $180~\mu m \times 420~\mu m = 0.075~mm^2$  respectively for the quadrature-driven Gilbert cell (Fig. 2.13a), and for the proposed architecture (Fig. 2.13b). Including the input and output pads, the overall area of each implementation is  $0.30~mm^2$ . For measurements, the die has been glued on a PCB which provides supply and biasing through bondwires. The input and output RF signals are interfaced with Cascade Infinity GSGSG probes. The differential input signal is provided through a pair of Agilent E8257D signal generators synchronized in antiphase through an external reference. On the output side, a balun is used for differential to single-ended conversion, and the output power is measured with Agilent PXA N9030A spectrum analyzer.

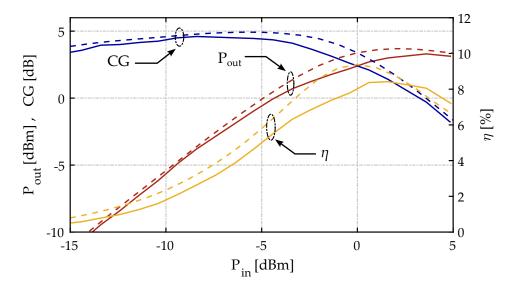

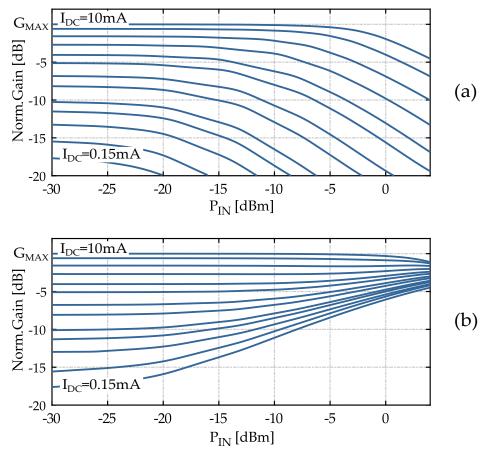

First, measurements are compared with simulations for the conventional quadrature-driven Gilbert-cell frequency doubler. Fig. 2.14 shows a sweep

Figure 2.13: Photograph of the realized frequency doublers. Quadrature driven Gilbert-cell (a) and the proposed self-adjusted reduced duty-cycle (b).

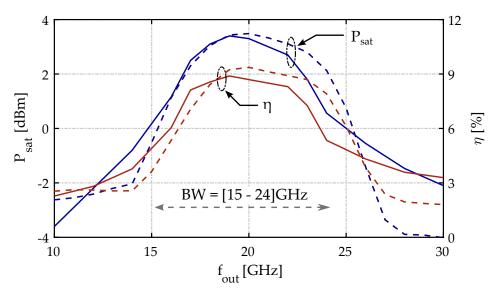

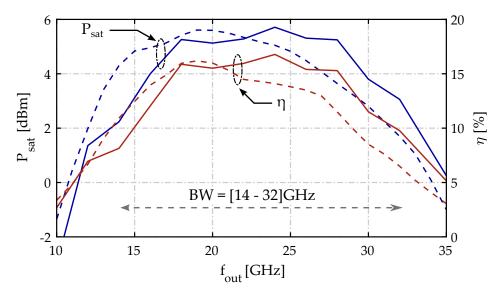

of the input power at the center output frequency  $f_{out} = 20\,\text{GHz}$ , reporting a peak conversion gain of  $5\,\text{dB}$ . The conversion gain drops to below  $0\,\text{dB}$  for  $P_{in} > 3\,\text{dBm}$ . The maximum saturated output power is  $P_{sat} = 3.3\,\text{dBm}$  and the collector efficiency  $(\eta = P_{out}/P_{DC})$  is around 8%. The measured and simulated  $P_{sat}$  and efficiency versus the output frequency are plotted in Fig. 2.15, showing a peak  $P_{sat} = 3.4\,\text{dBm}$  and a corresponding collector efficiency of 8.9%. The  $3\,\text{dB-bandwidth}$ , evaluated from the peak  $P_{sat}$ , is from 15 GHz to 24 GHz, corresponding to a 47% fractional bandwidth, with minor deviation from simulation results.

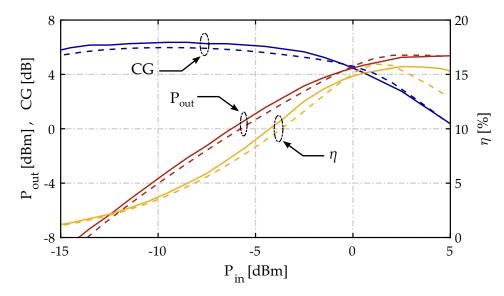

The same tests are performed for the proposed frequency doubler. Fig. 2.16 shows the results of the input power sweep at the output frequency  $f_{out} = 20\,\text{GHz}$ , reporting a peak conversion gain of 6 dB. The conversion gain drops to below 0 dB for  $P_{in} > 5\,\text{dBm}$ , after reaching  $P_{sat}$ . The saturated output power and efficiency versus output frequency are plotted in Fig. 2.17. The maximum saturated output power is  $P_{sat} = 5.7\,\text{dBm}$ , measured at  $f_{out} = 24\,\text{GHz}$ , where the power efficiency reaches 17%, almost 2 times higher than in the previous case. The 3 dB-bandwidth, still measured from the peak  $P_{sat}$ , is more than one octave, from 14 GHz to 32 GHz. The fractional bandwidth of 85% is nearly twice compared to the quadrature-driven Gilbert cell.

Figure 2.14: Quadrature-driven Gilbert Cell - Measured (solid) and simulated (dashed) output power ( $P_{out}$ ), Gain (CG) and collector efficiency ( $\eta$ ) vs input power  $P_{in}$  @  $f_{out}$  = 20 GHz.

Figure 2.15: Quadrature-driven Gilbert Cell - Measured (solid) and simulated (dashed) output saturated power  $(P_{sat})$ , and collector efficiency  $(\eta)$  vs frequency.

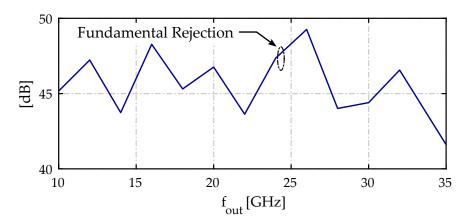

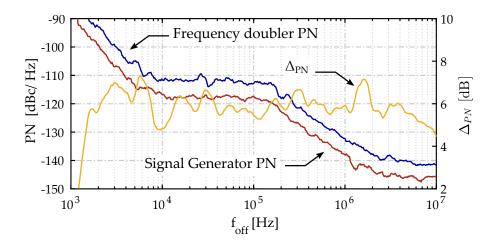

A more extensive characterization has been performed for the proposed doubler with self-adjusted duty-cycle. The measured rejection of the driving signal (i.e. the fundamental component) is reported in Fig. 2.18, proving more than 40 dB across the full operational bandwidth. Fig. 2.19 shows the phase noise measured on the input signal (provided by the Agilent E8257D generator), at the output of the frequency doubler, and the difference between the two curves,  $\Delta$ PN. The degradation of 6 dB, expected from frequency multiplication by 2, confirms the frequency doubler does not contribute to phase noise deterioration. The measured results on the two architectures are finally summarized

Figure 2.16: Proposed solution - Measured (solid) and simulated (dashed) output power  $(P_{out})$ , Gain (CG) and collector efficiency  $(\eta)$  vs input power  $P_{in} @ f_{out} = 20 \, GHz$ .

Figure 2.17: Proposed solution - Measured (solid) and simulated (dashed) output saturated power  $(P_{sat})$ , and collector efficiency  $(\eta)$  vs frequency.

in Table-2.1 and compared against previously reported frequency doublers operating in a similar frequency range. The implemented quadrature-driven Gilbert cell achieves a state-of-the-art bandwidth with good conversion gain,  $P_{\text{sat}}$  and  $\eta$  aligned with the average values of other works. The new proposed architecture highlights a remarkable improvement of the operating (fractional) bandwidth, except for [19] which lacks in terms of conversion gain and  $P_{\text{sat}}$ . This frequency doubler also demonstrates  $P_{\text{sat}}$  and efficiency  $(\eta)$  comparable or better than most of the previous works. It is worth noticing that the supply voltage of the presented doublers is 1.5 V, while the best efficiency in [17] [30] is achieved with the benefit of a remarkably higher supply, 2.5 V, which makes

the voltage headroom required to keep the stacked transistors in active region less relevant.

Figure 2.18: Proposed solution - Measured fundamental harmonic rejection vs frequency.

Figure 2.19: Proposed solution - Measured phase noise of the frequency doubler @  $f_{out} = 20\,\text{GHz}$  vs measured phase noise of the input signal generator.

Table 2.1: Performance summary and comparison table.

| [35]                                                                | m 55 nm<br>CMOS | 0 20.7-29.3     | 35     | -8.8            | -8.8                   | 1.40            | >38                  | 2 9.6 / 1.2                                     | 77.0 |

|---------------------------------------------------------------------|-----------------|-----------------|--------|-----------------|------------------------|-----------------|----------------------|-------------------------------------------------|------|

| [34]                                                                | 0.18 μm<br>SiGe | 26-40           | 43     | -4              | 5.0                    | 2.0             | 14                   | 66 / 2                                          | 0    |

| [33]                                                                | 0.15 μm<br>GaAs | 37 - 43         | 15     | 6.0             | 2.0                    | 2.1             | 9                    | 86 / 2                                          | 1    |

| [32]                                                                | 0.11 µm<br>CMOS | 21.8 - 25.8     | 17     | -4.2            | 0                      | 16.6            | 68                   | 6 / 1.2                                         | Ę    |

| [31]                                                                | 0.13 µm<br>SiGe | 27 - 41         | 42     | 19.8            | 8.0                    | 18.0            | 26                   | 32 / 1.6, 2                                     | 700  |

| [30]                                                                | 0.13 µm<br>SiGe | 22-36           | 50     | 21              | 11.9                   | 27.4            | 32                   | 43.1 / 2.5                                      | 0,0  |

| [25]                                                                | 90 nm<br>CMOS   | 40 - 49         | 20.3   | -1.6            | -1.6                   | 16.             | >25                  | 20 / 1.2                                        | (    |

| [19]                                                                | 0.18 μm<br>CMOS | 15-36           | 06     | -10.2           | -5.2                   | 2.7             | 33                   | 11 / 1                                          | c    |

| [18]                                                                | 65 nm<br>CMOS   | 23 - ,25        | 8.3    | 5               | 5.0                    | 6.6             | 44                   | 31 / -                                          | 2    |

| [17]                                                                | 0.13 µm<br>SiGe | 25 - ,40        | 47     | 14              | 13.0                   | 22.9            | >35                  | 87 / 2.5                                        |      |

| This Work $\parallel$ This Work Reduced- $\delta$ $\mid$ 90°-driven | 0.13 µm<br>SiGe | 15-24           | 47     | 4               | 3.4                    | 8.9             | /                    | 25 / 1.5                                        | 000  |

| This Work This Work Reduced-5 90°-driven                            | 0.13 µm<br>SiGe | 14-32           | 85     | 9               | 2.7                    | 17.0            | >40                  | 21 / 1.5                                        | 000  |

|                                                                     | Technology      | Frequency [GHz] | BW [%] | Conv. Gain [dB] | P <sub>sat</sub> [dBm] | Peak $\eta$ [%] | Fund. Rejection [dB] | $P_{\rm DC}/V_{ m SUP} \left[ { m mW/V}  ight]$ | L    |

## 2.3 D-Band Frequency Doubler

Considering the potential for wide bandwidth with enhanced conversion gain, this section investigates the implementation of the proposed architecture in D-band. With the operation frequency above  $100\,\mathrm{GHz}$ , pushed close to the technology limit ( $f_{max}$ ), the major challenge is how to manage the intrinsic phase shift introduced by device parasitic and interconnections of a non-negligible length compared to the signal wavelength. A circuit topology is presented and implemented in a 55 nm BiCMOS technology. From experimental results, the chip delivers a peak output power of 6.5 dBm at 148 GHz with 7.4 % power conversion efficiency and 8 dB of conversion gain. The -3dB bandwidth is from 125 GHz to 170 GHz and output power remains greater than 0 dBm over the full D-band, from 110 GHz to 170 GHz.

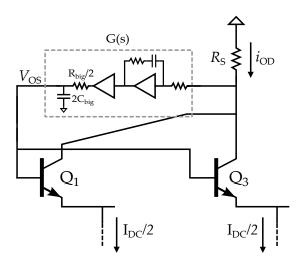

#### 2.3.1 Circuit Description and Implementation

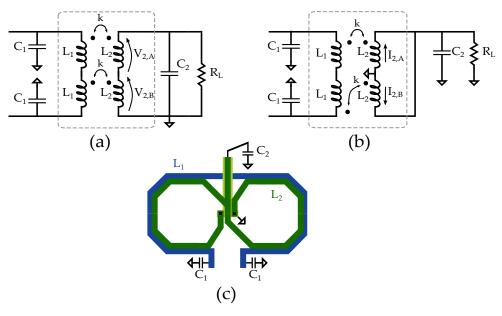

The schematic of the proposed frequency doubler is shown in Fig. 2.20. HBTs  $Q_{1,2}$  with size of 10  $\mu$ m x 0.2  $\mu$ m operate as transconductors converting the differential input voltage into a differential current  $i_{IN} = i_{LP} - i_{LN}$ . The input signal, single ended for measurement purposes, is converted to differential with an on-chip balun realized with a pair of coupled windings. The mixer switching quad is made of HBTs  $Q_3$ - $Q_6$ , with drawn area of 6  $\mu$ m x 0.2  $\mu$ m. The parasitic capacitance at the output of the switching quad is resonated by inductors  $L_p$ , while a Marchand balun provides differential to single ended conversion and scales the 50  $\Omega$  off-chip termination to a 80  $\Omega$  differential load resistance for the mixer, optimal to maximize the output power. The circuit is supplied with a  $V_{CC}$  of 2 V and draws a DC current  $I_{CC} = 30 \,\text{mA}$  when driven into saturation, at an input power of 0 dBm. As discussed in the previous section, the average (DC component) of the differential output current  $(i_{O,P} - i_{O,N})$  is nulled by a lowfrequency feedback loop, drawn in grey in Fig. 2.20, which sets a differential bias voltage  $(V_{OS})$  to the base of  $Q_3$ - $Q_6$ , reducing the switching-quad duty-cycle. The differential DC component is sensed by resistors  $R_{\text{sense}} = 5.5 \Omega$  in series with inductors  $L_p$ . To not impair the quality factor of the load resonator, and avoid performance penalty,  $R_{\text{sense}}$  are shunted by capacitors  $C_{\text{big}} = 1.5 \text{ pF}$ ., large enough to be considered a short circuit in D-band. The error voltage across the sense resistors is amplified by a fully differential OTA. The output voltage of the OTA,  $V_{OS}$ , biases the bases of the switching quad via resistors  $R_{big} = 1 \text{ k}\Omega$ . The OTA is made of two gain stages allowing to reach a low frequency loop gain of 40 dB. The stability is ensured by Miller compensation which also limits the loop bandwidth to  $200 \,\mathrm{MHz}$ . The OTA draws  $250 \,\mu\mathrm{A}$  from the  $2 \,\mathrm{V}$  supply. The overall power consumption of the low frequency biasing loop is 3 mW (500 μW consumed by the OTA and 2.5 mW due to the 80 mV DC drop across  $R_{\text{sense}}$ ) and represents only 5% of the overall doubler power consumption.

Figure 2.20: Schematic of the proposed frequency doubler.

For maximum  $2^{nd}$  harmonic conversion gain, the current entering the common emitter node of the switching quad  $(i_{I2,P} - i_{I2,P})$  must be in phase with the voltage driving the base of  $Q_3$ - $Q_6$  ( $V_{LO}$  in Fig. 2.20). At operation frequency far below the transistors cut-off frequency, as in the previous section, this condition is achieved by feeding the base of  $Q_3$ - $Q_6$  with the same voltage that drives the common emitter transconductors,  $Q_1$ ,  $Q_2$ . As frequency approaches the technology  $f_t/f_{max}$ , this straightforward implementation is no longer viable, because of the non-negligible phase shift introduced by transistors parasitic and the delay of interconnections. As an example, the extrinsic HBTs base resistance,  $r_{bb}$ , forms a low-pass filter with the base-to-emitter capacitance,  $c_{\pi}$ , with an associated pole at about 140 GHz in the adopted technology. With a 75 GHz frequency of the input signal, the pole delays the effective voltage at the internal base of  $Q_3$ - $Q_6$  by roughly  $30^\circ$ . Moreover, while at low frequency the common-emitter transconductors are connected directly to the switching

Figure 2.21: Frequency doubler conversion gain versus TL<sub>1</sub> length.

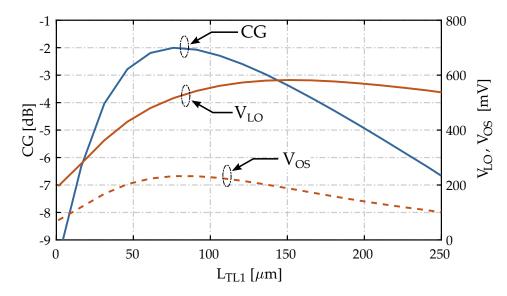

quad, the output resistance of  $Q_1$ ,  $Q_2$  at high frequency is drastically reduced, suggesting the introduction of an interstage matching network to rise the signal injection into the switching quad and increase the conversion gain. Looking again at Fig. 2.20, in the proposed frequency doubler the current provided by Q<sub>1</sub>, Q<sub>2</sub> is injected into the switching quad through a transmission line  $(TL_1+TL_2)$  and the voltage  $V_{LO}$  that drives the base of  $Q_3-Q_6$  is extracted from an intermediate tap. The first section of the line, TL<sub>1</sub>, has a dual purpose: first, together with the stray capacitances of  $Q_3$ - $Q_6$ ,  $TL_1$  provides step-up transformation of the impedance at the emitters of the switching quad, rising the amplitude of the voltage V<sub>LO</sub> thus leading to a better current commutation of the switching quad. Second, TL<sub>1</sub> compensates the phase shift introduced by parasitics of Q<sub>3</sub>-Q<sub>6</sub> by introducing a delay between the current which is finally entering into the switching quad and  $V_{LO}$ . To gain insight, Fig. 2.21 plots the current conversion gain  $\left(CG = \frac{(i_{O,P} - i_{O,N})|_{2fin}}{i_{I2,P} - i_{I2,N}}\right)$ , the amplitude of  $V_{LO}$  and the bias voltage produced by the OTA, V<sub>OS</sub>, versus the length of TL<sub>1</sub> (L<sub>TL1</sub>) when the multiplier is driven at 0 dBm input power. The amplitude of V<sub>LO</sub> rises with the length of TL<sub>1</sub>, reaching the maximum of 600 mV for  $L_{TL1} = 150 \,\mu m$ . On the other hand, the CG peaks to -2 dB at  $L_{TL1} = 75 \mu m$ , when the phase delay is optimally compensated, despite a V<sub>LO</sub> slightly below its maximum. The bias voltage  $V_{OS}$  is also maximized for  $L_{TL1} = 75 \mu m$ , confirming that at this length of TL<sub>1</sub> the duty-cycle of the switching quad is minimized. TL<sub>2</sub> provides conjugate matching to the output impedance of  $Q_1$ ,  $Q_2$  further increasing the conversion gain. Fig. 2.22 plots the same quantities of Fig. 2.21 versus the length of TL<sub>2</sub>  $(L_{TL2}).~V_{LO}$  rises close to 1~V and the  $\left(CG = \frac{(i_{O,P} - i_{O,N})|_{2fin}}{i_{I,P} - i_{I,N}}\right)$  increases from -2 dB to roughly  $0 \, dB$  at  $L_{TL2} = 300 \, \mu m$ . Tlines  $TL_1$  and  $TL_2$  are realized as a shielded coplanar structure with the signal in the topmost metal (M9) and the coplanar ground on the second topmost metal (M8). The characteristic impedance is

Figure 2.22: Frequency doubler conversion gain versus TL<sub>2</sub> length.

$65\,\Omega$  with a quality factor  $\approx$  25.  $TL_1$  and  $TL_2$  are also easily laid without additional interconnections that would add parasitic elements in D-band.

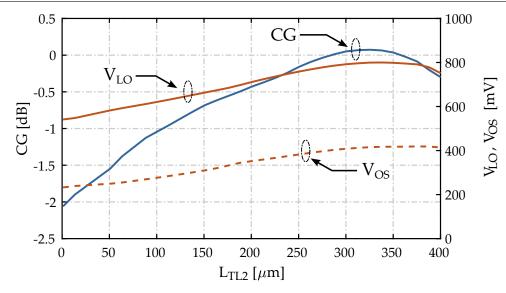

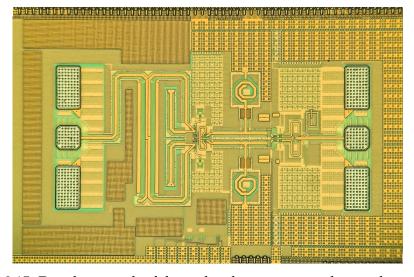

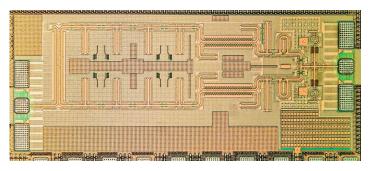

The frequency doubler is realized in STM BiCMOS 55 nm technology. The chip photograph is reported in Fig. 2.23a, with core area  $390 \times 250 \, \mu m^2$  excluding GSG pads. Not considering input and output baluns, only required for measurements, the area of the frequency doubler is  $200 \times 140 \, \mu m^2$ . The layout of half of the core is highlighted in Fig. 2.23b.  $TL_2$  is folded on top of  $Q_1,Q_2$  while  $TL_1$  is wrapped around the switching quad, allowing a straight connection to the base and emitter terminals of  $Q_3$ - $Q_6$ .

Figure 2.23: Photograph of the realized frequency doubler.

#### 2.3.2 Experimental Results

The chip is measured with direct die probing. The input signal is provided by an Agilent E8257D signal generator to cover the 50 - 67 GHz band and with an OML N5256BW12 frequency extension module for the 67 - 85 GHz band. Output power at twice the input frequency is measured with an ELVA-1 DPM-06 D-band power meter, while the fundamental leakage component is characterized with harmonic mixers and a PXA N9030A spectrum analyzer.

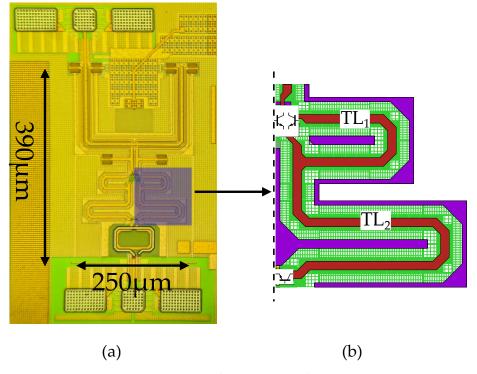

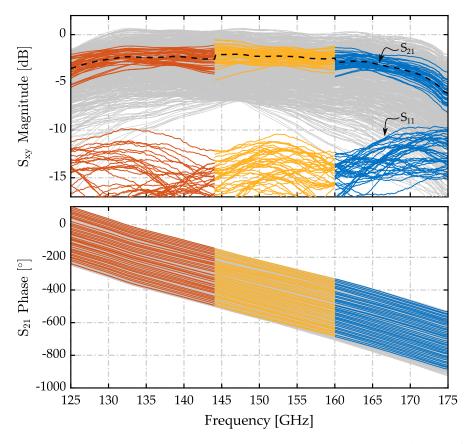

Fig. 2.24 shows the measured and simulated output power,  $P_{sat}$ , and collector efficiency ( $\eta = P_{sat}/P_{DC}$ ).  $P_{sat}$  peaks to 6.5 dBm at 148 GHz and remains within -3 dB from 125 GHz to at least 170 GHz, the upper limit of the measurement setup, corresponding to a fractional bandwidth larger than of 31%.  $P_{sat}$  is above 0 dBm over the full D-band [110 - 170] GHz. Measurements are well aligned with simulations, which predict a 3 dB bandwidth of [125 - 175] GHz and a remarkable  $P_{sat} > 0$  dBm bandwidth [110 - 200] GHz, corresponding to a 60% fractional bandwidth.

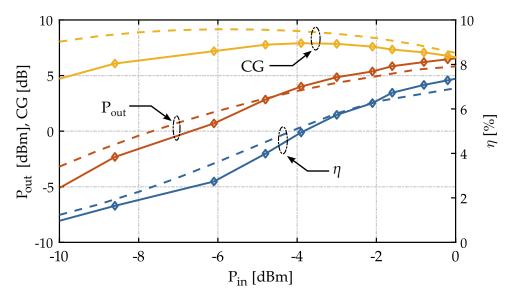

Fig. 2.25 shows the  $2^{nd}$  harmonic conversion gain (CG),  $\eta$  and output power ( $P_{out}$ ) at input frequency of 150 GHz versus the input power ( $P_{in}$ ). The CG peaks to 8.5 dB at  $P_{in}$  = -4 dBm. With  $P_{in}$  = 0 dBm, used for the measurements in Fig. 2.24, the conversion gain penalty is <1 dB.

Figure 2.24: Measured (solid) and simulated (dashed) output saturated power ( $P_{sat}$ ), and collector efficiency ( $\eta$ ) vs frequency.

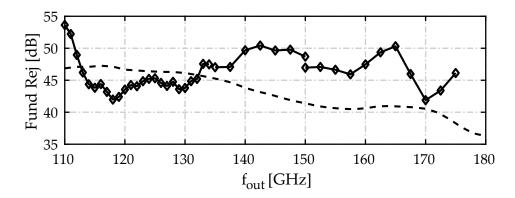

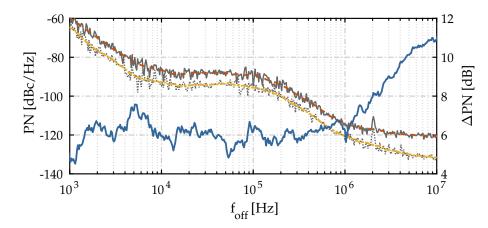

The fundamental rejection of the input signal is measured at  $P_{\rm in}=0$  dBm. The unavoidable coupling between input and output probes has been characterized and de-embedded from the measurement. Results are reported in Fig. 2.26, showing a fundamental rejection above 40 dB over the entire bandwidth. Figure 2.27 shows the phase noise profile at the doubler output, compared to the one of the input source, as well as the expected phase noise degradation of 6 dB. The higher noise floor at frequency offsets above 1 MHz may be limited

by the D-band downconverter in the measurement setup.

The measured results are finally summarized in Table 2.2 and compared against previously reported frequency doublers operating in a similar frequency range. The implemented frequency doubler displays high  $P_{sat}$  and CG simultaneously and the highest rejection of the fundamental signal. The -3 dB fractional bandwidth of 31% is also the largest reported in a silicon-based technology. [36], in a compound semiconductor technology, demonstrates a wider bandwidth but with significantly lower  $P_{sat}$  and a high conversion loss.

Figure 2.25: Measured output power  $(P_{out})$ , Conversion Gain (CG) and collector efficiency  $(\eta)$  vs input power  $P_{in} @ f_{out} = 150 \, \text{GHz}$ .

Figure 2.26: Measured (solid) and post-layout simulated (dashed) fundamental harmonic rejection vs frequency.

Figure 2.27: Proposed solution - Measured phase noise of the frequency doubler @  $f_{out} = 150\,\text{GHz}$  vs measured phase noise of the input source.

Table 2.2: Performance summary and comparison table.

|             |                           | -         | 1         |           |              |            | 7         | [7]              |            |

|-------------|---------------------------|-----------|-----------|-----------|--------------|------------|-----------|------------------|------------|

| Ihis        | This Work                 | [14]      | [37]      | [38]      | [39]         | [40]       | [41]      | [42]             | [36]       |

| 55          | 55 nm                     | 55 nm     | 0.13 µm   | 90 nm     | 0.13 µm      | 22 nm      | 55 nm     | 0.1 µm           |            |

| S           | SiGe                      | SiGe      | SiGe      | SiGe      | SiGe         | FDSOI      | CMOS      | GaAs             | IIIGaAS    |

| Red<br>Gilb | Reduced-δ<br>Gilbert-cell | Push-Push | Push-Push | Push-Push | Push-Push    | Push-Push  | Push-Push | Common<br>Source | Push-Push  |

| 125         | 125 - 170                 | 116 - 144 | 138 - 170 | 128 - 140 | 166 - 182    | 125 - 145  | 112 - 125 | 110-130          | 100 - 208  |

|             | 31                        | 22        | 21        | 6         | 6            | 15         | 11        | 17               | 75         |

|             | 6.5                       | 4.3       | 5.6       | 9.4       | 4.5          | 4.1        | 7.8       | rC               | 1.4        |

|             | 8                         | 9.3       | 4.9       | 9-        | <sub>C</sub> | -7.6       | -2.2      | 2                | -12.6      |

|             | 7.4                       | 7.2       | 10.1      | 12.1      | 8.4          | 10.4       | 8.9       | 4.9              | 9.6        |

|             | 6.3                       | 6.4       | 8.9       | 0>        | 5.8          | 0>         | 0>        | 1.8              | 0>         |

|             | >40                       | >32       | 37        | 20        | 1            | 15         | 20        | 25               | 1          |

| 9           | 60 / 2                    | 37.4 / 2  | 36 / 1.5  | 72 / 1.9  | 33.5 / 2.5   | 24.7 / 0.8 | 88 / 1.2  | 65 / 1           | 14.4 / 0.8 |

# 2.4 Chapter Summary

This chapter presented a simple technique to enhance the overall performance of frequency doublers based on Gilbert-cell mixers. The conversion gain is improved by applying a DC offset to the switching-quad transistors, such that the duty-cycle is reduced and the output current assumes an almost square-wave shape at twice the input frequency. The DC offset is self-adjusted by a low-frequency feedback loop to maintain optimal performance against input power and PVT variations. Compared to the conventional architecture made of a Gilbert-cell driven by quadrature signals, the proposed technique yields wider bandwidth (not requiring a 90° phase shifter), enhanced gain and robustness to impairments.

The claimed advantages are supported by simulations and verified experimentally on prototypes of the conventional quadrature-driven mixer and of the proposed architecture in the same technology for K-band operation. Compared to previously reported frequency doublers, the presented solution achieved state-of the-art output power and efficiency, at low supply voltage, with a remarkable advantage on the operation bandwidth.

The same operating principle is proven in D-band by experiments on a test chip in  $55\,\mathrm{nm}$  SiGe BiCMOS. A transmission line network that compensates the phase shift introduced by transistors parasitic is proposed to generate the LO signal and drive the mixer optimally. Compared to previous works, the doubler displays the widest operation bandwidth and the highest suppression of the fundamental component, with high  $P_{\text{sat}}$  and conversion gain, simultaneously.

# Phase Shifters

As seen in the Introduction chapter, active phased-arrays need to coherently combine the transmitted and received signals at each antenna element in order to perform beamforming and beam steering. Even though the ideal solution would involve true time delay, we have seen that this is only possible in digital or hybrid beamforming systems, as the required delay range increases with the array size. On the other hand, at D-band, although the transceivers may support wide frequency range, the fractional channel (instantaneous) bandwidth is, in most of the applications, limited, relaxing the issues of beam squinting [4] and inter-symbol interference [5]. Therefore, phase shifter (PS) can be used in place of true time delay in fully analog beamforming solutions with little penalty.

The programmable phase shifter remains a crucial component: on the transmitter side it precedes the power amplifier, and achieving a high output power at 1 dB gain compression (OP<sub>1dB</sub>) is desirable to relax PA requirements and improve the power efficiency. Conversely, in the receiver, the PS follows the low-noise amplifier, and both low noise and high linearity are desirable not to compromise the dynamic range. A relatively high gain compression point is necessary in radar sensors, to make the front-end resilient against close-by reflections, but also in wireless communications to support spectrally efficient high-order modulations [43]. Phase shifters can be implemented with passive circuits, based on programmable filters [44], reflective type structures [45] or switched delay paths [46], [47], offering high linearity at the expense of limited phase resolution, high losses, bandwidth limitation and large area occupation. Conversely, active phase shifters, built around the vector interpolation principle [48]–[55], can easily cover the 360° circle with high phase resolution and a compact area, but suffer from limited linearity. The latter can be improved by increasing power consumption, but penalizing the system efficiency. The linearity issue arises from the need for variable gain amplifiers (VGAs) which are required to operate across a relatively high dynamic range of gain control.

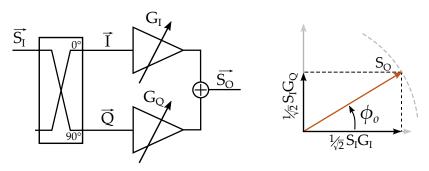

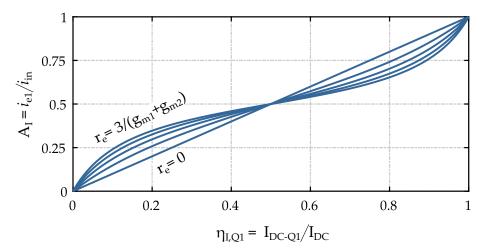

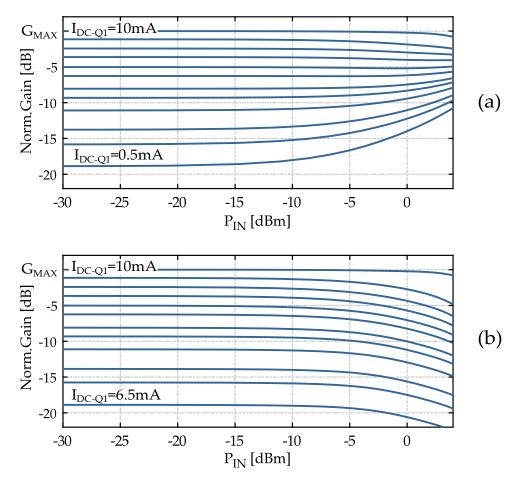

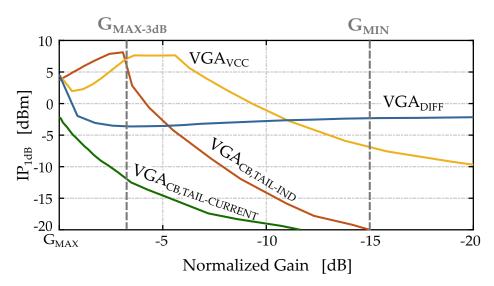

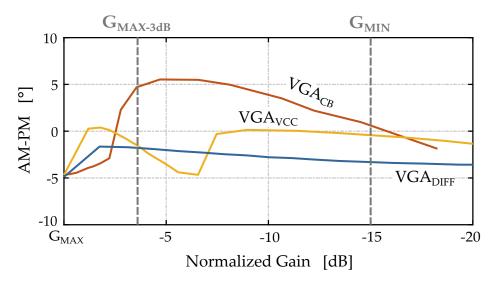

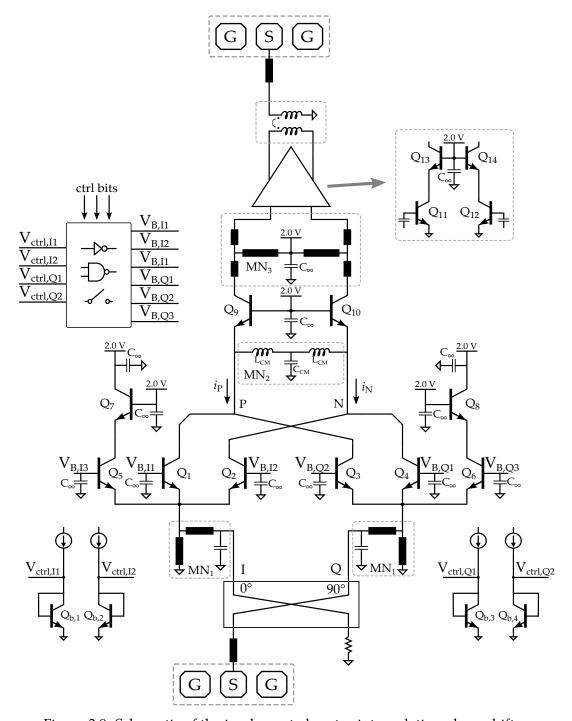

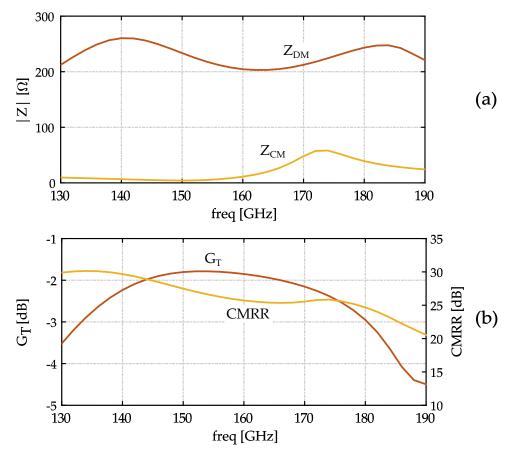

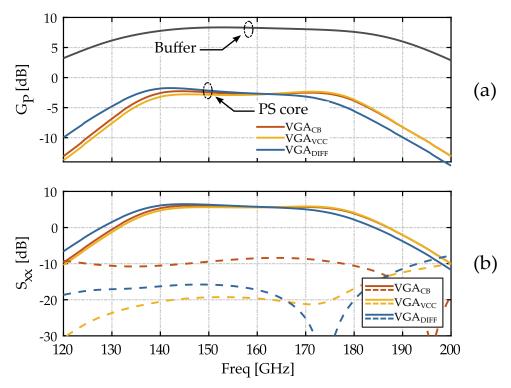

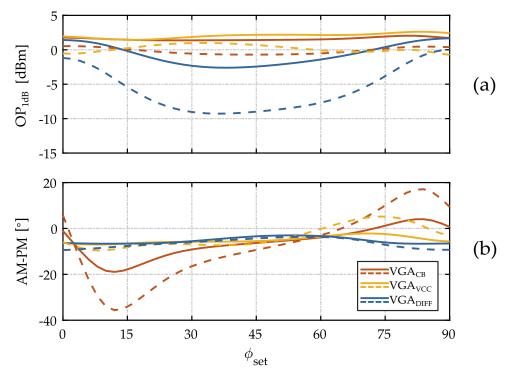

This first section of this chapter focuses on the vector interpolation phase shifter, investigating the impact of VGA impairments on the vector-interpolated