# Doctoral Dissertation Doctoral Program in Computer and Control Engineering (29<sup>th</sup>cycle)

# New techniques for functional testing of microprocessor based systems

By

### Riccardo Cantoro

\*\*\*\*\*

### **Supervisor(s):**

Prof. Ernesto Sanchez

### **Doctoral Examination Committee:**

Dr. Maksim Jenihhin, Referee, Tallinn University of Technology

Prof. Dr. Mario Schölzel, Referee, Universität Potsdam

Prof. Paolo Bernardi, Politecnico di Torino

Prof. Alberto Bosio, LIRMM

Prof. Michele Portolan, Laboratoire TIMA

Politecnico di Torino 2017

### **Declaration**

Riccardo Cantoro 2017

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Doctoral School of Politecnico di Torino (ScuDo).

### Acknowledgements

I would like to acknowledge all the people who made the accomplishment of this thesis possible by guiding, supporting and encouraging me.

My thanks goes especially to Ernesto Sanchez, Paolo Bernardi and Matteo Sonza Reorda. I feel very grateful for the privilege of working with them and I hope our collaboration will continue.

I also acknowledge all the other people I have worked with in the Politecnico di Torino research group. A special thanks goes to Davide Piumatti, whose works has been fundamental to the experimental part of this thesis.

I acknowledge all the researchers I have been in contact with over these years. Thanks to the fruitful collaboration and the time spent together in conferences and meetings.

Finally, I would also like to thank Katia, my family and my friends for their constant encouragement.

### **Abstract**

Electronic devices may be affected by failures, for example due to physical defects. These defects may be introduced during the manufacturing process, as well as during the normal operating life of the device due to aging. How to detect all these defects is not a trivial task, especially in complex systems such as processor cores. Nevertheless, safety-critical applications do not tolerate failures, this is the reason why testing such devices is needed so to guarantee a correct behavior at any time. Moreover, testing is a key parameter for assessing the quality of a manufactured product.

Consolidated testing techniques are based on special Design for Testability (DfT) features added in the original design to facilitate test effectiveness. Design, integration, and usage of the available DfT for testing purposes are fully supported by commercial EDA tools, hence approaches based on DfT are the standard solutions adopted by silicon vendors for testing their devices. Tests exploiting the available DfT such as scan-chains manipulate the internal state of the system, differently to the normal functional mode, passing through unreachable configurations. Alternative solutions that do not violate such functional mode are defined as functional tests.

In microprocessor based systems, functional testing techniques include software-based self-test (SBST), i.e., a piece of software (referred to as test program) which is uploaded in the system available memory and executed, with the purpose of exciting a specific part of the system and observing the effects of possible defects affecting it. SBST has been widely-studies by the research community for years, but its adoption by the industry is quite recent.

My research activities have been mainly focused on the industrial perspective of SBST. The problem of providing an effective development flow and guidelines for integrating SBST in the available operating systems have been tackled and results have been provided on microprocessor based systems for the automotive domain.

Remarkably, new algorithms have been also introduced with respect to state-of-theart approaches, which can be systematically implemented to enrich SBST suites of test programs for modern microprocessor based systems. The proposed development flow and algorithms are being currently employed in real electronic control units for automotive products.

Moreover, a special hardware infrastructure purposely embedded in modern devices for interconnecting the numerous on-board instruments has been interest of my research as well. This solution is known as reconfigurable scan networks (RSNs) and its practical adoption is growing fast as new standards have been created. Test and diagnosis methodologies have been proposed targeting specific RSN features, aimed at checking whether the reconfigurability of such networks has not been corrupted by defects and, in this case, at identifying the defective elements of the network. The contribution of my work in this field has also been included in the first suite of public-domain benchmark networks.

# **Contents**

| Li | List of Figures x |               |                               |     |    |  |

|----|-------------------|---------------|-------------------------------|-----|----|--|

| Li | st of '           | <b>Fables</b> |                               | xi  | iv |  |

| In | trodu             | ction         |                               |     | 1  |  |

|    | Prob              | olem Foi      | rmulation                     |     | 4  |  |

| Ι  | Sof               | tware-        | -Based Self-Test Enhancements |     | 5  |  |

| 1  | Bac               | kgroun        | d                             |     | 7  |  |

|    | 1.1               | Basic         | Concepts                      |     | 8  |  |

|    | 1.2               | Softwa        | are-Based Self-Test (SBST)    | . 1 | 0  |  |

|    | 1.3               | Fault (       | Grading Process for SBST      | . 1 | 4  |  |

|    | 1.4               | Observ        | vability Solutions            | . 1 | 5  |  |

|    |                   | 1.4.1         | Module-Level                  | . 1 | 6  |  |

|    |                   | 1.4.2         | Processor-Level               | . 1 | 17 |  |

|    |                   | 1.4.3         | System Bus                    | . 1 | 17 |  |

|    |                   | 1.4.4         | Memory Content                | . 1 | 9  |  |

|    |                   | 1.4.5         | Performance Counters          | . 2 | 20 |  |

|    | 1.5               | Genera        | ation Flows                   | . 2 | 21 |  |

|    |                   | 151           | ATDC based                    | 7   | 2  |  |

| Contents |  | vii |

|----------|--|-----|

|          |  |     |

|   |     | 1.5.2   | Deterministic                           | 22 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 1.5.3   | Feedback-based                          | 23 |

| 2 | SBS | T Algoi | rithms                                  | 26 |

|   | 2.1 | Decod   | e Unit                                  | 27 |

|   |     | 2.1.1   | Architectural Overview                  | 28 |

|   |     | 2.1.2   | Instruction Set Analysis                | 29 |

|   |     | 2.1.3   | Signature Mechanisms                    | 31 |

|   |     | 2.1.4   | Proposed Test Strategies                | 35 |

|   |     | 2.1.5   | Experimental Results                    | 40 |

|   | 2.2 | Regist  | er Forwarding and Pipeline Interlocking | 41 |

|   |     | 2.2.1   | Architectural Overview                  | 42 |

|   |     | 2.2.2   | Proposed Test Strategies                | 45 |

|   |     | 2.2.3   | Experimental Results                    | 52 |

|   | 2.3 | Dual-I  | ssue Processors                         | 53 |

|   |     | 2.3.1   | Architectural Overview                  | 54 |

|   |     | 2.3.2   | Scheduling Issues                       | 56 |

|   |     | 2.3.3   | Duplicated Computational Modules        | 57 |

|   |     | 2.3.4   | Multi-Port Register File                | 59 |

|   |     | 2.3.5   | Feed-Forward Paths                      | 65 |

|   |     | 2.3.6   | Pipeline Interlocking                   | 70 |

|   |     | 2.3.7   | Instruction Prefetch Buffer             | 75 |

|   |     | 2.3.8   | Case Studies                            | 78 |

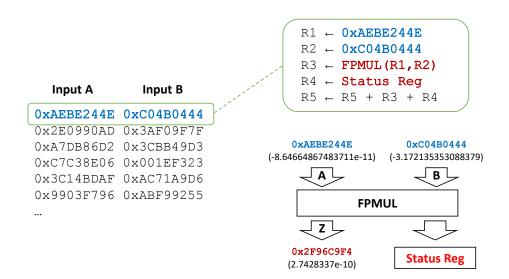

|   | 2.4 | Floatir | ng Point Unit                           | 83 |

|   |     | 2.4.1   | Architectural Overview                  | 84 |

|   |     | 2.4.2   | Proposed Test Strategies                | 85 |

|   |     | 2.4.3   | Experimental Results                    | 88 |

| viii | Contents |

|------|----------|

|      |          |

|    | 2.5  | Chapte  | er Summary                                | 90  |

|----|------|---------|-------------------------------------------|-----|

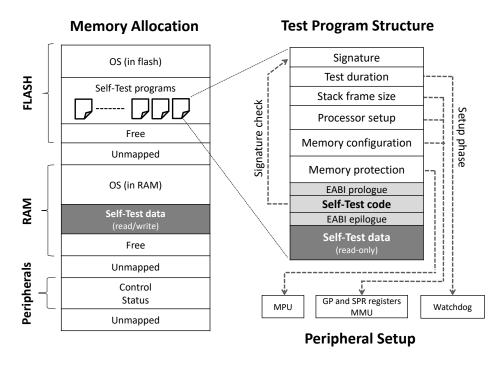

| 3  | Deve | elopmer | nt Flow for On-Line SBST                  | 91  |

|    | 3.1  | On-Lir  | ne Constraints                            | 92  |

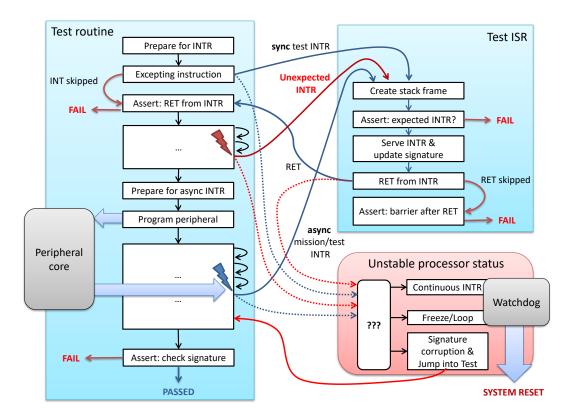

|    | 3.2  | Execut  | tion Management                           | 93  |

|    |      | 3.2.1   | Test Encapsulation                        | 94  |

|    |      | 3.2.2   | Context Switching to Test Procedure       | 95  |

|    |      | 3.2.3   | Interruption Management and Robustness    | 97  |

|    | 3.3  | Develo  | opment Flow                               | 99  |

|    |      | 3.3.1   | Resources Partitioning                    | 101 |

|    |      | 3.3.2   | Optimized Test Programs Generation Order  | 102 |

|    | 3.4  | Case S  | tudies                                    | 106 |

|    |      | 3.4.1   | Automotive Microprocessor                 | 106 |

|    |      | 3.4.2   | Embedded Floating-Point Unit              | 114 |

|    |      | 3.4.3   | Cumulative Results                        | 117 |

|    | 3.5  | Chapte  | er Summary                                | 119 |

| 4  | Sum  | ımarv o | f Part I                                  | 120 |

| -  | 2022 |         | <del></del>                               |     |

| II | Te   | st and  | Diagnosis of Reconfigurable Scan Networks | 122 |

| 5  | Bacl | kground | ì                                         | 124 |

|    | 5.1  | Netwo   | rk Constructs                             | 125 |

|    |      | 5.1.1   | IEEE Std 1149.1-2013                      | 125 |

|    |      | 5.1.2   | IEEE Std 1687                             | 127 |

|    |      | 5.1.3   | Example Network                           |     |

|    | 5.2  |         | d Works                                   |     |

|    | 5.3  |         | 1687 Benchmark Networks                   |     |

|    |      |         |                                           |     |

|          | •  |

|----------|----|

| Contents | 17 |

| Contonts | 11 |

|          |    |

| 6 | Test | ing     |                                         | 133 |

|---|------|---------|-----------------------------------------|-----|

|   | 6.1  | Termi   | nology and Fault Model                  | 134 |

|   |      | 6.1.1   | Configurations, Vectors, and Test Time  | 134 |

|   |      | 6.1.2   | Fault Model for Reconfigurable Modules  | 137 |

|   | 6.2  | Netwo   | ork Representation                      | 141 |

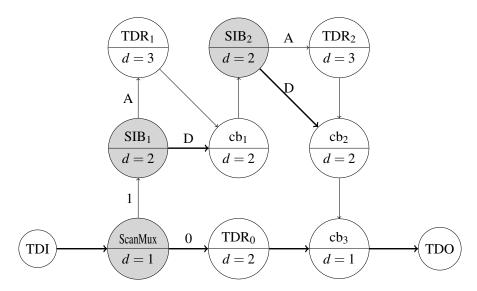

|   |      | 6.2.1   | Topology Graph                          | 142 |

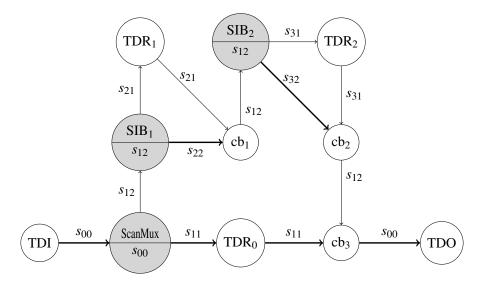

|   |      | 6.2.2   | Configuration graph                     | 143 |

|   | 6.3  | Propos  | sed Test Strategies                     | 145 |

|   |      | 6.3.1   | Optimal Approach                        | 146 |

|   |      | 6.3.2   | Enhanced Version                        | 151 |

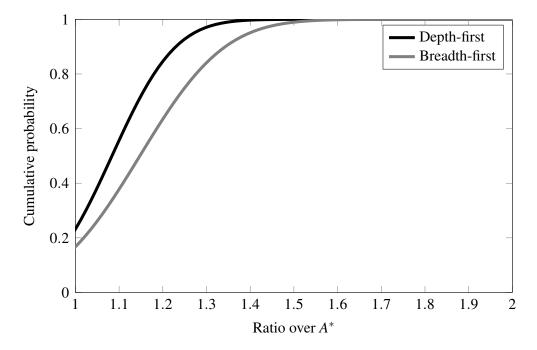

|   |      | 6.3.3   | Sub-Optimal Approaches                  | 155 |

|   | 6.4  | Experi  | imental results                         | 158 |

|   |      | 6.4.1   | Experiments with Known Benchmarks       | 159 |

|   |      | 6.4.2   | Experiments with Synthesized Benchmarks | 162 |

|   | 6.5  | Chapte  | er Summary                              | 165 |

| 7 | Dia  | gnosis  |                                         | 166 |

|   | 7.1  | Termi   | nology and Fault Model                  | 167 |

|   |      | 7.1.1   | Fault Dictionary and Fault Classes      | 168 |

|   |      | 7.1.2   | Fault Model                             | 169 |

|   | 7.2  | Propos  | sed Diagnostic Approach                 | 171 |

|   |      | 7.2.1   | Diagnostic Analysis                     | 171 |

|   |      | 7.2.2   | Generation of New Patterns              | 175 |

|   | 7.3  | Experi  | imental Results                         | 176 |

|   | 7.4  | Chapte  | er Summary                              | 179 |

| 8 | Sun  | ımary o | of Part II                              | 180 |

| X | Contents |

|---|----------|

|   |          |

| Conclusions                    | 181   |

|--------------------------------|-------|

| List of Research Contributions | . 182 |

| Future Works                   | . 184 |

| References                     | 185   |

# **List of Figures**

| 1.1 | Stuck-at fault and possible test pattern for a sample combinational circuit (a) and sequential circuit (b)                                         | 8  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Conceptual representation of a sequential circuit including a scan chain                                                                           | 9  |

| 1.3 | Conceptual representation of a pipelined microprocessor architecture and example of SBST for a stuck-at 0 fault in the Arithmetic Logic Unit (ALU) | 11 |

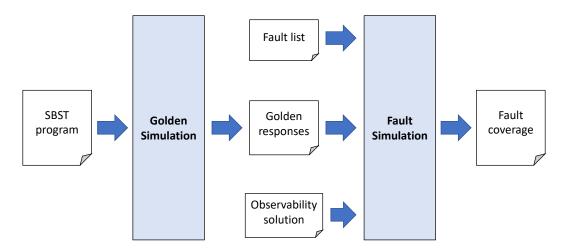

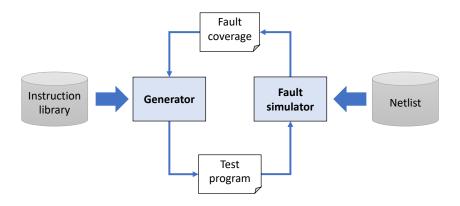

| 1.4 | Fault grading process for SBST                                                                                                                     | 14 |

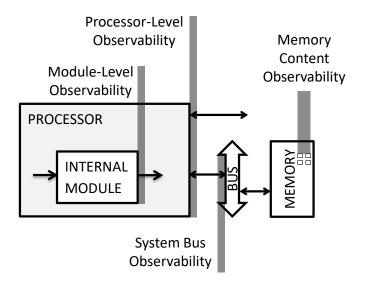

| 1.5 | Generic system under test: the observation points adopted by the techniques described in the text are highlighted                                  | 16 |

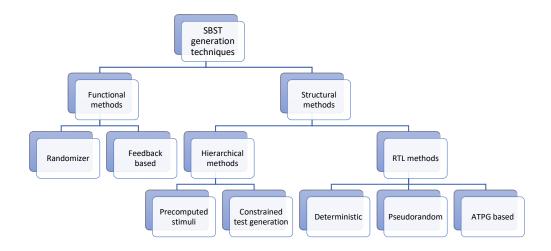

| 1.6 | Taxonomy of routine development styles for SBST, taken from [60]                                                                                   | 21 |

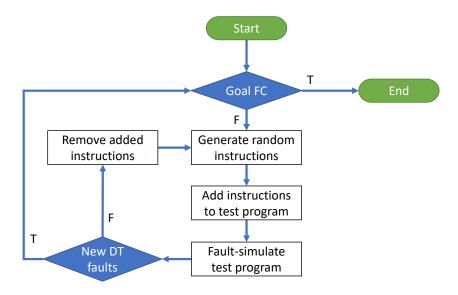

| 1.7 | Feedback-based approach based on random code generator                                                                                             | 24 |

| 1.8 | Feedback-based approach based on evolutionary engine                                                                                               | 24 |

| 2.1 | Example of signature mechanism for ALU instructions                                                                                                | 33 |

| 2.2 | Example of signature mechanism for memory instructions                                                                                             | 33 |

| 2.3 | Example of signature mechanism for execution flow related instructions                                                                             | 34 |

| 2.4 | Example of opcodes in the neighborhood of the add instruction                                                                                      | 36 |

| 2.5 | Test procedure and ISRs for breakpoint instructions                                                                                                | 39 |

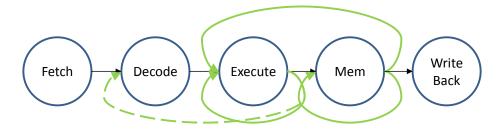

| 2.6 | Graph of the possible forwarding paths between pipeline stages                                                                                     | 43 |

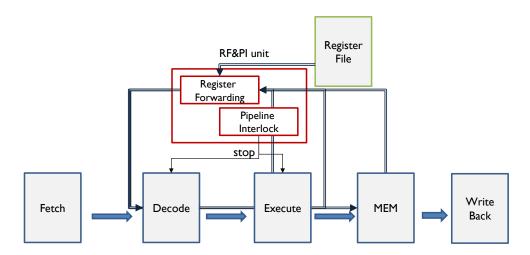

| 2.7 | The Register Forwarding and Pipeline Interlock unit and its interaction with the processor pipeline and Register File module                       | 44 |

**xii** List of Figures

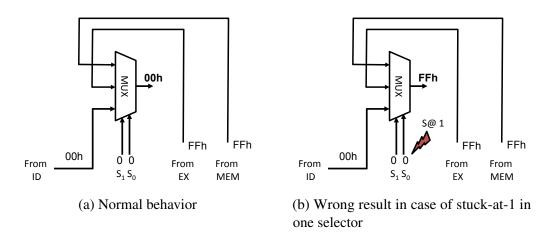

| 2.8  | Test program fragment for testing the MUX for the EXE stage                                                                                              | 47 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.9  | Vector 0 application to the MUX for the EXE stage                                                                                                        | 49 |

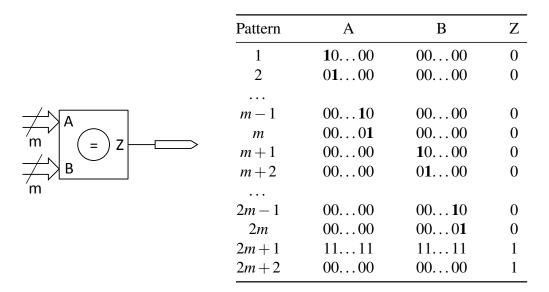

| 2.10 | Comparator schema and test patterns                                                                                                                      | 50 |

| 2.11 | Test program fragment for testing the CMP in the EXE stage                                                                                               | 51 |

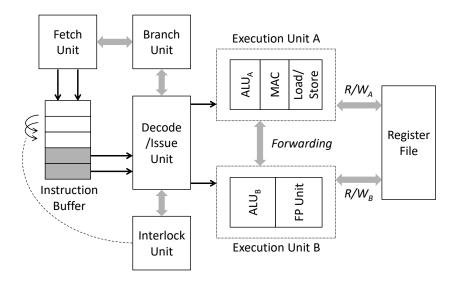

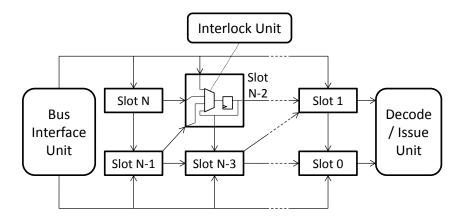

| 2.12 | Example block diagram of in-order dual issue processors                                                                                                  | 55 |

| 2.13 | Single-issue (a) and dual-issue (b) versions of a snippet procedure to test adder units                                                                  | 58 |

| 2.14 | Example of dual-issue execution of instructions that access to the register file ports in parallel                                                       | 59 |

| 2.15 | Effect of data-dependencies on the access to the register file read ports. Wrong implementation (a) and correct version by means of nop instructions (b) | 63 |

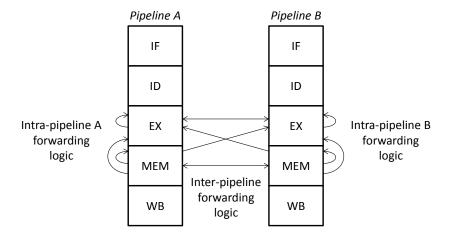

| 2.16 | Example feed-forward paths of in-order dual issue processors                                                                                             | 66 |

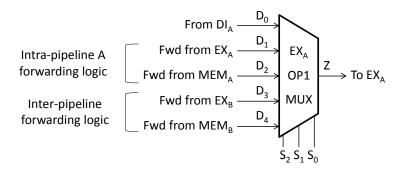

| 2.17 | Example of multiplexer feeding one of the operands of the execute stage                                                                                  | 67 |

| 2.18 | Propagation of a test pattern through feed-forward paths                                                                                                 | 68 |

| 2.19 | Test sequence that applies the pattern 0 of Table 2.6 to $EX_A$ $OP1$ $MUX$                                                                              | 69 |

| 2.20 | Example of instruction schedule on a dual-issue processor                                                                                                | 71 |

| 2.21 | Example of instruction schedule including a multi-cycle instruction                                                                                      | 72 |

| 2.22 | Test sequence that applies the first pattern of Fig. 2.22 to two CMPs involved in data-dependency check                                                  | 73 |

| 2.23 | Implementation of the test algorithm for the $EX_A$ $OP1$ CMP of an example in-order dual-issue processor with 8 registers                               | 74 |

| 2.24 | Dual-issue prefetch buffer                                                                                                                               | 76 |

| 2.25 | Test sequence that propagates a pattern through the prefetch buffer slots                                                                                | 77 |

| 2.26 | Implementation of the pipeline reset in the case studies                                                                                                 | 79 |

| 2.27 | Example of ATPG loop-based approach applied to FPU                                                                                                       | 85 |

List of Figures xiii

| 3.1 | Test program encapsulation and loading for execution phase 94                                                                                                                        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Expected and unexpected exception management scenario 98                                                                                                                             |

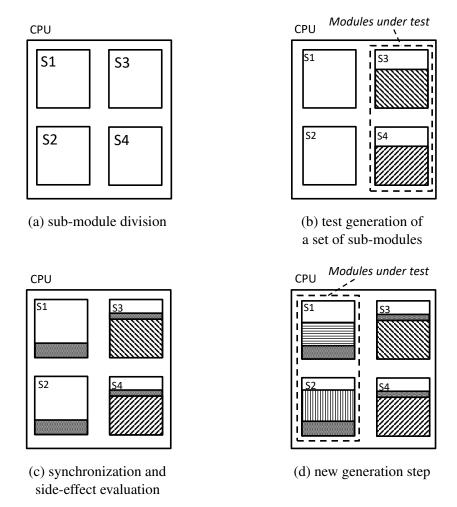

| 3.3 | Sub-module identification and visualization of the coverage figure evolution along the proposed generation steps                                                                     |

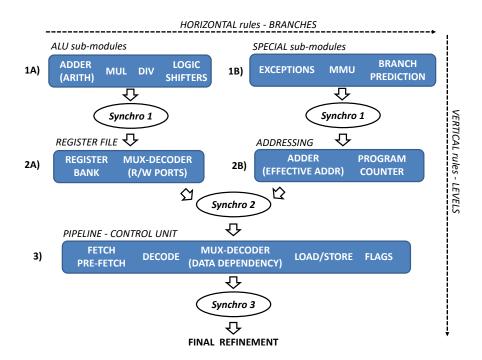

| 3.4 | Proposed test program development order for CPUs organized in levels and branches, and synchronization steps                                                                         |

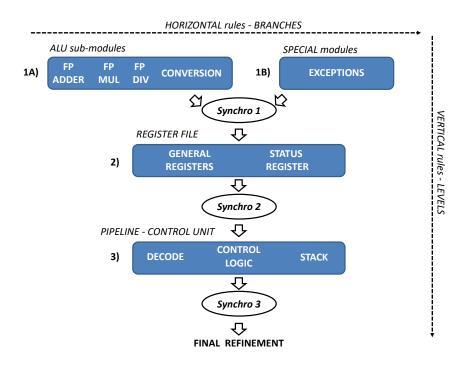

| 3.5 | Proposed test program development order for FPUs                                                                                                                                     |

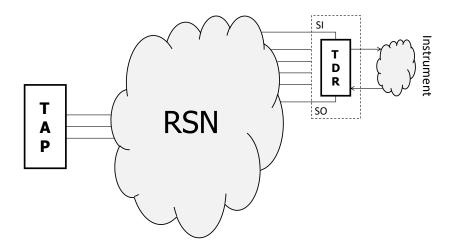

| 5.1 | Concept of Reconfigurable Scan Network (RSN)                                                                                                                                         |

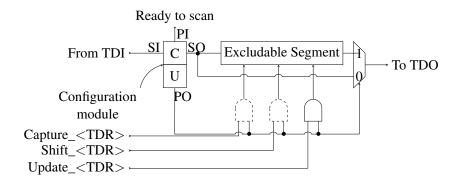

| 5.2 | Excludable TDR segment described in IEEE Std 1149.1-2013 126                                                                                                                         |

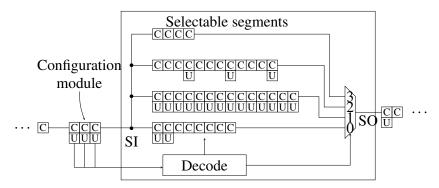

| 5.3 | Selectable TDR segments described in IEEE Std 1149.1-2013 126                                                                                                                        |

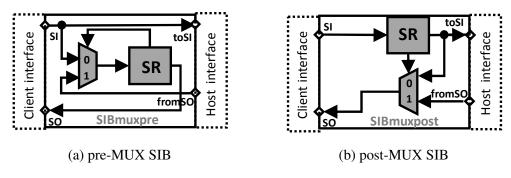

| 5.4 | Segment Insertion Bit (SIB) described in IEEE Std 1687 127                                                                                                                           |

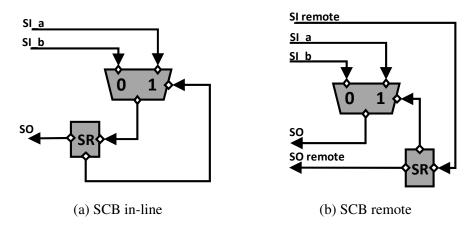

| 5.5 | ScanMux Control Bit (SCB) described in IEEE Std 1687 128                                                                                                                             |

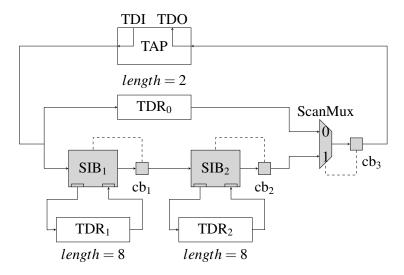

| 5.6 | Example of IEEE Std 1687 reconfigurable scan network 129                                                                                                                             |

| 6.1 | Topology graph of the example network in Fig. 5.6                                                                                                                                    |

| 6.2 | Pseudo-code of the optimal approach based on the $A^*$ algorithm 149                                                                                                                 |

| 6.3 | Topology graph of the example network in Fig. 5.6 annotated for heuristic optimization                                                                                               |

| 6.4 | Pseudo-code of the sub-optimal approach based on the depth-first algorithm                                                                                                           |

| 6.5 | Pseudo-code of the sub-optimal approach based on the breadth-first algorithm                                                                                                         |

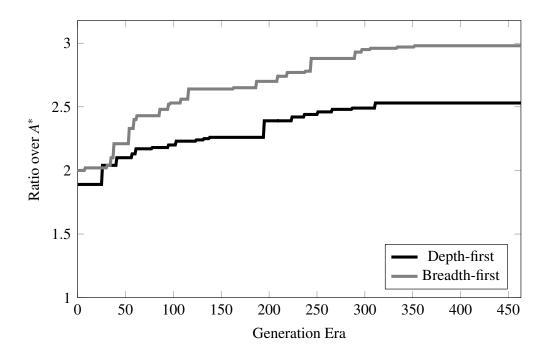

| 6.6 | Normal cumulative distribution function (CDF) of the ratio between sub-optimal approaches (depth-first in black, breadth-first in gray) and $A^*$ on the randomly generated networks |

| 6.7 | Progression in time of the maximum fitness value for the evolutionary-based experiments                                                                                              |

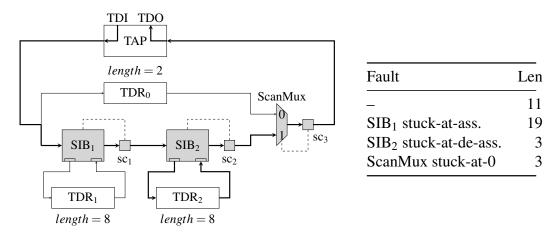

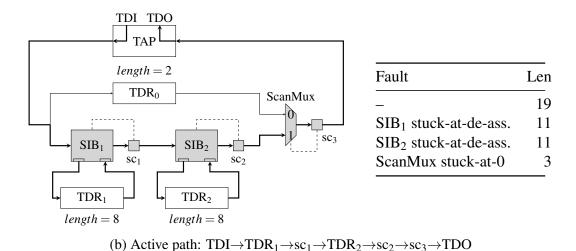

| 7.1 | Examples of active path in a RSN and related faulty path lengths 174                                                                                                                 |

| 1.1  | SBST generation techniques comparison                                                                       | 25 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Example of instruction format and bitmask                                                                   | 30 |

| 2.2  | Example list of instructions                                                                                | 30 |

| 2.3  | Operand configurations for instructions working on three registers .                                        | 38 |

| 2.4  | Incremental results of the application of the proposed approach                                             | 41 |

| 2.5  | Experimental results on random opcodes                                                                      | 41 |

| 2.6  | Test vectors for a 8-to-1 MUX                                                                               | 46 |

| 2.7  | Input values for the 3-to-1 MUX feeding the first operand input of the EXE stage in a pipelined processor   | 47 |

| 2.8  | Characteristics of the test program for the RF&PI unit                                                      | 53 |

| 2.9  | Implementation of the single-issue version of the basic test algorithm for a register file with 8 registers | 62 |

| 2.10 | Implementation of the dual-issue version of the basic test algorithm for a register file with 8 registers   | 64 |

| 2.11 | Fault simulation results on the duplicated computational modules of e200z448                                | 81 |

| 2.12 | Fault simulation results on the register file of e200z448                                                   | 81 |

| 2.13 | Fault simulation results on the feed-forward paths, interlocking logic, and prefetch buffer of e200z448     | 83 |

| 2.14 | Experimental results on e200z448 and e200z425                                                               | 83 |

| 2.15 | Proposed special operations to detect faults related to erroneous                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------|

|      | operations                                                                                                                             |

| 2.16 | Experimental results on the FPU                                                                                                        |

| 2.17 | Duration and code size of test programs for the embedded FPU 90                                                                        |

| 3.1  | SBST strategies used along the generation process for the automotive microprocessor                                                    |

| 3.2  | Coverage evolution along the development flow for the automotive microprocessor                                                        |

| 3.3  | Number of evaluated test programs, duration, and code size along development flow for the automotive microprocessor                    |

| 3.4  | Fault simulation time comparison for approaches without and with synchronization                                                       |

| 3.5  | SBST strategies used along the generation process for the embedded FPU                                                                 |

| 3.6  | Coverage evolution along the development flow for the embedded FPU116                                                                  |

| 3.7  | Number of test programs, duration, and code size for the embedded                                                                      |

|      | FPU                                                                                                                                    |

| 3.8  | Cumulative experimental results on industrial processors                                                                               |

| 3.9  | Cumulative experimental results on academic processors                                                                                 |

| 5.1  | List of possible configurations for the network in Fig. 5.6 130                                                                        |

| 6.1  | Effect of the functional fault on the ScanMux of Fig. 5.6, which always selects the input 1, when selecting different active paths 139 |

| 6.2  | Adjacency matrix of the configuration graph built on network in Fig. 5.6                                                               |

| 6.3  | Characteristics of the ITC'16 benchmark networks                                                                                       |

| 6.4  | Experimental results on the ITC'16 benchmark networks 161                                                                              |

| 6.5  | Characteristics of the selected networks                                                                                               |

| xvi | List of Tables |

|-----|----------------|

|     |                |

| 6.6 | Experimental results on the selected networks   | 165 |

|-----|-------------------------------------------------|-----|

| 7.1 | Characteristics of the new synthesized networks | 177 |

| 7.2 | Test and diagnostic sequences characteristics   | 178 |

### Introduction

A general definition of functional testing of microprocessor based systems is hard to give. I will try to explain the concepts separately and then put everything together. The key concept is testing, which in this thesis is the activity that checks whether a given entity works as expected, according to an ideal model [1]. When referring to a manufactured electronic product, several terms are commonly used, such as device under test (DUT) or unit under test (UUT) [2]. DUTs in this thesis are systems that include microprocessor cores and the focus of testing is given to physical defects possibly affecting such systems. Testing flows that are currently applied to electronic devices are based on the application of suitable stimuli to some specific test points of the DUT, while other test points are used to perform measurements of the DUT responses to the applied stimuli [3]. Different definitions of the term functional testing have been given, for example that it corresponds to checking whether the device is able to perform the function which has been designed for. Another definition is that, during functional test, only functional input signals of a circuit are stimulated (we will see that special logic is commonly included in the electronic device, e.g., for testing purposes) and only functional output signals are observed [4]. A common definition borrowed from software testing is that functional testing is one type of black box testing, in which functions are tested by feeding them input and examining the output, while internal structure is rarely considered [5]; in this context, only functional models are provided and the evaluation of functional tests requires the definition of new metrics [6, 7]. Finally, functional testing is often referred to as the test applied to the DUT while this is embedded in the overall system [3].

In the field of functional testing of microprocessor based systems, several research aspects are still open, such as concerning the generation of high-quality tests. The quality of a test is defined by well specified metrics and identifies the effectivess of the test in detecting defects. Hence, the more defects a test is able to detect the

higher the test quality. In this thesis, several systematic techniques will be introduced in the first part that are able to produce high-quality functional tests for common microprocessor based systems, while the second part will concentrate on special logic embedded in modern (and next-generation) designs. This logic is purposely inserted in a system to access to on-board instruments, such as sensors, debug-related features, special hardware used for testing, and so on. Other the testing the on-board instruments, the problem of testing the accessing logic itself is still open and is one the major achievements of this thesis.

The first part includes Chapters 1 to 4 and is about a well-known functional testing technique for microprocessor based systems, named software-based self-test (SBST). SBST is a self-test methodology performed by a processor available in the system, which executes a test program stored in an accessible memory. We will see in Chapter 1 the basic concepts and the state-of-the art of SBST. This subject is not new in literature, as many publications can be found proposing heterogeneous generation techniques and targeting aspects such as quality of the test, on-line execution of SBST during the normal system operations, or diagnostic capability of SBST.

SBST presents several advantages when compared to hardware approaches. Being a software-based technique, its development can be done in parallel with the manufacturing process of the hardware and eventual modification to test programs does not affect the hardware, while a modification to the overall system where the DUT is inserted in may affect the development of SBST. To understand the scenario, let us consider the test of a microprocessor. The manufacturing of the microprocessor passes through several phases, starting from the design of a microprocessor model up to the physical manufacturing. SBST is developed based on a model (at a given level of granularity), hence when the needed model has been consolidated, test programs can be generated. However, the test engineer (or the tool) implementing SBST requires the knowledge of the system in which the microprocessor is inserted in, such as the memory map and the attached peripheral cores. Since software operations may interact with such peripherals (or may produce different behaviors by changing the memory map), any modification to such an environment may require changing SBST programs, even by leaving the microprocessor untouched. We will see in Chapter 3 some of these problems, that are even more emphasized for on-line testing, where additional constraints exist due to the coexistence of SBST and operating systems.

Clearly, there are drawbacks that are limiting the adoption of SBST as the standard test solution for end-of-manufacturing, when compared with hardware approaches that are fully supported by commercial EDA tools. The current average capability of detecting defects by SBST is considerably lower and not acceptable to guarantee the expected level of test quality. Despite this, there are specific applications in which this coverage level is acceptable, such as for safety-critical domain, where standard regulations demand for constant monitoring of the system status, intended as faulty or not. These periodic tests should address the most relevant parts on the processor core, allowing in some cases low coverage levels in marginal processor parts. The industrial interest to SBST as a periodical self-test methodology for safety critical applications has moved the scope from the mere academic experience to reality. Although some of the techniques proposed in the literature in the last decades, which were trying to leverage the manual effort required to the test engineer, are valid and demonstrate that the automatic generation of SBST is possible, such techniques are still not applied in industry, where the work of test engineers is based on the personal experience and standardized commercial tools are demanded for quality aspects.

Even though part of my research work has been focused on automatizing the SBST generation, this part of the thesis is more oriented to the work of industrial test engineers, rather than to EDA tool vendors. An effective development flow based on manual processes will be described in detail in Chapter 3, which mainly targets in-field testing and on-line application of SBST. This process is preceded by a set of systematic algorithms presented in Chapter 2, which have been intended to cover special sub-modules existing in modern microprocessor based systems and have outperformed the state-of-the-art methodologies. Finally, some conclusive discussions on the topic will be given in Chapter 4.

The second part of this thesis consists of Chapters 5 to 8 and is focused on test and diagnosis of reconfigurable scan networks (RSNs). A RSN is a kind of infrastructure for interconnecting the numerous instruments that are available in the modern microprocessor based system. Such an infrastructure has the ability of being reconfigured to interact with different sets of instruments, dynamically. More details about RSNs will be presented in Chapter 5, which describes the basic concepts concerning instruments and reconfigurable modules, the main functional operations of RSNs, and the related work on this topic.

Given the recent approval of standards describing the specifications for RSNs, their adoption in electronic designs is growing fast and tools are being developed targeting several aspects related to their design, integration, and usage. Being the topic relatively new, few works can be found in the literature about the test of RSNs. A new functional testing approach will be presented in Chapter 6, based on performing functional operations on the network to excite possible defects, which affect the ability of the network of being dynamically reconfigured. One of the main goals of the presented methodology is to minimize the test time and different approaches will be presented, which are able to find both optimal solutions, highly demanding for CPU time and memory occupation, and sub-optimal, this time using very few resources. Diagnosis of RSNs will be discussed in Chapter 7. The proposed diagnostic algorithm is able to apply functional operations to identify the faulty element of the network. To the best of my knowledge, the presented work is the first one targeting diagnosis of RSNs. Finally, Chapter 8 will give some conclusions on this topic. Contrarily to the first part, the algorithms presented for RSNs are mainly oriented to EDA tool vendors.

### **Problem Formulation**

This thesis deals with the enhancement of state-of-the art SBST techniques and with the test and diagnosis of RSNs.

Concerning SBST, the research question this thesis is trying to answer is whether SBST can be successfully adopted for the test of real-world processor based systems. This means providing algorithms and techniques that a test engineer can systematic implement for the specific DUT with reasonable effort. Moreover, when dealing with real-world processors, the problem of integrating SBST in the on-board operating system represents a further challenge.

Concerning RSNs, at time of writing there are very few works existing in literature about testing, while contributions about diagnosis are missing. The research question tackled by this thesis is whether RSNs can be systematically tested, once the functional description is known and, in this case, in the minimum amount of time. Moreover, whether it is possible to diagnose which is the faulty part of a specific RSN, systematically and in a reasonable time.

# Part I Software-Based Self-Test Enhancements

## **Chapter 1**

## **Background**

The use of microprocessor based systems in safety- and mission-critical applications, calls for total system dependability. This requirement translates in a series of system audit processes to be applied throughout the product lifecycle. Nowadays, some of these processes are common in industrial design and manufacturing flows. These include risk analysis, design verification and validation, performed since the early phases of product development, as well as various test operations both during and at the end of manufacturing or assembly steps. Increasingly often, test operations need to be applied during the product's mission life, such as periodic on-line testing and concurrent error detection. The reliability requirements are met by trading off test quality with admissible implementation costs of the selected solutions.

This chapter briefly introduces the topic of Software-Based Selft-Test, which is a consolidated technique for the functional test of microprocessor based systems, together with basic concepts needed for the understanding of this thesis.

The rest of this chapter is structured as follows. Section 1.1 presents the basic terms and concepts. Section 1.2 gives a definition of SBST and discusses the related work. The methodology used to evaluate of the SBST fault coverage is briefly described in Section 1.3. Section 1.4 discusses about possible observability solutions used to evaluate SBST. The chapter is concluded in Section 1.5 by a discussion of the most used SBST generation techniques.

Parts of this chapter have been published in [17], concerning observability solutions for SBST.

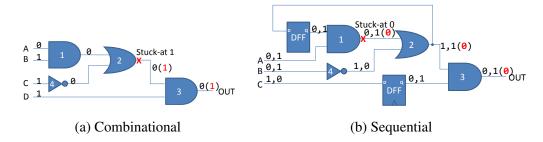

Fig. 1.1 Stuck-at fault and possible test pattern for a sample combinational circuit (a) and sequential circuit (b)

### 1.1 Basic Concepts

The purpose of *Testing* is to identify defective products. When electronic circuits are considered, it consists in the application of suitable patterns to certain test points of the actual circuit, such as the input ports, while other points, such as the output ports, are sampled and compared to expected values, that are computed on an ideal device. If there is a mismatch between measured and expected values, a certain defect affecting the device has been identified [3].

Generating test patterns for assessing the correctness of the structure of a circuit is a critical task. In order to make it feasible and to quantify the efficacy of a test, the possible circuital defects are mathematically modeled as *Faults* [1]. Testing usually refers to faults instead of defects, since the first can be enumerated. Fault coverage is defined as the fraction of faults detected (or covered) by a set of test patterns over all possible faults according to a fault model.

Test pattern generation for combinational circuits is quite straightforward. The pattern has to activate (or excite) the fault at its location, which means to introduce a logical difference between the fault-free machine and the one affected by that fault. Then, it has to propagate the fault effect to an observable point. An example of test pattern for a stuck-at-1 fault affecting a combinational circuit is shown in Fig. 1.1a. In the example, the test pattern excites the stuck-at-1 fault by forcing the value of the faulty location to be 0 and propagates the fault effect up to the OUT signal. The problem of test pattern generation for sequential circuits is more complex, due to the presence of memory elements (e.g., flip-flops). In this scenario, additional effort is needed to move the fault effect towards an observable point. In the example shown in Fig. 1.1b, the first pattern applied to the primary inputs of the sequential circuit loads

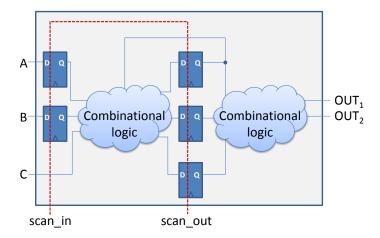

Fig. 1.2 Conceptual representation of a sequential circuit including a scan chain

the flip-flops with suitable values; then, in the next clock cycle, the fault excitation and propagation are performed by both the second pattern and the values previously stored in flip-flops.

Automated algorithms for test pattern generation are widely known and employed in industry. This technique is defined as Automatic Test Pattern Generation (ATPG). The complexity of the ATPG grows exponentially with the sequential depth of the circuit.

To circumvent the complexity of sequential test pattern generation, which is the case of microprocessor based systems, hardware solutions are applied to the original design, specifically devised for testing purposes. Such solutions are traditionally known as Design-for-Testability or DfT. A de-facto standard DfT solution implemented in all currently available industrial microprocessors is the inclusion of one or more scan chains. A scan chain is a serial connection of the available flip-flops in a circuit and is accessible by additional dedicated pins (see Fig. 1.2). By serially shifting test patterns through the scan chains, the testing problem is restricted to the complexity of the combinational logic, thus the efficiency of the ATPG is dramatically increased. Other DfT solutions are based on Logic Built-In Self-Test or Logic BIST, which are able to apply stimuli to the primary inputs of the device under test and to compact the primary output values into a so-called *test signature* [3].

Testing solutions exploiting the available DfT such as scan-chains may present some problems: firstly, they are poor in detecting certain faults (e.g., dynamic faults related to timing issues) since DfT tests are performed at low frequencies;

additionally, they manipulate the internal state of the system, differently to the normal functional mode, passing through unreachable configurations. When the testing is performed at the nominal frequency of the circuit, without using special hardware not guaranteeing its functional mode of operation, then it is said to be *functional*. This means, for example, that a functional test does not make use of scan-chains and is typically used for in-field testing, when an excessive stress due to unreachable configurations is neglected or scan chains are not accessible anymore.

### **1.2** Software-Based Self-Test (SBST)

The term Software-Based Self-Test (SBST) was first proposed by Chen and Dey in [18], but the approach itself has been proposed few years before under the name *Native Mode Functional Test* in [19, 20]. SBST broadly identifies all test methodologies based on forcing a microprocessor/microcontroller to execute a program and checking the results to detect the presence of possible defects affecting the hardware. Indeed, the pioneering idea of testing a microprocessor with a program dates back to 1980. In [21], Thatte and Abraham devised fault models and procedures for building test programs able to detect permanent defects in different functional units of a simple processor. A wide adoption of their methodology was hindered by the difficulties in automating the generation of such test programs, especially when targeting complex processors.

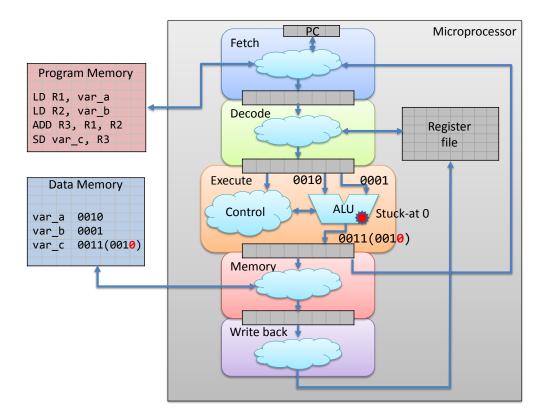

The basic concept of SBST is graphically depicted in Fig. 1.3. In the figure, a stuck-at-0 fault affecting the ALU is excited by a specifically crafted sequence of instructions and by suitable data. When the sequence of instructions is executed, the result of the arithmetic computation is stored in the data memory. The contents of the memory are then compared with the expected values, hereinafter referred to as *golden* references. Alternative ways to observe the fault effect are discussed in Section 1.4.

In general, the usage of SBST requires:

1. Generating a suitable test program. This is typically a hard job, which is still mainly performed by hand. Moreover, the complexity and effectiveness of this task depends on the adopted metric, which in turns depends on the available information: in some cases, both RTL and gate-level models of the

Fig. 1.3 Conceptual representation of a pipelined microprocessor architecture and example of SBST for a stuck-at 0 fault in the Arithmetic Logic Unit (ALU)

target system are available, while in others functional information is available, only. When the gate-level netlist is available, then it is possible to compute the fault coverage achieved by the generated test program with respect to the most common structural fault models (e.g., stuck-at). Details about the most common generation techniques are given in Section 1.5.

2. Creating an environment to support its execution. Once the test program is available, it must be stored in some memory accessible by the processor. The processor must be triggered to execute the test program at the due time. Finally, the results produced by the processor during its execution must be observed. More details are given in Section 1.3.

Nowadays, the complexity of processors has significantly increased; the microarchitectural details play a fundamental role, and devices cannot be accurately modeled using information about the Instruction Set Architecture (ISA) alone. However, SBST is getting more and more important: it commonly supplements other kinds of tests, as functional programs may detect unmodeled defects that escape

traditional structural tests (the so-called "collateral coverage" [22]). By definition, the functional approach tests the system in its operational mode, without activating a test mode and without reconfiguring the system; hence, it is guaranteed not to cause overtesting (or overkilling). Moreover, several producers exploit functional stimuli to validate their design or to run post- silicon verification.

In some cases, test programs are generated pseudo-randomly [23], possibly using simulation feedback, and may even use some hardware support to make the test phase more efficient [24].

Among the several recent works focusing on SBST, some aim at developing algorithms to generate effective test programs for common modules starting from the knowledge of its ISA alone (e.g., for an OpenSPARC T1 processor [25] or a MIPS-like ISA [26]), eventually combined with RTL description (e.g., [27] for two different implementations of the MIPS ISA).

Several works focus on the possible automation of the test program generation procedure. Details on some of the most used generation techniques are given in Section 1.5. The work in [28] proposes a genetic-algorithm-based evolution framework that enables small test programs to evolve using a LEON2 processor. High-level decision diagrams (HLDDs) are used by the authors of [29]. The work in [30] applies bounded model checking tools on a global extended finite state machine (EFSM) model of the processor under test. SAT-based test program generation is also proposed by several other works [31, 32], including a personal collaborative work [33], which is able to derive test programs from the gate-level microprocessor description. The SAT-based framework of such work is described in details in [34] and not included in this thesis. Other works reuses existing procedures to automatically generate effective test programs. For example, [35] remaps generic test program on a target processor, as experimented in a VLIW processor, while [36] uses the execution trace collected during executing training programs on the processor under test to create constraints for the test program generation.

The possible usage of SBST for diagnostic purposes has also been explored, e.g., in [37] using an 8-bit accumulator-based microprocessor, and [38] for transition-delay faults in an i8051-compatible microcontroller. The work in [39] is able to produce diagnostic test programs, which specifically target for faults that can be handled with an available self-repair method. The same authors described how to integrate such programs into a superscalar processor [40]. A personal collaborative work [41]

tackled the automatic generation of test programs with diagnostic capabilities and provides results gathered on a MIPS-like processor. Also in this case, the work is not further discussed in this thesis and details can be found in [41].

Finally, a number of works study how to apply SBST for in-field test (e.g., [42] for a MIPS architecture processor).

In this last domain, regulations and standards mandate the adoption of effective solutions to early detect permanent faults, and SBST has the big advantage that it does not require access to any systematic DfT solution, whose usage details are often considered as proprietary by the manufacturer. SBST can be used not only to test the CPU, but also the other components in a microcontroller or SoC: for example, several works addressed its adoption for the test of peripherals [43], memories [44] (possibly implementing transparent test [45]), and cache memories [46, 47]. SBST usage can also be extended to the test of multi-core systems [48]. In some cases, the usage of existing hardware resources introduced for non-test-related purposes (e.g., for debug, design validation, performance assessment) allows significantly reducing the size and duration of SBST test programs [49].

Moreover, SBST can more easily match the constraints of the environment where the processor is employed. When adopted for in-field test, SBST typically means activating a test program either at the system power-on, or during the application idle times. In the latter case, additional constraints about the duration of the test exist, due to the limited duration of the available time slots. Unfortunately, the constraints posed by the application environment may severely impair the effectiveness of the method when applied to test a processor. When functional test is used for endof-manufacturing test, processor inputs and outputs can often be fully controlled and observed by an automatic test equipment (ATE). Nevertheless, during in-field test some parts of the processor (e.g., the test and debug structures) might not be accessible by the test procedure, thus resulting in untestable faults [50], i.e., faults for which no input stimuli exists, able to detect them. In other words, some parts of a processor which are not used anymore during the operational phase may contain faults, which cannot be tested in this phase, but are also guaranteed not to affect the system behavior. Besides, not all the processor inputs may be freely controllable in the in-field scenario: for example, activating the reset signal is hardly possible, thus preventing the test of the reset logic. More in general, possible Control/Status input signals coming from other devices may be hard to control [20]. Finally, observability

Fig. 1.4 Fault grading process for SBST

during SBST in-field test could be limited, since only the produced results (e.g., in memory) can be observed. The set of faults which cannot be tested in the in-field environment due to these additional constraints are known as *functionally untestable faults* [50]. As previously mentioned, it is important to be able to identify untestable faults, since they limit the achievable fault coverage.

### 1.3 Fault Grading Process for SBST

Fault grading corresponds to the task of measuring fault coverage of a certain SBST procedure. This process, that evaluate the effectiveness of SBST programs, passes through two main steps: the golden simulation and the fault simulation (see Fig. 1.4).

In microprocessor based systems, all the environment concurs to the test program execution. The environment includes the microprocessor itself, together with accessible peripheral cores and memory modules. A proper testbench has to be able to control such a system, load a compiled program in th available memory, and finally forces the microprocessor to executes the program.

A logic (golden) simulation of the testbench uses the SBST program to collect the golden run responses, e.g., the values of the microprocessor primary output ports, or the memory content at the end of the test program. The fault simulation uses the golden run responses and compare them with the faulty circuit responses, according to a given observability solution (refer to Section 1.4). The fault list used in fault simulation contains all faulty locations to be checked in the gate-level netlist of the system.

At the end of the grading process a fault coverage report is produced. Further analysis on the circuit can be performed to show effective test coverage not taking into account functionally untestable faults. As an example, some scan signals may become faulty but never affect the in-field SoC behavior, or modules used to perform software and silicon debug will be no more used during the mission, thus may be skipped during the grading process. Details about how to identify part of these faults are given in [50]. In generation approaches based on formal methods, it is possible to prove that a given fault is functionally untestable during test generation, as shown in a collaborative work based on SAT solvers [34].

More details on a fault grading process for dependable automotive applications are presented in [51].

### 1.4 Observability Solutions

In the following, the main solutions that can be adopted to observe the effects of possible faults during the SBST testing of a processor-based system are described, namely: module-level, processor-level, system bus, memory content, and performance counters. The above solutions are referred to bare metal systems, i.e., solutions that would require the presence of an Operating System (e.g., based on monitoring its performance, or analyzing the event logs) are not included.

The assumption is that the targeted faults are those inside a given module within the processor. For every solution, the adopted mechanism as well as the main advantages and disadvantages are detailed, and a preliminary analysis about the forecasted coverage is reported. Fig. 1.5 graphically summarizes the considered solutions.

Fig. 1.5 Generic system under test: the observation points adopted by the techniques described in the text are highlighted

### 1.4.1 Module-Level

When a generic module inside the processor is considered for the test, the *ideal* level of observability is the boundary of such a module, i.e., it is assumed that all the output ports are available for observation.

The test program is supposed to be able to properly stimulate the input ports of the considered module, to excite the faults and to propagate them towards the module output ports, which are test observation points.

This observability approach can be adopted during simulation and fault simulation processes. However, when working on real chips, for a number of reasons it is hardly feasible neither in-field nor, in most cases, at end-of-manufacturing. These reasons are, firstly, that the module output ports usually do not coincide with the circuit pinout, and even if they do, it is normally not affordable to continuously observe the circuit behavior without resorting to additional hardware; secondly, when an instrument is attached to the observation points, the observed signals can only be read in test mode through a dedicated tester.

Therefore, this observability solution is introduced here only as a reference, because it establishes an upper bound to the fault coverage results obtainable in simulation through SBST test approaches.

### 1.4.2 Processor-Level

This solution assumes that fault effects can be observed at the processor level, i.e., that all the processor outputs can be continuously monitored. While module-level observability is very specific and may be not feasible in practice, observability at processor-level represents one of the scenarios that are sometimes adopted for end-of-manufacturing test. Considering an internal module which has to be tested, the test program must not only propagate the fault effects up to the module output ports, but must be able to propagate them also to the processor output ports.

According to these considerations, the observability we can get with this solution is generally lower than the one obtained at module-level. In most of the cases, propagating the faulty behavior requires an additional effort in order to reach the processor outputs. In the case of a functional testing approach based on test programs, this additional effort may imply the addition in the code of specific instructions able to propagate the fault effects to the processor outputs. As an example, faults within an arithmetic unit can be easily activated by executing suitable arithmetic instructions (thus propagating their effects on the module outputs), and can then be made observable on the processor outputs via Store instructions that propagate the result of the arithmetic operation up to the processor output ports.

Faults may also exist that, even with the addition of instructions, cannot be observed on the processor outputs. This situation may happen when the processor design includes some redundant circuitry, for example left from previous releases or included for future extensions of the design. Clearly, the related faults can be classified as untestable. However, the identification of untestable faults may often represent a relevant problem.

Due to the need of constant monitoring of all the processor outputs, this observability solution requires the use of an ATE and thus, cannot be adopted by in-field SBST.

### 1.4.3 System Bus

This solution mandates that the control, data and address signals of the system bus are continuously monitored. When comparing this solution with the previous, all the processor outputs not related with the system bus are excluded from observation.

End-of-manufacturing scenarios may offer a high-level of observability, when the constant monitoring of the output ports of the processor is possible. Such a powerful scenario is not representative of an observation mechanism for in-field testing. However, more and more processors (especially for embedded systems) are equipped with specific components in charge of monitoring the interconnections between the processor and the memory subsystem, in some cases including external caches. Examples of such modules are MISRs attached to the bus, that update a signature every time new data are going to be written to the memory. This solution has been adopted by commercial microcontrollers, e.g., from Freescale [52]. In other cases, dedicated programmable embedded cores are in charge of tracing specific bus transactions (e.g., ARM HTM [53]) and of storing a history of processor execution in a local memory, which is accessible through a dedicated port (e.g., for debug purposes). An example of IP core specially devised for SoC testing is described and demonstrated for a processor compliant with the SPARC v8 architecture in [54]. The presence of caches significantly limits the amount of data flowing through the bus, and hence the number of faults whose effects can be observed by observing it.

SBST programs using this observability solution should include specific sequences of instructions that permit the propagation of the fault effects up to the system bus.

As an example, the faults affecting the circuitry for supporting an external coprocessor are considered. If the external coprocessor is connected to the processor with dedicated ports, the effects of such faults –propagated up to this interface in the original program– need to be read back from the coprocessor and stored to the system memory in order to become observable in the system bus. This solution adds complexity to the test program and is not always feasible. In case of faults whose effects can only be observed on non-functional output signals and never read back, the fault coverage reduction cannot be recovered, thus resulting in a potentially less-effective observation mechanism in general.

Also, if an SBST program developed for processor-level observability is evaluated with this observability solution, a significant fault coverage reduction could be observed. This fault coverage loss is motivated by the reduction of the observed signals, as they are a subset of the output signals of the processor.

### 1.4.4 Memory Content

According to this solution, a fault is marked as detected if the content of the system memory is different than the expected one at the end of the execution of the SBST program.

All the previously presented observation mechanisms rely on the fact that some output ports of the circuit can be constantly monitored, e.g., by a dedicated tester which is physically connected to test points or to the interface with on-board instruments. This is not the usual case of SBST in general. In a manufacturing at-speed SBST scenario, the functional program is often uploaded in the system memory (e.g., a cache, or a dedicated flash) and run at-speed, storing its responses in some available memory elements, such as internal registers, caches, or main memory, and hence permitting a low-cost tester to access them at the end of the execution. Similarly, during in-field SBST, at the end of the test program run the processor itself or another module (e.g., another processor) may perform an access to the specific memory cells in order to compare their values with the expected ones.

According to the presented scenario, this observation mechanism assumes that the test program collects in some way the information about test results and saves this information in the system memory. The information collected by the test program may be compacted by the test program itself and then (at the end of the test process) saved in few selected memory cells. Alternatively, the information saved by the program may be written to a set of memory cells, according to the targeted module characteristics as described in [55] for a MIPS-like processor and an industrial System-on-Chip.

Since the test results correspond to the values generated by the test program, which are checked only at the end of the test program execution without taking into account when these results are produced, some performance faults may escape when using this observability mechanism. For example, in the case of Branch Prediction Units, some performance faults may not modify the final test program results, but only delay the actual execution time [56], e.g., by turning a correctly predicted branch into a mispredicted one.

### 1.4.5 Performance Counters

Performance Counters (PeCs) measure the number of occurrences of different internal events, making their observation easier from the outside. They exist in many processors, mainly for design validation, performance evaluation and to support silicon debug. Their values can normally be accessed via software. Hence, a test program may read the value of a given PeC, execute a sequence of instructions exercising a given module, and then read again the value of the PeC comparing it to the expected one. Possible differences may allow the detection of faults inside the module.

The most common types of PeCs include those that count internal events related to:

- caches, counting the number of miss and hit events;

- Branch Prediction Units (BPUs), counting the number of correctly or incorrectly predicted branches;

- pipeline stages, counting the different types of stalls;

- Memory Management Units (MMUs), counting the number of hit/miss accesses to the Translation Lookaside Buffer (TLB);

- exception units, counting the number of triggered exceptions, often divided by type.

- bus interfaces, counting the number of performed bus transfers, also often divided by type.

These counters are already quite common in general-purpose high performance processors, and their adoption is growing in microcontrollers for embedded applications.

The usage of these counters as part of the observability mechanism adopted by a testing procedure was proposed in several works, such as [56, 26] that use variants of the MIPS architecture, or [57, 58] working with the OpenSPARC T1 processor. The PeCs have also been proposed as feedback in automatic test programs generation [59] and in [47]to simplify the test programs aimed at detecting faults in caches. They are crucial for the detection of some specific types of faults, such as performance faults. Moreover, they can facilitate the test of faults belonging to some modules, such as Branch Prediction Units, Cache Controllers, TLBs. They may also be used

Fig. 1.6 Taxonomy of routine development styles for SBST, taken from [60]

to support the test of specific modules within the pipeline, such as those controlling the activation of stalls.

Regarding observability issues, the PeCs may provide deeper details on internal events affecting the module that may not reach the output ports, and allow the detection of several performance faults. Thus, exploitation of PeCs and propagation of performance values to system memory increases observability and may represent a valuable solution during in-field SBST.

## 1.5 Generation Flows

This section presents some of the most common methodologies for the development of SBST programs. As a reference, the nomenclature presented in [60] is used. The main taxonomy of different development styles is also shown in Fig. 1.6. The authors includes all possible generation techniques into two main categories:

**Functional methods** that exploit only functional information, such as the microprocessor ISA. They include both methods that rely on *code randomizers*, sometimes guided with suitable constraints, and methods that adopt a *feedback-based* strategy, meaning they evaluate generated test programs according to suitable metrics (often computed through simulation) and try to progressively improve them.

22 Background

**Structural methods** that uses also structural information, such as gate-level are RTL descriptions. These methods are further divided into two categories: *hierarchical* approaches, that focus on a processor's module one at a time, generating stimuli for each module and then extending those stimuli to the processor level; and *RTL* approaches, that exploits structural RTL information along with the ISA information to generate instruction sequence templates for justifying and propagating faults of the module under test.

Above all the methodologies listed in Fig. 1.6, in the following three representative techniques are discussed in details.

#### 1.5.1 ATPG-based

This methodology guarantees the highest possible coverage, given the fact that test patterns for a specific module are automatically generated by means of an ATPG engine. Especially for combinational blocks, ATPG is able to reach 100% test coverage, while it may be harder (in terms of computational effort) for complex sequential circuits.

These patterns are intended to be applied to the primary input signals of the block under test and are usually provided in text format (e.g., STIL). Further work is needed to parse the text file and transform the signal values to a sequence of assembly instructions. Such step is trivial for simple blocks, but can be more challenging in other cases, where selection signals have to be properly interpreted. This requires the knowledge of the processor's microarchitecture.

A few coverage loss is typically observed when transforming ATPG patterns to SBST, due to masking effects and aliasing during the signature computation.

*Effort*: medium-low (minutes to hours), depending the functional block complexity. In the best case, it requires a single fault simulation.

## 1.5.2 Deterministic

It consists in the implementation of a documented algorithm or methodology. This is a functional methodology, which does not highly depend on the internal structure of the module under test. Some new deterministic algorithm targeting specific modules of modern microprocessors are presented in Chapter 2.

The expected fault coverage level is medium to high. However, the resulting program can be highly redundant in terms of test patterns applied to the module under test. This redundancy is mainly present to effectively adapt the program to the whichever implementation of the module.

These kind of techniques are really useful when the netlist is missing or not hierarchical (e.g., flattened, obfuscated). Moreover, they are suitable for such modules that are too complex for ATPG-based methods.

*Effort*: low (minutes to hours). In some cases, it requires several adjustments and fault simulations, until an appropriate level of fault coverage is reached.

### 1.5.3 Feedback-based

This methodology is based on an iterative generation, in which the fault-coverage of the current test program is used as a feedback for the next program generation.

A sample scheme resorting on random code generator is graphically depicted in Fig. 1.7. According to this scheme, a test program is incrementally generated, by adding new instructions at each iteration. Every time new instructions are added to the test program, a fault simulation is performed. If new faults are not detected by the test program, then the added instruction are removed by the test program and new ones are generated in the following loop.

An alternative scheme is based on an evolutionary engine to continuously generate test programs, as shown in Fig. 1.8. The effectiveness of this technique depends both on the number of test programs generated and the skills of the test engineer, which has to guide the evolutionary engine. Briefly, the test engineer has to build the basic blocks of the test programs, where some parameters such as register contents are unknown. The evolutionary engine starts by assigning random values to such parameters. Later on, after the fault coverage level of the generated programs is evaluated, the engine is able to combine previously generated programs and to generate new ones [61].

The fault coverage can be very high, but it requires that many programs are generated. This technique is highly useful for distributed parts of the processor, for

24 Background

Fig. 1.7 Feedback-based approach based on random code generator

Fig. 1.8 Feedback-based approach based on evolutionary engine

which is quite difficult to group the logic into a well-defined module. In this case, the fault list is enough to guide the evolution. Even for flattened or obfuscated circuits, it can be used to cover the corner cases as the last generation process (i.e., after deterministic approaches).

*Effort*: medium-high (hours to days). Since each program is fault simulated, the time required for a single fault simulation is a key parameter for the effectiveness of this method. The preliminary steps of preparing the program skeletons require additional effort, but typically this is not very high.

25

Table 1.1 SBST generation techniques comparison

| Technique      | #lines  | #clock cycles | SA FC% |

|----------------|---------|---------------|--------|

| ATPG-based     | 110/708 | 3,549         | 98.0   |

| Deterministic  | 42/533  | 41,326        | 90.1   |

| Feedback-based | 164/188 | 1,651         | 91.9   |

Table 1.1 provides the results in terms of number of code lines, clock cycles required to execute the programs, and stuck-at (SA) fault coverage while using the described techniques, targeting the shifter module included in the ALU of an industrial processor core. The shifter counts with 4,196 gates. The column labeled as #lines provides two values (A/B) showing the number of lines of the obtained test program. The A and B values count the number of lines of a loop-based version of the final program and its unrolled version, respectively.

# **Chapter 2**

# **SBST Algorithms**

Test programs included in a SBST test suite for microprocessors are typically developed following heterogeneous approaches. Although an automatic way to generate them would be the dream of every test engineer, similarly to the ATPG for test patterns, at the moment most of the work is done by manually implement systematic test algorithm on the target processor, especially in industry. This is mainly due to the lack of automatic SBST support by commercial EDA tools.

A negative aspect of these approaches is that the effectiveness of manually developed test programs is highly influenced by the skills of the test engineers and the availability of test algorithms for different parts of the processor. The more the processors become complex, the harder it is to reach high fault-coverage levels especially on those modules that are not directly controllable by single assembly instructions.

This chapter purposely tackles the testing of particular sub-modules of modern processors that are deeply embedded in the pipeline and whose faults are historically considered hard to test.

In Section 2.1 the focus is given to the Decode Unit, which in RISC processors is responsible for decoding each instruction fetched from the program memory and generating the control signals needed by the other units.

Section 2.2 covers faults on hardware modules responsible for resolving data hazards. A data hazard is the situation in which the result of a previous instruction is needed in the pipeline before it is available. Hardware modules devoted to

2.1 Decode Unit

resolve such a situation implement the Register Forwarding and Pipeline Interlock mechanisms.

Section 2.3 deals with superscalar processors that are able to issue multiple instructions at a time. A set of rules and strategies are given for the re-design of traditional SBST techniques to cope with multi-issue aspects. Although the presented algorithms specifically target dual-issue processors, a test engineer can easily adapt them to complex in-order multi-issue processors.

Finally, a classical computational module such as the Floating-Point Unit (FPU) is analyzed in Section 2.4. Although the FPU differ from the previous modules in terms of controllability by means of specific assembly instructions, its test is not a trivial task. Specific strategies are shown that are able to cover possible test escapes of state-of-the-art techniques.

Parts of this chapter have been also published in [9] (about Register Forwarding and Pipeline Interlocking), [8] (about Decode Unit), and [11] (about FPU).

The presented algorithms are examples of *free* test program generation, which does not take into account online testing contraints, such as test duration and memory occupation of the test suite. Details about those aspects are analyzed in Chapter 3.

Experimental results based on fault-simulation are given in each section for each of the presented algorithms. Results refer to both academic and industrial processors manufactured by STMicroelectronics.

## 2.1 Decode Unit

In this section, a functional methodology to test common decode units by means of SBST is presented. The method uses the instruction set architecture (ISA) of the target processor and its pipeline functional behavior as described in the user manual, only. The physical implementation of the processor is only used for evaluating the fault coverage of the proposed methodology on the actual processor netlist.

Details about the proposed methods are given in the following subsections. A brief architectural overview is given in Section 2.1.1. The overall approach starts analyzing the instruction set and dividing the list of assembly instructions into homogeneous groups, as presented in Section 2.1.2. Depending on the class of

instructions, Section 2.1.3 shows different implementations of *signature* mechanisms, i.e., the way to observe the effect of faults affecting the decode unit after the target instruction has been decoded. Such signature mechanisms have to be included in the synthesized SBST procedures, which are specific of each group of instructions, as detailed in Section 2.1.4. Finally, experimental results are presented in Section 2.1.5.

#### 2.1.1 Architectural Overview