# Politecnico di Torino

Doctoral dissertation

Doctoral Program in Electrical, Electronics and Communications Engineering (cycle XXXIII)

Curriculum in "Electronic Devices" in convention with the National Institute for Nuclear Physics (INFN)

## CMOS distributed signal processing systems for radiation sensors

#### Andrea Di Salvo

Supervisors: Prof. Angelo Rivetti, Supervisor (INFN) Prof. Goano Michele, Co-supervisor (Politecnico di Torino) Dr. Manuel Dionisio Da Rocha Rolo, Co-supervisor (INFN)

#### **Doctoral Examination Committee:**

Laura Gonella, Referee (University of Birmingham, UK) Valerio Re, Referee (University of Bergamo, Italy)

## Abstract

The purpose of this thesis is to address aspects of digital signal processing for multi-channel ASICs employed to read out radiation sensors. These detectors are characterized by a high degree of segmentation and they are coupled to integrated front-end electronics embedding many channels operating in parallel. The number of channels found on a typical front-end ASICs ranges from 16 to 128, but some applications require up to thousands of processing block integrated on the same die. In these systems, low power consumption is often at a premium. In tracking detectors used in particle physics, for instance, the mechanical infrastructure needed to cool down the system adds a significant material on the particle path that can blurry the reconstructed tracks. In satellite-based applications, power consumption is always a primary concern for obvious reasons.

Modern deep-submicron CMOS technologies allow to achieve densely packed systems, but the non-recurring engineering costs can be problematic. It is therefore preferable to develop flexible circuits that can be re-used for different sensors, thus serving multiple experimental setups. Consequently, multi-channel mixed-signal ASICs where fast ADCs are mated to digital processors become increasingly interesting in the radiation instrumentation community. In the following, this architecture will be referred to as a *full sampling system* to distinguish it from other more specialized topologies. Although very common in mainstream electronics, the full sampling approach has not been widely used so far in radiation instrumentation because the power consumption of fast ADCs prevented their use in most multi-channel systems, where the power consumption has to be kept well below 10 mW/channel. The typical resolution required to these converters in the applications of interest in this thesis is between 8 and 12 bits, while the sampling frequencies ranges from 10 MS/s to more than 1 GS/s. A sampling frequency in the 10 - 100 MS/s range is however already adequate in many cases. The digital processor must be able to extract signal features such as the energy of the impinging particle and the time of occurrence of the event. Compared to commercial products, the design of these systems is challenging. For instance, on the analog side the distribution of a clean reference voltage for the ADCs is very critical, as many ADCs have to operate in parallel, thus heavily loading the reference voltage. On the digital side a very low-power consumption and fast processing must be simultaneously achieved. Additionally, radiation hardness to both total ionizing dose and single event effects are required to guarantee the circuit functionality. Hence, all these aspects have to be taken into account, requiring the development of custom solutions.

The aim of this work was to investigate digital signal processing solutions for low-power radiation detector systems. The work focused in particular on the application of ADC digital calibration algorithms optimized for the radiation detection environment and on the design of low power processors for feature extraction. A custom high-level simulation environment that allows to compare different options was also deployed.

The thesis is organized as follows. Chapter 1 introduces key concepts about radiation sensors which are relevant to discuss key issues addressed in the rest of the work. The most frequently used topologies in the implementation of multi-channel front-end ASICs for radiation detectors are briefly reviewed, with an emphasis on the state of the art of full sampling circuits.

Chapter 2 starts with the discussion of ideal analog-to-digital converter characteristics and the causes of the error conversion such as the quantization error, thermal noise, jitter and capacitance mismatch. The discussion focuses in particular on SAR ADCs, which are of particular interest for this work. A high-level code that allows to model the relevant ADC errors was developed on purpose to provide inputs to test different error correction strategies.

In Chapter 3 key techniques used in digital calibration of ADCs are reviewed. A section describes in detail the chosen digital algorithm, named Offset Double Conversion, selected to mitigate the non-linearities of a converter. A following section explains how the calibration processor was implemented, describing the finite state machine, all its functionalities and the developed solutions for an on-chip implementation.

Chapter 4 discusses the digital signal processor which in a full sampling system follows the ADC. A dedicated section considers the difference between the FIR and IIR filters implementation. An overview on the digital signal processor is presented with the description of the circuit at block level. All the features implemented in this unit are described, starting from the anti-glitch system based on self-adjustable thresholds. The bisection algorithm for the square root computation is discussed. This algorithm is used to prepare to the baseline restoration which benefits of the same dynamic thresholds. A pile-up unit to manage the rejection of events too close in time has also been developed. The mathematical description of a digital  $CR-RC^4$ pulse shaper is derived and its signal-to-noise ratio performance is discussed. The trapezoidal filter used belongs to the deconvolution filter class and it is referred to as mobile window deconvolution. Its explanation is reported as well as the circuit employed for the energy extraction of the signal. A snippet code is provided to show in more detail the strategy adopted in the calculation of this feature. The chapter ends with a descriptions of the digital filters implemented to calculate the time of occurrence of the event.

Chapter 5 is divided in two parts to separately show the physical implementation of the calibration block and the digital signal processor. For both circuits the post P&R simulation carried out in the typical corner are reported. The power analysis was only executed for the 65 nm CMOS technology, highlighting the contribution of each sub-block in the total power budget. For what concerns the calibration circuit, a prototype has been realized in 110 nm CMOS process. This chip includes a segmented SAR ADC with a nominal resolution of 12 bits, the correction block, two serializers and LVDS banks. A section reports the experimental results and discusses their analysis. Finally, a protection against single event upset and multiple bit upsets is presented.

Chapter 6 is reserved to data compression topics and three different techniques are discussed. These methods were used in a preliminary study about data compression for RD53A which is a pixel readout integrated circuit designed for the CMS experiment upgrade at CERN and fabricated on silicon. The last chapter summarizes the key outcome of the work, presenting conclusion and outlooks.

Ai miei genitori, senza i cui sforzi tutto questo non sarebbe stato possibile, non così almeno.

A tutta la mia famiglia.

# Acknowledgments

Writing a PhD thesis is a hard work which is essentially a patchwork of knowledge, tips and people.

Thus, I would like to thank the INFN staff of Torino that have helped me over these years. I express my first thank to Angelo Rivetti for this experience in a research context and also for scientific, technical and informal conversations, both in person and at a distance. I am deeply grateful to Floarea Dumitrache for the bonding of the prototype chip, Francesco Rotondo for the design of the test board and Richard Wheadon for his essential work with the DAQ system during the tests as well as our small talks. Without yours contributions, I would not have been able to collect the results reported in the current dissertation. I acknowledge the important support of Giulio Dellacasa for the power analysis of my digital processors.

I would also like to thank Manuel Da Rocha Rolo, Marco Mignone and Barbara Pini while I was joining the Arcadia project.

Special thanks go to Pisana Placidi and Giuseppe Baruffa for the discussions on data compression and the days I spent in Perugia.

Thanks also to my PhD colleagues and the Postdoctoral Researchers for their help. In addition, I really appreciated the nice time together because it is important as the technical support.

Lastly, I am grateful to my family, my friends and who shared this period with me. Many times even just yours listening and a couple of words have lightened my efforts. Thank you, with love.

Andrea

# Contents

| 1 | ASIC architectures for radiation sensor read-out |                                         |    |  |  |  |  |

|---|--------------------------------------------------|-----------------------------------------|----|--|--|--|--|

|   | 1.1                                              | Radiation sensors                       |    |  |  |  |  |

|   | 1.2                                              | Front-end architectures                 |    |  |  |  |  |

|   | 1.3                                              | Full sampling systems                   | 13 |  |  |  |  |

|   |                                                  | 1.3.1 ALTRO                             | 14 |  |  |  |  |

|   |                                                  | 1.3.2 Super ALTRO                       | 15 |  |  |  |  |

|   |                                                  | 1.3.3 SAMPA                             | 16 |  |  |  |  |

|   |                                                  | 1.3.4 CAEN - DT5780                     | 17 |  |  |  |  |

|   |                                                  | 1.3.5 ADSP-2183 for MINIBALL            | 18 |  |  |  |  |

| 2 | Ana                                              | Analog-to-digital converters overview   |    |  |  |  |  |

|   | 2.1                                              | Quantization error in ADCs              | 21 |  |  |  |  |

|   | 2.2                                              | Thermal noise                           | 24 |  |  |  |  |

|   | 2.3                                              | Jitter                                  | 26 |  |  |  |  |

|   | 2.4                                              | ADC Architectures                       | 27 |  |  |  |  |

|   |                                                  | 2.4.1 Flash                             | 27 |  |  |  |  |

|   |                                                  | 2.4.2 Single-slope                      | 27 |  |  |  |  |

|   |                                                  | 2.4.3 Wilkinson                         | 28 |  |  |  |  |

|   |                                                  | 2.4.4 Successive Approximation Register | 28 |  |  |  |  |

|   | 2.5                                              | Integrated capacitors                   | 31 |  |  |  |  |

|   | 2.6                                              | SAR ADC state of the art                | 33 |  |  |  |  |

| 3 | Digital Calibration for SAR ADCs                 |                                         |    |  |  |  |  |

|   | 3.1                                              | Superposition Principle                 | 37 |  |  |  |  |

|   | 3.2                                              | Independent Component Analysis (ICA)    | 38 |  |  |  |  |

|   | 3.3                                              | Redundant Double Conversion (RDC)       | 38 |  |  |  |  |

|   | 3.4                                              | Internal Redundancy Dithering (IRD)     | 39 |  |  |  |  |

|   | 3.5                                              | Code density test                       | 39 |  |  |  |  |

|   | 3.6                                              | Offset Double Conversion                | 40 |  |  |  |  |

|   | 3.7  | ation processor                                 | 41                                                                                                                                     |     |  |  |  |  |  |  |  |  |

|---|------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|

|   | 3.8  |                                                 |                                                                                                                                        |     |  |  |  |  |  |  |  |  |

|   | 3.9  | Discre                                          | te Fourier Transform                                                                                                                   | 46  |  |  |  |  |  |  |  |  |

| 4 | Digi | gital Signal Processor for radiation sensors 51 |                                                                                                                                        |     |  |  |  |  |  |  |  |  |

|   | 4.1  | Introdu                                         | uction                                                                                                                                 | 51  |  |  |  |  |  |  |  |  |

|   |      | 4.1.1                                           | Difference between analog and digital implementation                                                                                   | 51  |  |  |  |  |  |  |  |  |

|   | 4.2  | Introdu                                         | uction to digital filtering                                                                                                            | 52  |  |  |  |  |  |  |  |  |

|   |      |                                                 | 4.2.0.1 Linear time-invariant systems (LTI)                                                                                            | 52  |  |  |  |  |  |  |  |  |

|   |      |                                                 | 4.2.0.2 Impulse response                                                                                                               | 53  |  |  |  |  |  |  |  |  |

|   |      |                                                 | 4.2.0.3 Convolution                                                                                                                    | 53  |  |  |  |  |  |  |  |  |

|   |      | 4.2.1                                           | FIR and IIR filters                                                                                                                    | 54  |  |  |  |  |  |  |  |  |

|   | 4.3  | Digital                                         | l Signal Processor overview                                                                                                            | 57  |  |  |  |  |  |  |  |  |

|   | 4.4  | Anti-g                                          | litch system                                                                                                                           | 60  |  |  |  |  |  |  |  |  |

|   |      | 4.4.1                                           | Self-adjustable thresholds                                                                                                             | 62  |  |  |  |  |  |  |  |  |

|   |      | 4.4.2                                           | Square root computation: the bisection algorithm                                                                                       | 63  |  |  |  |  |  |  |  |  |

|   | 4.5  | Baselin                                         | ne subtraction                                                                                                                         | 65  |  |  |  |  |  |  |  |  |

|   | 4.6  | Pile-up                                         | p                                                                                                                                      | 69  |  |  |  |  |  |  |  |  |

|   |      | 4.6.1                                           | Pile-up rejection circuit                                                                                                              | 69  |  |  |  |  |  |  |  |  |

|   | 4.7  | Digital                                         | $1 \mathrm{CR} \cdot \mathrm{RC}^4$ pulse shaper $\ldots \ldots \ldots$ | 71  |  |  |  |  |  |  |  |  |

|   |      | 4.7.1                                           | Charge sensitive amplifier                                                                                                             | 71  |  |  |  |  |  |  |  |  |

|   |      | 4.7.2                                           | Digital shaper description                                                                                                             | 73  |  |  |  |  |  |  |  |  |

|   |      | 4.7.3                                           | Pole zero cancellation                                                                                                                 | 75  |  |  |  |  |  |  |  |  |

|   |      | 4.7.4                                           | SNR                                                                                                                                    | 77  |  |  |  |  |  |  |  |  |

|   |      | 4.7.5                                           | Fixed-point representation                                                                                                             | 79  |  |  |  |  |  |  |  |  |

|   | 4.8  | Decon                                           | volution                                                                                                                               | 80  |  |  |  |  |  |  |  |  |

|   |      | 4.8.1                                           | Mobile Window Deconvolution                                                                                                            | 80  |  |  |  |  |  |  |  |  |

|   |      |                                                 | 4.8.1.1 Energy extraction                                                                                                              | 83  |  |  |  |  |  |  |  |  |

|   |      | 4.8.2                                           | Charge extraction                                                                                                                      | 87  |  |  |  |  |  |  |  |  |

|   | 4.9  | Time p                                          | pick-off                                                                                                                               | 87  |  |  |  |  |  |  |  |  |

|   |      | 4.9.1                                           | Jitter                                                                                                                                 | 88  |  |  |  |  |  |  |  |  |

|   |      | 4.9.2                                           | Leading edge                                                                                                                           | 92  |  |  |  |  |  |  |  |  |

|   |      | 4.9.3                                           | Zero crossing discriminator                                                                                                            | 94  |  |  |  |  |  |  |  |  |

|   |      | 4.9.4                                           | Constant fraction discriminator                                                                                                        | 94  |  |  |  |  |  |  |  |  |

|   |      | 4.9.5                                           | Least square minimization and interpolation                                                                                            | 98  |  |  |  |  |  |  |  |  |

|   |      | 4.9.6                                           | Goldschmit's algorithm                                                                                                                 | 100 |  |  |  |  |  |  |  |  |

| 5            | Physical implementation |         |                                                  |     |  |  |  |  |  |

|--------------|-------------------------|---------|--------------------------------------------------|-----|--|--|--|--|--|

|              | 5.1                     | Calibra | ation processor implementation                   | 104 |  |  |  |  |  |

|              |                         | 5.1.1   | Serializer                                       | 106 |  |  |  |  |  |

|              |                         | 5.1.2   | Simulation results                               | 107 |  |  |  |  |  |

|              |                         | 5.1.3   | Test chip results                                | 111 |  |  |  |  |  |

|              |                         | 5.1.4   | Power analysis                                   | 118 |  |  |  |  |  |

|              | 5.2                     | Digital | signal processor implementation                  | 125 |  |  |  |  |  |

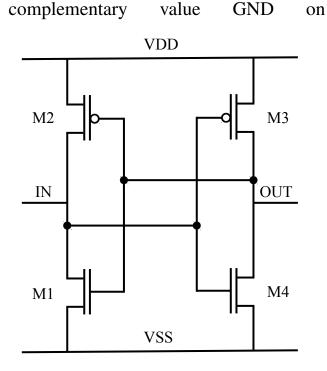

|              |                         | 5.2.1   | Radiation hardness                               | 125 |  |  |  |  |  |

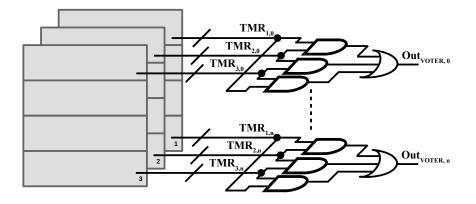

|              |                         | 5.2.2   | SEU mitigation techniques                        | 128 |  |  |  |  |  |

|              |                         |         | 5.2.2.1 Triple Modular Redundancy implementation | 128 |  |  |  |  |  |

|              |                         |         | 5.2.2.2 SEU and MBU simulations                  | 131 |  |  |  |  |  |

|              |                         | 5.2.3   | Simulation results                               | 131 |  |  |  |  |  |

|              |                         | 5.2.4   | Power analysis                                   | 137 |  |  |  |  |  |

| 6            | Data compression        |         |                                                  |     |  |  |  |  |  |

|              | 6.1                     | Compr   | ression techniques                               | 146 |  |  |  |  |  |

|              |                         | 6.1.1   | Run-Length Encoding                              | 147 |  |  |  |  |  |

|              |                         | 6.1.2   | Huffman tree                                     | 147 |  |  |  |  |  |

|              |                         | 6.1.3   | Delta encoding                                   | 150 |  |  |  |  |  |

|              | 6.2                     | RD53A   | A                                                | 154 |  |  |  |  |  |

| 7            | Conclusion and outlooks |         |                                                  |     |  |  |  |  |  |

|              |                         | 7.0.1   | Future perspective                               | 162 |  |  |  |  |  |

| Bibliography |                         |         |                                                  |     |  |  |  |  |  |

# Chapter 1

# ASIC architectures for radiation sensor read-out

A radiation detector is a device designed to capture the interaction of an impinging particle, converting part of its energy into a suitable electrical signal. This event is characterized by some features such as signal amplitude and time of occurrence that can be extracted with appropriate data manipulation. To get the idea we can think of a common digital camera. The light source coming from the environment is collected, then it is converted into an image that freezes its information on a memory bank. The image contains a representation of space features related to the status of the surrounding world at a given time. Radiation detectors are widely used in many fields, from astrophysics to high-energy physics or medical applications. In order to record and analyze the interactions, an appropriate front-end electronics coupled with the sensor is necessary. To achieve high performance in terms of energy discrimination, spatial accuracy and timing resolution, the sensor area is partitioned into many independent channels. This implies a massive parallelism in the processing of the generated data. Such technological challenge can be fulfilled through the implementation of Application Specific Integrated Circuits (ASIC), in Very Large Scale of Integration (VLSI) technologies.

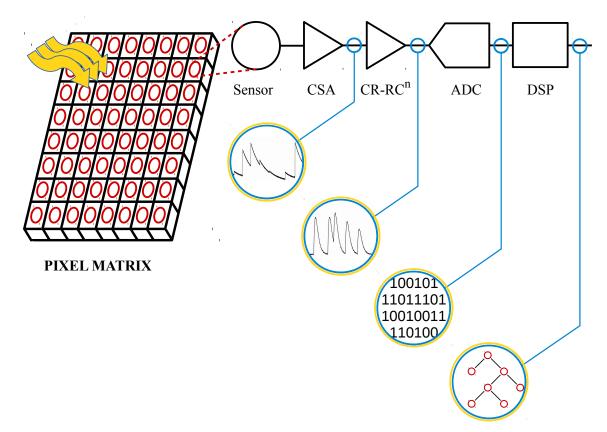

Figure 1.1 depicts a typical acquisition channel that is primary formed by the sensor which is the sensitive area where the interaction occurs. In the case represented in the picture, the sensors are organized in a pixel matrix where each unit is independent from the others. When the signal is formed, its amplitude could be too small to be directly manipulated by the following electronics. Thus, a first stage amplifies the original signal to be fed to the next blocks. In the image this role is accomplished by a Charge Sensitive Amplifier (CSA). In a straightforward implementation, the CSA output is filtered and digitized by an Analog-to-Digital converter (ADC). Therefore, the data can be further elaborated on-chip with a Digital Signal Processor (DSP) to extract the features of interest . Eventually, also data compression schemes can be applied on the processed values to satisfy specific data transmission requirements. Alternatevely, the converted samples can be directly sent out off chip and acquired by a Field Programmable Gate Arrays (FPGA).

Figure 1.1: Block representation of a typical read-out channel composed by a sensor, a preamplifier stage (CSA), a pulse shaper (CR-RC), an analog-to-digital converter (ADC) and a digital signal processor (DSP).

#### 1.1 Radiation sensors

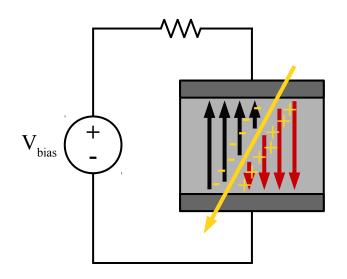

Many different types of radiation sensors are employed, depending on the application and its requirements. Due to the complexity and broadness of the topic, only key aspects relevant to front-end electronics design are discussed here. More detailed explanations about these devices can be found in the references quoted in the bibliography [1] [2] [3]. An interesting description of the history of particle detectors is also available in [4]. The basic understanding of the sensor properties as well as of the specific application needs is a critical step to properly optimize the design of the front-end. In Figure 1.2 a representation of a ionization chamber is reported, where two conductive plates (the grey darker strips) confine a sensi-

3

tive material (the grey lighter zone). In order to maintain an electric field within this volume, a voltage  $V_{bias}$  is applied between the two electrodes. The volume which defines the sensitive part of detector can be filled by gasses or their mixture.

Figure 1.2: Representation of an ionization chamber.

However, semiconductor materials, and silicon in particular, became more and more popular in the recent decades. Insulator materials are not suitable to be employed because of the polarization phenomenon. When a charged particle or a photon crosses the sensor, its interaction with the atoms of the device generates electron-ion pairs if the volume is formed by a gas and electronhole pairs in case of a semiconductor. If a photon is energetic enough, it can set an electron free. This electron loses in turn its energy by ionization

in the medium, thus creating a detectable signal. It is fundamental to highlight that the detected signal is due to the induction of the charge carriers that move inside the sensitive volume and it is not formed by their collection at the electrodes. Indeed, when the conductive plates gather all the charges, the signal is no longer observable by the front-end electronics. For a comprehensive analysis of this process the reader is referred to [5]. If the sensor is not equipped with an internal amplification system, the signal is generated by the primary charges originated after the interaction. The charge released can be considerably small. For instance, in a silicon detector, the charge can be  $5 \cdot 10^{-17}C$  in case of 1 keV x-ray and  $4 \cdot 10^{-15}C$  for a minimum ionizing particle traversing a 300  $\mu$ m thick device. When the sensor is composed by a gas, the signal is not strong enough to be detected therefore a further ionization is required. The process that strengthens the signal is the avalanche one which takes place when the weak primary charge is driven into a region of a high electric field. A third class of sensor is represented by multi-stage systems. An example is given by a scintillator crystal which absorbs a gamma ray, partially converting its energy into visible or near UV photons. The latters are thus collected by a photon detector exploiting the well-know photo-electric effect.

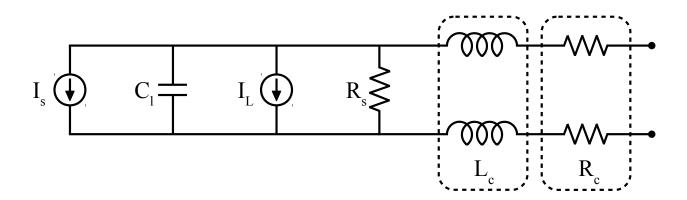

Figure 1.3: Modelling of a generic radiation sensor with an equivalent small signal circuit.

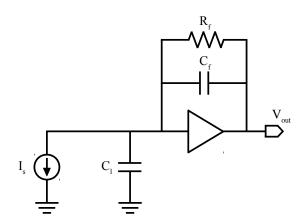

In general, a sensor can be modelled with the equivalent small signal circuit reported in Figure 1.3. Here, the current source  $I_s$  represents the sensor signal, while  $C_l$  is the capacitive load that the sensor presents to the front-end electronics. The electronic noise is closely related to this capacitance, thus sensors with smaller capacitance allow for better Signal-to-Noise ratio (SNR).  $I_L$  is another current source that models the leakage current. This quantity is also important to consider because in some application the sensor is DC coupled to the front-end amplifier. The leakage current is especially relevant for semiconductor devices since thermal process produces electron-hole pairs inside the depletion region that are later collected by the electrodes. In some cases, such as with Germanium detectors, a cooling system is mandatory to keep the leakage current low enough. The leakage current contributes also to the noise because the generation of the pairs is in itself a random process. Furthermore, it can even determine a sizeable shift of the DC operating points of the front-end amplifier. This issue can be fixed either by AC coupling or by adopting dedicated methods to compensate this undesired effect [6] [7] [8].  $R_s$  is used to describe the intrinsic output impedance of the sensor or the physical resistor adopted to provide the bias voltage. Lastly,  $L_c$  takes into account the parasitic inductance and  $R_c$  the parasitic resistance of the connections. The model introduced so far is a generalization suitable for a large number of detectors, however the value of the parameters depends on the specific sensor design and its operating conditions. For instance, the  $I_s$  which models the timing evolution of the signal can be described by a Dirac-delta in the simplest case or can be defined as a composition of exponential terms.

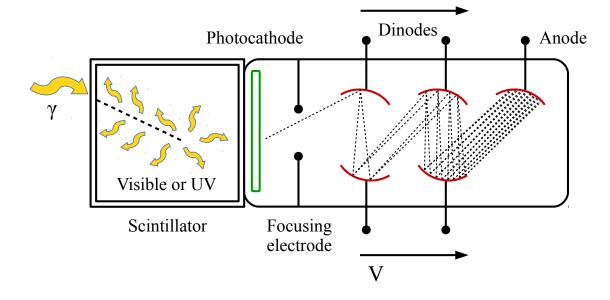

In the following, three examples of radiation sensors will be discussed to show the validity of the presented model. The first one belongs to the composite class and as introduced before it is formed by two parts. Figure 1.4 illustrates the concept of a vacuum Photomultiplier Tube (PMT) which is still today one of the most popular devices to detect single photons.

Figure 1.4: Representation of a vacuum photomultiplier tube (PMT).

The scintillator is composed by a material that absorbs the gamma ray and reemits photons at a lower energy along the ionization path. When one of these visible or near UV photons reaches the photocathode an electron is emitted and it is focused toward the inner part of the tube by an electrode. Other electrodes named dynodes are located between the photocathode and the anode and their task is to generate a second emission. Each dynode is connected to an increasingly intense voltage in order to produce an exponential multiplication due to the avalanche process. In this way from a single photoelectron a million of electrons that are collected at the anode can be produced. The induced current on this last electrode forms the signal observed. The model previously described works well to represent this device. Here the capacitance is composed by that one between the last dinode and the anode and the capacitance generated by the interconnections.

A second example of detectors is represented by the gas-based sensors that are still very interesting for the scientific community due to the their low cost compared to the instrumented area. As explained before, this kind of devices suffers of a weak signal when implemented without an amplification mechanism. Thus also in this case a suitable electric field is applied to exploit an avalanche effect in order to generate more carriers. The intent is to guarantee a proportionality between the primary charge originated by the initial interaction and the detectable signal. Since the length of the avalanche is a function of the creation point of the initial charge, if an equivalent energy is deposited in different regions of the detector the output signals will be characterized by different amplitudes. In other words, it will no longer be possible to maintain a linear measurement. Therefore, the strategy is to bound the avalanche process to a defined region and this result can be obtained with a cylindrical geometry, where the multiplication effect is confined to a volume around a thin wire that acts as the anode. If more than one wire is used, the device is referred as multi-wire proportional chamber (MWPC) where the charges are drifted towards the anodes by the applied electric fields, inducing the signal with a multiplication factor between  $10^4$  and  $10^5$ . Other solutions have been developed to increase the space resolution as well as the rate such as the Gas Electron Multiplier (GEM). These devices include in the sensitive volume a series of Kapton foils coated with Copper. Holes are opened on these surfaces that are held at a high potential difference. The diameter of the holes is typically in the range of 50 - 70  $\mu m$  with a pitch between 150  $\mu m$ and 200  $\mu m$ . The generated electric field collects the primary charges by drift and when they cross the first foil the multiplication starts. The process is iterated on the second Kapton surface and goes on until the collecting electrode where the signal is induced. The sensor capacitance  $C_l$  is around 50 pF, depending on the area of the landing pad.

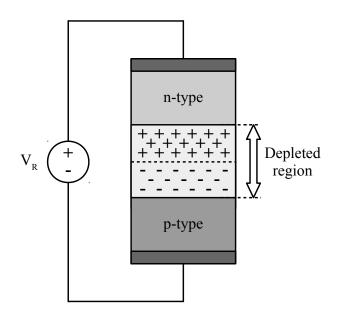

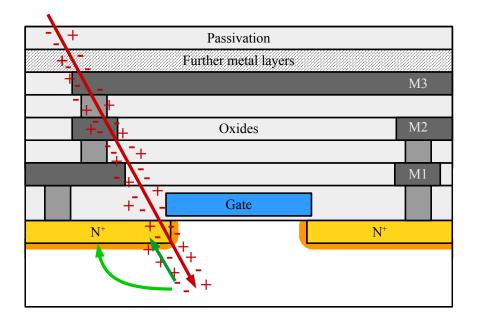

Semiconductor-based detectors are the last class of detectors considered. Their basic structure is shown in Figure 1.5 where a so called *pn junction* representation is reported [9]. This is formed by the doping process of a semiconductor crystal, namely, when a certain concentration of impurities are introduced into the crystalline structure to improve its conductivity. The concentration range is between  $10^{12}$  -  $10^{18} cm^{-3}$ . Silicon is a tetravalent atom. If a pentavalent atom is introduced in the lattice, at room temperature the extra electron can be easily promoted to the conduction band due to thermal process and it becomes free to move along the lattice. In this case the dopant, named *donor*, assumes a positive charge and when the semiconductor is doped with this kind of atoms it is referred to as n-type. Conversely, if doping atom is trivalent, a vacancy in the atomic bonds occurs and an additional state is available in the bandgap. Since the energy of this new state is close to the valence band it is particularly easy for the dopant, referred as *acceptor*, to get an electron. Therefore, when the state is filled, a further negative charge is assigned to this atom. At room temperature almost all the dopants states are occupied and the valence band is populated with holes. When the semiconductor is doped with acceptors it is named p-type. Very common semiconductors employed for this kind of detectors are Silicon (Si) and Germanium (Ge), but also compound materials have been explored such as Cadmium Zinc Telluride (CdZnTe). To realize a n-type Phosphorus (P), Arsenic (As) and Antimony (Sb) are commonly used, while Boron (B), Aluminium (Al), Gallium (Ga) and Indium (In) are usually chosen for p-type doping.

Figure 1.5: Representation of a reverse-biased semiconductor junction.

When these dopants are implanted on the same semiconductor (we consider here silicon) a junction is formed. At the beginning, each side is neutral from an electric point of view. However, the diffusion starts to transport the holes from the p-region towards the n-side, while electrons migration occurs in the opposite direction. As illustrated in the figure, this process leaves a positive charge on the n-side and a negative counterpart on the ptype region, respectively. Therefore, this process builds up a potential and the equilibrium is established when the force exerted by the uncovered

dopant atoms compensates the thermal diffusion, limiting further migration of the carriers. Thus, the built-in potential creates a region across the junction named depletion region where the net current is zero. This voltage exhibits a dependence on the dopants concentration and the temperature. The depleted volume is almost free of mobile carriers, therefore it acts as a dielectric, and the undepleted sides behave as conductive electrodes since they are populated by free carriers. Because the internal electric field of the depleted volume sweeps the mobile carriers towards the plates, this device is actually an ionization chamber where the width of the depletion region can be increased by applying a reverse bias voltage  $V_R$  as shown in Figure 1.5. Hence, when a particle releases energy into the active volume electron-hole pairs are generated and their number is proportional to the deposited energy. When the mobile charged carriers are moving in the sensitive region, a current signal is inducted on the electrodes and the event can be detected. Since this kind of sensors provide a better energy resolution than the previous described classes, they are exploited for X and gamma-ray spectroscopy. In these studies the highly penetrating radiation is investigated, so the sensor must be thick enough to offer a suitable stopping power. For energy below 30 keV the Silicon can be adequately prepared for this task by drifting Lithium ions into the substrate. In this way the impurities trapped in the bulk are compensated and the Silicon acts as an extremely pure crtystal leading to a depletion depth of several millimiters. To explore higher energy the Silicon must be substituted with Germanium, but these detectors demand a cooling system. Compound semiconductor solutions are located halfway between an acceptable efficiency in the high energy range and room temperature operation and an examples is represented by Cadmium Zinc Telluride (CdZnTe).

Silicon detectors are also suitable for the detection of low-level light, an example being provided by avalanche photodiode (APD). Similarly to the previous processes described for the other detectors, the electric field drives the electron-hole pairs created by the photons towards an avalanche region where the impact ionization determines the extraction of other charged carriers with a gain in the range of 100 - 1000. This interval is sufficient to spot a small number of photons, however single photon sensitivity is not achieved. To detect even the single interaction the electric field of these devices can be appropriately strengthened. These detectors are called Single Photon Avalanche Diode (SPAD) or Geiger-mode Avalanche Photodiode (GAPD). They incorporate a quenching resistor  $R_Q$  in series with the diode to suppress the avalanche process. The voltage at the cathode equals a bias voltage when there is no current. If the latter is increased, the voltage across  $R_Q$  brings the cathode voltage below the breakdown point. Unfortunately, this implementation returns a constant output which is independent of the photons in the sensitive volume. To recover an output proportional to the number of incident photons a segmentation of the detector can be adopted. The analog Silicon PhotoMultipliers (SiPMs) presents a structure composed by array of parallel and independent units named microcells whereas the output is obtained as the sum of the signals produced by each diode. To have a small probability of more than one interaction into a single cell, the cell area is around 50  $\mu m \ge 50 \mu m$ . In this topology, the number of firing microcells is equivalent to the number of incident photons and due to their high spacial resolution the SiPMs replaced the photomultiplier tubes in those applications where high granularity and high magnetic field are required. Both the space and time resolution can be exploited to obtain 3D images, deriving the third coordinate with time of arrival measurements. A large number of microcells can be accomodated in parallel, thus the capacitance of these detectors is between 30 pF and 300 pF and the model previously discussed is not valid anymore because the rise time of the signal could be overstimated. However, the literature offers more accurate model description of SiPMs [10]. Finally, CMOS technologies can be used to implement GAPD and they are referred to as digital silicon photomultiplier. Each cell of these device is read-out separately with a very small capacitance which improves the timing performance. In general, the

electrodes of a detector can be arranged in different segmentations to obtain a space information about the event. The simplest structure is the partition of the electrodes into strips where the position of a hit is intrinsically one-dimensional. When a tilted particle deposits its charge on more than one strip it is possible to get a better spatial resolution through an interpolation exploiting the ratio between the collected charges on those strips. To increase the spatial resolution up to two-dimensions a further orthogonal segmentation can be implanted. The distance between the centers of two adjacent strips is named pitch. Its value is between 25 and 100  $\mu m$  in collidingbeam experiments, while the lengths of the strips array starts from centimeters up to 30-40 cm. This sensors organization may suffer of "ghosts" hits at high densities, but this problem can be mitigated adopting a small-angle stereo, where the strips are not perfectly located at 90° as further described in [9]. Another way to achieve two-dimensional information without this kind of compromise is the pixelization of the sensor such as in the case of Charge Coupled Device (CCD) and random access pixel device. Thus, in a possible implementation, the electrodes are segmented into a surface that resembles a chessboard and each partitioned volume is physically connected with solder bumps to a dedicated readout electronics organized in a specular segmentation. The pitch of the pixels is typically between 30 and 100  $\mu m$ , however the pixel size is constrained by the associated readout unit. Moreover an additional electronics is required to manage the readout control system which means more area is demanded. Furthermore, the split manufacturing increases the cost because the sensors have to be separately produced from the readout chain. In the case of hybrid pixel detectors, this additional budget is due to the bump bonding process which absorbs around half of the cost. From this point of view, a monolithic structure would be preferable because the sensor shares the same pixel area of the electronics, thus their connections are made during the fabrication, requiring a lower material budget. The pixel pitch is reduced down to 5 - 10  $\mu m$  and the charge collection occurs in a very thin layer, of order  $\mu m$ . When these device are fully depleted (FD), their are named FD-Monolithic Active Pixel Sensors (MAPS) and in the last three decades they became increasingly of interest for particles detection, high-energy photons imaging as well as tracking in space experiments and medical applications. Some examples can be found in [11] [12] [13]. In the next section, some of the architectures developed for the front-end electronics will be discussed, leaving to Section 4.7.1 the discussion about analog amplifiers as a brief prologue to the digital filters.

#### **1.2** Front-end architectures

As well as the sensors, many front-end architectures have been developed due to the variety of possible applications. Indeed, the purpose of the measurement determines the implementation of a specific electronics to execute a required task. For instance, in High Energy Physics (HEP) tracking detectors the aim is to provide a set of space-points to identify a particle track. In this case, a threshold comparator providing a yes/no decision followed by digital memories can be adequate. By contrast, if the energy evaluation is the main target of the experiment, such as in nuclear spectroscopy, the signal amplitude needs to be sampled with adequate resolution, so a high performance ADC is required. Another possible application is represented by Positron Emission Tomography (PET) where both the time information and the amplitude of the event must be derived. Thus, this section will present a not exhaustive list of common front-end solutions.

- The first architecture presented is also the simplest one and it is named *binary* [14] [15]. Basically, the signal is monitored by a comparator and when it is above a configured threshold a digital pulse is generated, neither processing nor storing the amplitude. Therefore, this system is suitable to get space information about the hit channels of a detector. The hits are then stored in digital memories and queued for readout. In most cases, a sparsified approach is adopted, and only the channels that fired within a given time window are readout, suppressing the zeroes.

- As introduced before, some applications require the extraction of other informations rather than the position of an event. In the case of X-ray imaging the quantity of interest is the intensity of the incident radiation [16] [17]. A *counting architecture* can address this need equipping the comparator with a counter to record the number of events occurred in a desired time frame. In this implementation two critical aspects must be considered when designing the counter. The first one is due to the switching activity because if many bits switch at the same time they can generate an higher noise. The other possible issue concerns the storage of the counter value when it is sampled since an error during this step can result into an incorrect extracted value. To get the idea, let's consider a 4-bits counter and the transition from 0111 to 1000. If a bit-flip occurs to the first bit which is the most significant one, the data recorded will be 0000. This means that the error is quantifiable as half of the whole dynamic range. To fix this potentially severe problem, pseudo-random counters can be adopted to limit the number of simultaneous transitions. Using Gray codes is useful as well

#### 1.2. FRONT-END ARCHITECTURES

because the Hamming distance between two consecutive counts is always equal to one.

- A simple approach to derive the amount of charge released by the particle in the sensor is to measure the time spent over a preset threshold by the amplifier signal. Under appropriate conditions, this time interval is proportional to the magnitude of the detected signal. Thus in binary front-ends the width of the comparator pulse can be measured to infer the charge information. In these systems, a common time-stamp is generated and distributed to the channels. The time-stamp is very often provided by a Gray counter driven by a reference clock. The time at which the leading and trailing edges of the comparator signal occur are then captured by dedicated registers in the firing channel. This method is referred to as *Time over Threshold (ToT)* and it widely reported in the literature [19] [18].

- *Time pick-off* systems must be employed when timing information are crucial in the application [20] [21]. This is the case of the particle identification in HEP and PET, where the time of flight of charge particles or photons needs to be measured with a resolution better than 100 ps. In this scenario a counting mechanism as the one described above is unsuitable because the clock frequencies would be in the range 5 10 GHz. Hence, while a counter still provides a coarse time base, the time elapsing between the event and a suitable clock transition must be measured by an interpolating circuit. A Time-to-Digital Converter (TDC) is a device able to assign this kind of digital tag to a selected time window with a resolution that today can even exceed 1 ps.

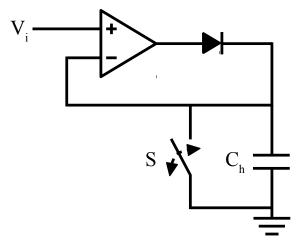

- While the previous architectures only store digital information, there are other approaches in which substantial more analog signal processing is carried out. A typical example is provided by the *sample and hold* systems where a hold capacitor is located between the front-end output and the read-out circuit. Its connections with the input stage and the output one are controlled by switches. As their name suggests, this topology works in two steps: during the acquisition process the input switch of the capacitor is closed, directly connecting it to the front-end, while the output switch is open. If a peak is observed, its value can be stored on the capacitor by opening the first switch. When the detected values have to be read, the output switch is closed in order to digitize it on-chip or to send it out still in analog form. The peak of a signal is the sample-target of a front-end designed with a continuous-time transfer function because this point has the highest SNR. To detect it, both the peaking and the sampling times must

Figure 1.6: Representation of a peak detector

Figure 1.6 illustrates the concept of the *peak detectors* that are used for this purpose. At the non-inverting input (+) of the operational amplifier the frontend output  $V_i$  is presented, while the output of the op-amp forms a negative feedback with the inverting terminal (-) where an unidirectional component is added (shown as a simple diode in the figure). The switch S acts as a reset for the hold capacitor  $C_h$ , thus when it is closed  $C_h$  is discharged to ground. If  $V_i \leq 0$  no signal is coming from the front-end and the diode is off, namely, the inverting input of the op-amp is zero. Otherwise, the diode is turned on because the difference between  $V_i$  and the negative terminal is amplified. Thus, the circuit works as a voltage follower and the voltage on  $C_h$  tracks the input one. Once the peak is overstepped, the derivative of the signal becomes negative since  $V_i$  is returning back to the baseline. Now the voltage on the hold capacitor will not follow the input signal. In fact, to track again the amplifier input the voltage on  $C_h$  should be reduced, but this would imply to sink current from the feedback path. Since the diode is unidirectional, the voltage on the inverting terminal becomes fast larger than  $V_i$ . Consequently, the output of the amplifier is pulled down and the diode itself turns quickly off while the peak value is stored in the hold capacitor. In a CMOS implementation, the diode function is implemented with a transistor and on-silicon examples of this are reported in [22] [23]. To reduce the dead time, a discriminator per channel is associated to both sample and hold and peak detectors to point out when a hit occurs. This addition allows for a sparsified readout. To further shrink the dead time, a strategy is to increase the number of storage cells available in each channel.

be synchronized.

In this way, when a cell is already busy, another one can be available to store a new peak value.

• The last example of architecture reported is the *analog memories*. Typically, these devices are formed by an array of capacitors, each one equipped with switches for the writing and reading operations. A sample and hold process allows to implement the writing, tracking the output of an amplifier and then storing its value in a single memory unit. When this cell have to be read out, the capacitor is usually connected in the feedback path of an op-amp. A final reset clears the cell, making it available for a new writing. An advantage of analog memories is the possibility to record a full waveform, recognizing specific features such as signal pile-ups. By contrast with an analog to digital conversion process, these devices are characterized by a lower power consumption and for this reason they are suitable to capture fast transients. The acquired values can be converted either on-chip [24] or off-chip [25] at a lower speed when an interesting event is detected.

Depending on the application, the capacitors can be implemented in CMOS processes exploiting metal-metal or MOS version. The first ones are characterized by an high linearity and a quick response, but as a drawback they have a small density around 1  $fF/\mu m^2$ , making them a good choice for high speed applications. The alternative represented by the MOS capacitors is denoted by an higher density even above 5  $fF/\mu m^2$ . On the other hand, this kind of capacitors are affected by a poor linearity and a smaller speed compared to the metal-metal counterpart. Thus, they are suitable when many units per channel are required. Another aspect to take care of is the sequencer used to control the sampling switches. An approach is to use the clock signal to drive a shift register, using it as pointer in the writing process. Another strategy can be the employment of a digital delay line which is a chain of digital buffers eventually arranged in a closed loop. In this configuration, the buffer propagation delay sets the time difference between two consecutive samples and in CMOS nodes it can achieve values smaller than 100 ps. Hence, this approach becomes interesting for applications where a very fast sampling is demanded.

#### **1.3** Full sampling systems

By "full sampling systems" we mean in this context systems in which an ADC follows immediately the front-end amplifiers and all the relevant signal processing is carried-out in the digital domain. For many years, the power consumption of ADCs represented the bottleneck for full-sampling systems since an on-chip analog to digital conversion with an acceptable resolution required a power budget not affordable by most applications. However, in the last decade the substantial improvement of ADCs power figure has made full-sampling solutions progressively more appealing. In general, ADCs resolution in the range of 6 - 10 bits combined with a sampling rate between 50 - 100 MS/s are adequate for most applications. In this context, a readout channel can be equipped with a Digital Signal Processor (DSP) to locally select and manipulate the generated data. These tasks can be achieved with configurable thresholds to reject the undesired values and implementing specific filters to extract useful information from the digitized signals such as the energy or the time when the event occurs. This approach leads to a more accurate data processing compared to the analog counterpart because it is not affected by the tolerances of the components. In a digital system the attained precision depends in fact on the algorithm and on the numerical representation. Furthermore, it is possible to program the key parameters of a filter, eventually adjusting them after the fabrication step. Last but not least, state of the art CMOS processes are primarily conceived for digital applications. In the following, the state of the art of full sampling systems is described.

#### 1.3.1 ALTRO

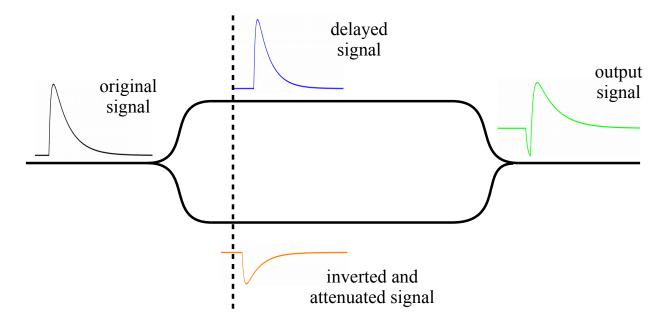

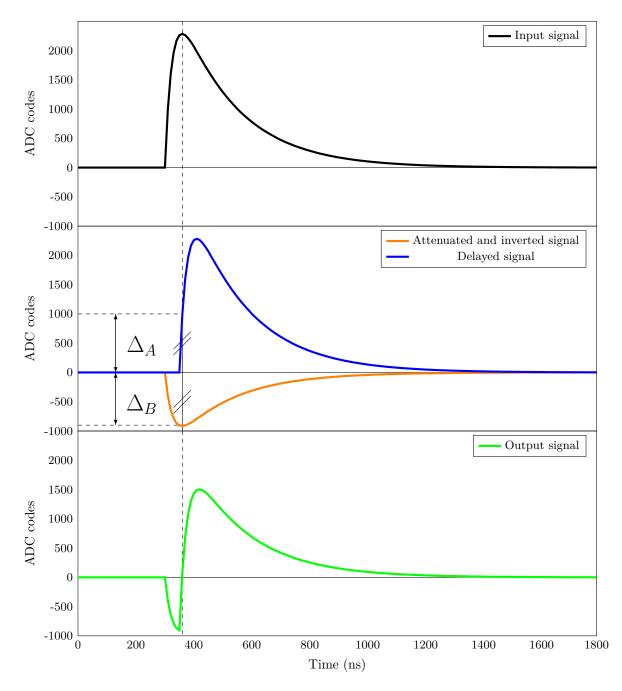

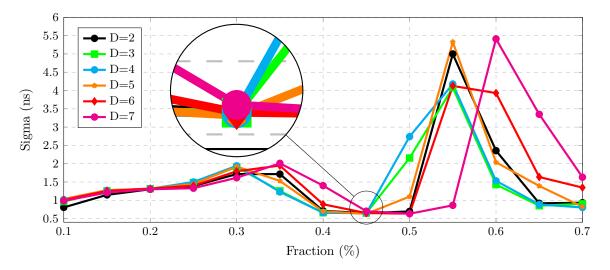

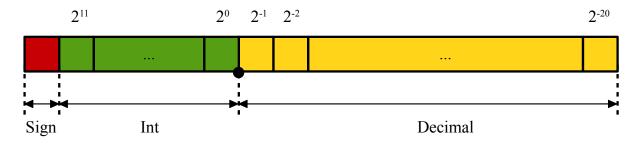

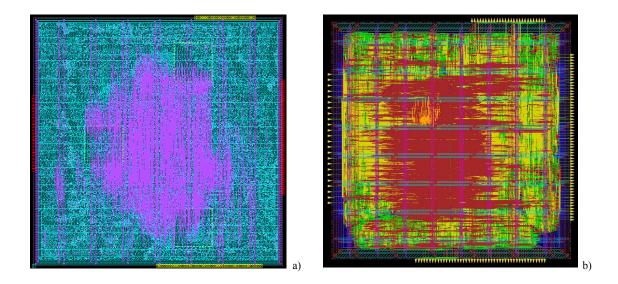

The ALICE experiment is one of the four major detectors equipping the CERN Large Hadron Colliders (LHC), located near Geneva, Switzerland. In particular, ALICE stands for A Large Ion Collider Experiment and it is a detector designed and optimized to study the collisions of ions at ultra-relativistic energies [26]. The three-dimensional reconstruction of the particle tracks is provided by Time Projection Chamber (TPC) which is a cylindrical gas volume held to a uniform electrostatic field. With the process described in Section 1.1, the charged particles ionize the gas and they generate charged carriers later collected by the electrodes. The induced signal has a rise time smaller than 1 ns and a long tail. The latter bounds the event rate since pile-up effects can occur. Because of this the front-end electronics must implement a tail cancellation procedure. This is accomplished by the ALICE TPC Read Out (ALTRO) chip which is a mixed-signal custom integrated circuit designed for gas detectors readout [27] [28]. The chip was fabricated in a 0.25  $\mu m$  CMOS process and it is formed by 16 channels where independent signals are acquired by an equivalent number of 10-bits ADCs implemented on chip. Then they are digitised and processed to be finally compressed and stored in a multi-event acquisition memory. The chip area is 64 mm<sup>2</sup>, while the power consumption is 320 mW at 10 MHz sampling rate. The DSP partitioned the algorithms in pipelined stages where the first

one is dedicated to a first baseline correction. At this stage, the digitized signal is manipulated by removing both the low-frequency perturbations and systematic effects to prepare the data for the tail cancellation. Low-frequency spurious signals are up to one kilohertz and they introduce a baseline shift in the order of one ADC count. This kind of perturbations can be generated by the temperature variation of the electronics, while the systematic effects are noise patterns that are superimposed to the original signal. For instance, the trigger of a detector can introduce this signal variations. Due to their nature, they can be removed implementing a pattern memory. Here the input signal is corrected subtracting a set of values previously stored onchip. Then, the tail cancellation task is accomplished in the following stage where a filter was designed to remove the tail of a pulse within 1  $\mu s$  after its peak. The signal was approximated by the sum of 4 exponential functions and consequently a transfer function in the Z domain was obtained. This suppression takes advantages of the digital implementation since the filter coefficients are configurable, thus the system can cover a wide range of different tail shapes. Then, a second baseline correction mechanism was carried out exploiting a moving average filter that adjusts the nonsystematic perturbations of the baseline [29]. Because at the output of this step the baseline is constant within 1 LSB, a simple zero suppression scheme was adopted. In this way, the data below a programmable threshold are rejected, avoiding to readout meaningless information. Finally, the chip also manages the data formatting where each packet is assigned its time stamp and size information for the off-chip reconstruction. The 5 kbyte data memory was designed to record up to eight acquisitions and the maximum readout frequency is 60 MHz for a a total bandwidth of 300 Mbyte/s.

#### 1.3.2 Super ALTRO

Super ALTRO (S-ALTRO) was the natural evolution of the ALTRO chip described above. It is a demonstrator that shares the same digital processing such as the baseline restoration and the tail cancellation, but enhancing their performance in terms of power consumption, flexibility, digital noise and stability. A key feature of the S-ALTRO is that it implements on board also the front-end amplifier. The main efforts during this optimization process were put on the digital shaper designed for the undershoots and tail cancellations, since this block accounted for 84% of the digital power budget. A detailed analysis of the IIR filter architectures can be found in [30] where the hardware improvements lead to a gates reduction of 2/3 compared to the ALTRO implementation. Other aspects were also considered for the optimization of the first baseline correction mechanism and the SNR of this stage was incremented by 1.5 dB. However, this results in an increased hardware resources of slighly less than 8%. Since this block is particularly small in comparison to the whole digital processor, this variation is not significant. As well as the first baseline correction, also the second one was improved both on flexibility and digital noise reduction at the cost of 4% more hardware resources. Therefore, the overall hardware resources have been decreased by 20%, while the SNR shown a positive increment of 7.9 dB. Lastly, the power consumption was reduced to 40% changing the power supply from the nominal 1.2 V to 0.8 V at the working frequency of 40 MHz. Under this reduction, the delays increased, but without impairing significantly the overall performance.

After this architecture and hardware review, a prototype has been fabricated in 130 nm CMOS technology which occupies an area of 5.75 mm by 8.56 mm [31]. As its predecessor, S-ALTRO implemented 16 channels where the ADCs have 10-bits resolution and they work up to 40 MHz of sampling frequency. Each channel is equipped with a dedicated memory able to store up to 1000 samples for a maximum time duration of 100  $\mu s$  at 10 MHz sampling rate or 25  $\mu s$  at 40 MHz. For a single 10-bits sampled data, the internal data formatting system generates a 40-bit stream which provides a header, a trailer, the time stamp of the event, the configuration information during the acquisition and a set of error flags. The recorded data structure of 80 kbyte can be read out at the maximum frequency of 80 MHz, leaving a dead time of 0.2 ms. The DSP block consumes 65 mW during its normal mode, accounting 4.04 mW/channel.

#### 1.3.3 SAMPA

Periodic LHC shutdowns have been planned to provided the necessary time for accelerator updates in order to achieve higher luminosity and ultimately higher event rate. As a consequence, all the LHC experiments were also upgraded. For what concerns ALICE, an upgrade of its TPC electronics was scheduled in order to enhance the readout capability by two orders of magnitude, thus achieving 50 kHz event rate in Pb-Pb collisions [32]. The efforts to replace the previous front-end led to a new ASIC called SAMPA [33] [34]. Thus, this chip represents the further development of ALTRO and it doubled the number of channel to 32 although the same channel components were maintained: a charge-sensitive pre-amplifier (CSA) is followed by a shaper, then a 10-bit ADC samples the signal at 10 MS/s and a DSP collects and manages the converted data. Two SAMPA prototypes were fabricated in 130 nm CMOS technology. The DSP block inherited the baseline corrections divided into a IIR filter for the low-frequency baseline variations and a moving average filter for the

faster ones and the digital shaper for the tail cancellation. In addition another baseline correction system based on limited slope baseline tracking was implemented. The purpose of this block is to provide a complementary version of the first two restoring methods that may also substitute them. Beside the zero suppression circuit, a data compression scheme was designed based on Huffman coding. The data formatting unit completes the on-chip digital signal processing.

An irradiation campaign with protons was also carried out [35] to qualify the chip for the expected Total Ionizing Dose (TID) of 2.1 kRad and a flux of 3.4 kHz/cm<sup>2</sup>. The aim of the test was the investigation when soft errors such as the single event upset and hard error as Single Event Latchup (SEL) occur. For more detail about this topic, the reader can skip to Section 5.2.1. Briefly, the SEL is a permanent effect that can cause the overcurrent of a CMOS component, resulting in a fatal damage for the device. The high current is due to the formation of a low impedance path established between the supply voltage and the ground. The issue can be solved by power cycling the circuit. Therefore, the devices under test have not implemented specific mitigation techniques against radiation, however only the second version of the chip showed SEL events. The adequate safety measures were adopted and implemented in the next prototypes.

#### 1.3.4 CAEN - DT5780

Industrial products provide also a large variety of DSP solutions. For instance, CAEN is a well-know company that designs both high/low Voltage Power Supply systems and Front-End/Data Acquisition modules for nuclear and particle physics experiments. An example of their products is represented by the DT5780 family [36]. These boards integrate 2 independent 16k channels Digital Multi Channel Analyzer (MCA) and they are suitable for Gamma and X-ray spectrometry. They can be used with different detectors such as the High Purity Germanium (HPGe) radiation detectors to obtain high energy resolution as well as a PMT-based sensor where the exponential tail is at least few hundreds of ns long. The on-board ADCs have a resolution of 14 bits and the sampling rate is 100 MS/s. CAEN has also developed a firmware to accomplish a digital signal processing, providing both the pulse height for the energy extraction and timing information. A digital trapezoidal filter was adopted to generate a flat top whose amplitude is proportional to the deposited energy. The systems are even able to show slices of the signal for the fine tuning of the pulse height analysis settings. This MCA are equipped also with a baseline restorer with programmable averaging similar to the ALTRO and SAMPA chips . This means that the baseline is calculated by averaging a configurable number of samples before the trapezoid, then its value is held within the time interval of the trapezoidal signal itself to properly correct the filter output. The high frequency noise can be instead reduced with an adjustable moving average filter. Another useful feature is the integrated pile-up rejection system that appropriately manages the trapezoids overlap when the event rate becomes too high. Furthermore, the dual input allows to realize coincidences and anti-coincidences involving other detectors to improve the measurements.

#### 1.3.5 ADSP-2183 for MINIBALL

This overview terminates with the case of an industrial product employed in a physics experiment. Indeed, as tacitly anticipated in the previous section, custom systems are not always designed and implemented for all the possible applications. Here the case of MINIBALL is reported which is an high-resolution detector array that has been operational at the radioactive ion beam facility named HIE-ISOLDE (High Intensity and Energy) at CERN [37] for over 10 years. This spectrometer was formed by an array of 24 six-fold segmented high-purity germanium crystals that were encapsulated and arranged into a conical shape. This high-resolution  $\gamma$ -ray spectroscopy investigated a wide interval of shell models using many Radioactive Ion Beams (RIB) such as  $^{74,76,78}$ Zn,  $^{110,132}$ Sn,  $^{144}$ Xe [38]. The signal formed by a  $\gamma$ -ray is slightly different from what was introduced before since it involves two steps. The interaction between the incident photon and the sensor material can generate a fast electron and a Compton scattered  $\gamma$ -ray or alternatively a fast electron-positron pair. The second step is the familiar process where the charged particle deposits its energy, then an electron-hole pair is produced and a signal is induced on electrodes. Without discussing further details about other aspects of this generation process, a pulse shape analysis is the way to increase the granularity beyond that one resulting from the detector segmentation. Thus, the events were manipulated by a ADSP-2183 Digital Signal Processor (DSP) from Analog Devices [39]. This unit runs at 40 MHz and it is designed to address 16 bit fixed point representation, integrating 80k bytes for the memory. Three computational blocks can independently work on the processor composed by an Arithmetic Logic Unit (ALU), a multiplier-accumulator unit (MAC) and a shifter. A trapezoidal filter have been implemented on the DSP module to extract the energy of a  $\gamma$ -ray and this algorithms will be specifically analyzed in Section 4.8.1. Therefore, the experiment was able to benefit of the digital processing to correct the ballistic deficit which affects the trapezoidal output. The DSP was also used for the pulse shape analysis since in this applications it is important to determine with an adequate accuracy the time when an event occurs. The Modified Linear Extrapolated Baseline Crossing (ML-EBC) method was chosen to perform a linear extrapolation exploiting an acquired sample at the start of the signal and the slope defined by its position. The latter was easily derived because it was calculated as difference between two consecutive samples. These pulse shaping analyses were presented and discussed in detail [40].

## Chapter 2

# Analog-to-digital converters overview

As introduced in the abstract of this thesis, the Analog-to-digital Converter (ADC) is the key device to transfer information from the analog to the digital domain. In a full sampling system, the ADC samples directly the amplifier output and generates a digital stream which is manipulated by the digital signal processing unit. The conversion process is characterized by an intrinsic resolution that reduces the original information and it is affected by several errors due to the non-ideal behavior of the components used in the ADC. When designing the signal processing units, these aspects must be properly accounted for and they will be discussed in the next sections, focusing when appropriate on the successive approximation architecture chosen for this study.

#### 2.1 Quantization error in ADCs

The generic output of an ADC is a digital data represented with a given resolution which is expressed in a number N of bits, leading to a  $2^N$  possible digital codes. Thus, considering a voltage reference  $V_{REF}$  as the full scale range of the ADC, the minimum digital step is named Least Significant Bit (LSB) and it is described by:

$$LSB = \frac{V_{REF}}{2^N} \tag{2.1}$$

Because of the limited resolution, a leak of information occurs during the conversion process. This is true also for an ideal converter, because it stems from the need of approximating a continuous quantity with a finite number of possible codes. This error is referenced to as *quantization error* and it is linked with to the SNR as described in the following.

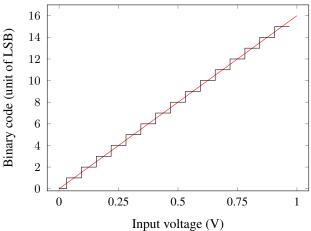

In Figure 2.1 the ideal characteristics of a 4-bits ADC with a  $V_{REF}$  of 1 V is depicted. The red line represents a ramp and it is assumed as the input signal, whereas

the staircase shape is the response of the ADC. The vertical steps point out the transition levels and the horizontal lines between them are the results of the mapping process from the analog to the digital domain. The error is given by the difference between the ramp and the voltage level associated with the n-th code transition. This means that the error increases from a transition level to the following step, defining a typical saw-tooth shape.

In Figure 2.1 the staircase characteristics is right-shifted by LSB/2 from the origin of the system to symmetrize the quantization error. Adopting a ramp as the input signal implies that the output codes will be uniformly distributed on all the bins and the probability density function results to be inversely proportional to the width of the bins. Thus, the RMS quantization error  $V_q$  is given by:

Figure 2.1: Ideal characteristics of a 4 bit ADC

$$V_q = \sqrt{\int_{-\frac{LSB}{2}}^{\frac{LSB}{2}} \frac{x^2}{LSB} \, dx} = \frac{LSB}{\sqrt{12}} \tag{2.2}$$

In general, to define the SNR of a signal we need to know the power of the input signal and the one of the noise. In the case of the SNR of an ideal converter, the quantization error of Eq 2.2 is the denominator of the ratio, while for the numerator the power of a sinusoid is typically used. Sinusoidal waves are a popular choice because they can be generated with very high fidelity. In order to explore all the  $V_{REF}$  range of the quantizer, the sinusoid must have an amplitude  $A = V_{REF}/2$ :

$$V(t) = A \cdot \sin(\omega \cdot t) \tag{2.3}$$

The RMS value is written as:

$$V_q = \sqrt{\frac{\omega}{2\pi} \int_0^{\frac{2\pi}{\omega}} \left[\frac{V_{REF}}{2} sin(\omega \cdot t)\right]^2 dt}$$

(2.4)

The integral can be solved recalling the remarkable integral:

$$\int_{0}^{2\pi} \sin^2(x) \, dx = \pi \tag{2.5}$$

Hence, the RMS value of the input signal is defined as:

$$V_q = \frac{V_{REF}}{2\sqrt{2}} \tag{2.6}$$

and the SNR is simply the ratio of Eq 2.6 and Eq 2.2:

$$SNR_{dB} = \frac{\frac{V_{REF}}{2\sqrt{2}}}{\frac{V_{REF}}{2^N\sqrt{12}}}$$

(2.7)

where the quantization levels have been considered with  $2^N$ . Eq 2.7 can be rewritten as:

$$SNR_{dB} = 20 \log \sqrt{\frac{3}{2}} + 20 N \log 2$$

=  $6.02N + 1.76 dB$  (2.8)

Eq 2.8 defines the signal-to-noise ratio for an ideal converter. If the SNR is known, the equation can be overturned to find the number of bits:

$$N = \frac{SNR - 1.76}{6.02} \tag{2.9}$$

However, in place of SNR the Signal-to-noise and Distortion (SINAD) is usually employed. SINAD is derived by the spectrum analysis of the ADC output when a sinusoidal wave is provided as the test signal. It is defined as the ratio between the amplitude  $A_f$  of the fundamental harmonic located at frequency f and the sum of the other amplitude components where are combined noise and distortion:

$$SINAD = 20log \sqrt{\frac{A_f^2}{\sum_{k=1}^{f-1} A_k^2 + \sum_{k=f+1}^{\frac{N}{2}} A_k^2}}$$

(2.10)

The reader should notice that the k index of the leftmost sum at denominator starts from one. This is due to the current dynamic analysis of ADC performance accomplished using a sinusoidal signal, where the DC component located at k = 0 is not conveyed [41] [42]. Substituting now Eq 2.10 in Eq 2.9 the Effective Number of Bits (ENOB) can be obtained:

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

(2.11)

which is the actual resolution of the ADC *Methods and draft standards for the DY-Namic characterization and testing of Analog to Digital converters* (DYNAD) [43]. In addition to the SINAD and the ENOB, the spurious free dynamic range (SFDR) must also be considered. In a power plot, this quantity is simply the range free of spurious components assuming as reference the principal component frequency centered at 0 dB.

#### 2.2 Thermal noise

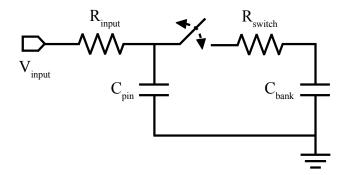

Figure 2.2: RC model of an ADC switch.

Another source of noise is introduced by the sampling process itself and it can be analyzed considering the switching model of an ADC [44] reported in Figure 2.2. Here  $R_{input}$ models the external source resistance,  $R_{switch}$  represents the internal switch resistance (usually around 1 k $\Omega$ ),  $C_{pin}$ quantifies the pin capacitance and  $C_{bank}$  is the sum of the capacitive ar-

ray of a Successive Approximation Register (SAR) architecture explained in Section 2.4.4. If  $R_{input} \ll R_{switch}$  and the errors generated by the capacitance  $C_{pin}$ negligible, the model works as an RC filter. Let's introduce the thermal noise  $V_{th}$ [45] given by:

$$V_{th} = \sqrt{4k_B T R \Delta f} \tag{2.12}$$

where  $k_B$  is the Boltzmann constant  $(1.38 \cdot 10^{-23} \text{ J/K})$ , T indicates the absolute temperature in Kelvin, R is the resistive contribution measured in  $\Omega$  of the complex impedance Z and  $\Delta f$  defines the bandwidth expressed in Hz. The thermal noise, also called Johnson noise, is due to the thermal agitation of electrons in ohmic paths. Taking into account a frequency band from  $f_1$  to  $f_2$  and the impedance Z, Eq 2.12 can be rewritten as:

$$V_{th} = \sqrt{4k_B T \int_{f_1}^{f_2} Re(Z) \, df} \tag{2.13}$$

#### 2.2. THERMAL NOISE

where Re(Z) is the real part of impedance Z:

$$Re(Z) = \frac{R}{1 + (2\pi f R C)^2}$$

(2.14)

The total noise voltage of a RC pair can be obtained replacing Eq 2.14 into Eq 2.13 and extending the interval of integration from 0 to  $+\infty$ :

$$V_{th} = \sqrt{4k_B T \int_0^{+\infty} \frac{R}{1 + (2\pi f R C)^2} df}$$

(2.15)

Let's focus now on the improper integral. Because of its definition, we can rewrite it as:

$$\int_{0}^{+\infty} \frac{R}{1 + (2\pi f R C)^2} df = \lim_{i \to \infty} \int_{0}^{i} \frac{R}{1 + (2\pi f R C)^2} df \qquad (2.16)$$

We define the new variable x and its differential dx as:

$$x = 2\pi f RC$$

$$dx = 2\pi RC df$$

$$(2.17)$$

$$df = \frac{dx}{2\pi RC}$$

where in the last line the expression for df is shown. Substituting it into Eq 2.16, the improper integral becomes:

$$\lim_{i \to \infty} \frac{1}{2\pi C} \int_0^i \frac{1}{1+x^2} dx =$$

$$= \frac{1}{2\pi C} \lim_{i \to \infty} \arctan x \Big|_0^i = \frac{1}{4C}$$

(2.18)

The result is achieved using a well-know remarkable integral and the limit value of  $\arctan x$  function for  $x \to \infty$  which is equal to  $\pi/2$ . Thus, a last substitution leads to:

$$V_{th} = \sqrt{4k_B T \int_0^{+\infty} \frac{R}{1 + (2\pi f R C)^2} df} = \sqrt{\frac{k_B T}{C}}$$

(2.19)

That is the expression for the thermal noise. In the case of a SAR ADC, the same result can be reached balancing the energy stored in the capacitor array with the quantity derived by the equipartition energy theorem considering one thermody-namic degree of freedom:

$$\frac{1}{2}C\overline{V}^2 = \frac{1}{2}k_BT\tag{2.20}$$

Eq 2.19 tell us that the thermal noise dominates the ADC noise contribution for high-resolution ADCs [41] [46].

#### 2.3 Jitter

The jitter is the last source of uncertainty taken into account to model the noise at this stage. In order to quantify the effect of jitter, the following input signal is considered:

$$V_{in} = V_0 \sin(2\pi f_{in} t)$$

(2.21)

where an ADC with a full scale range of  $V_{REF}$  and  $V_0 = V_{REF}/2$  is assumed. The point of maximum slope can be easily obtained as:

$$\left. \frac{dV}{dt} \right|_{max} = 2\pi f_{in} V_0 \cos(2\pi f_{in} t) \right|_{max} = 2\pi f_{in} V_0 \tag{2.22}$$

At this point, the RMS uncertainty  $V_j$  on the sampled value is caused by the RMS jitter  $\sigma_t$ :

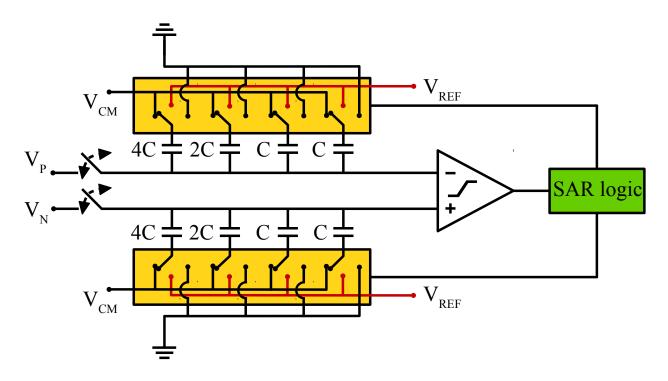

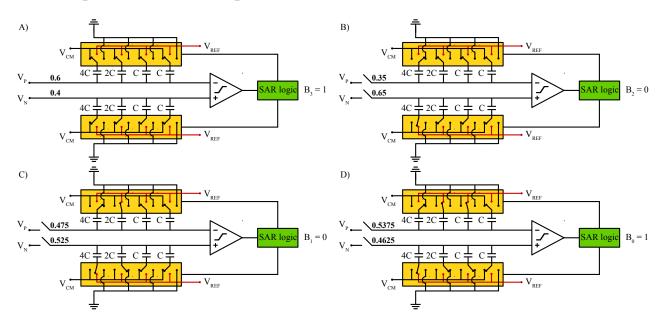

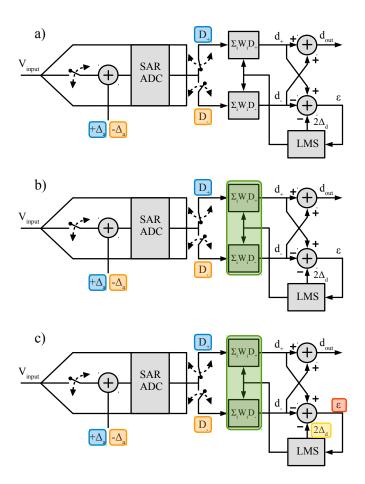

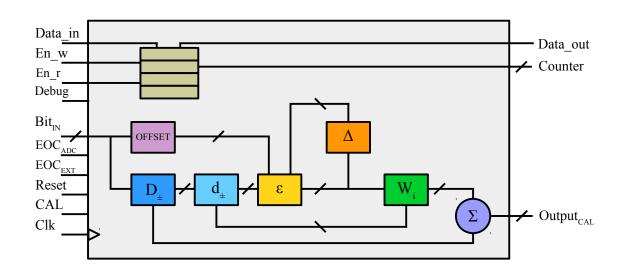

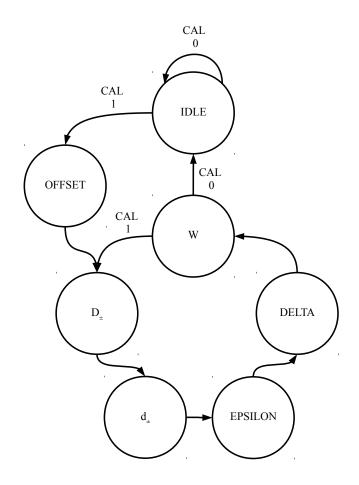

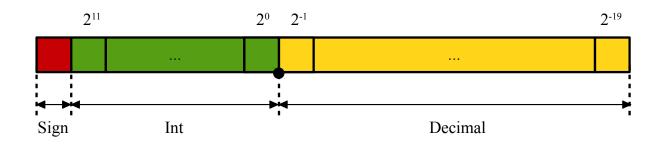

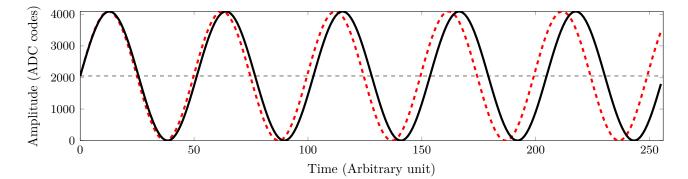

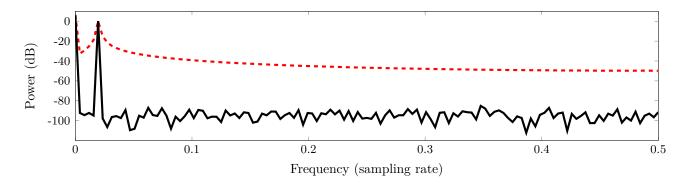

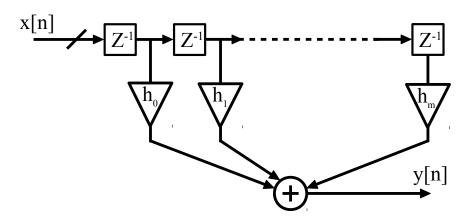

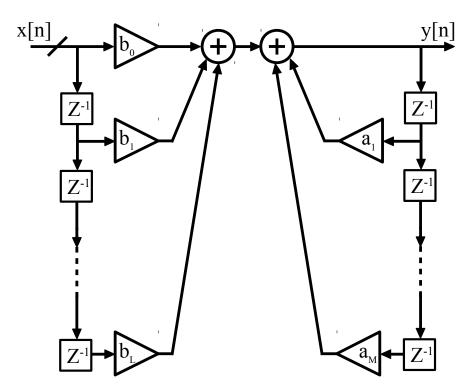

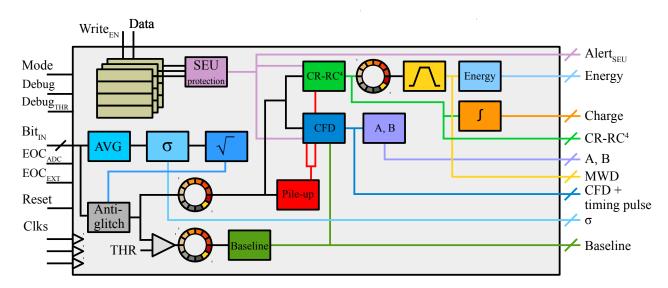

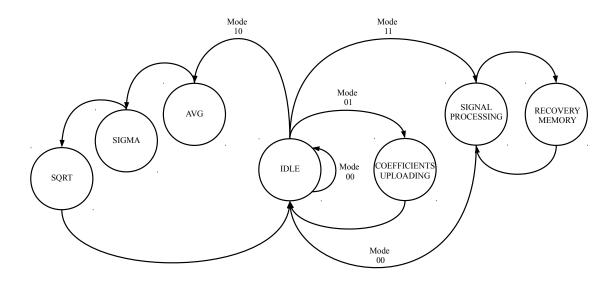

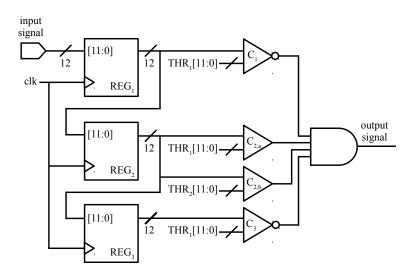

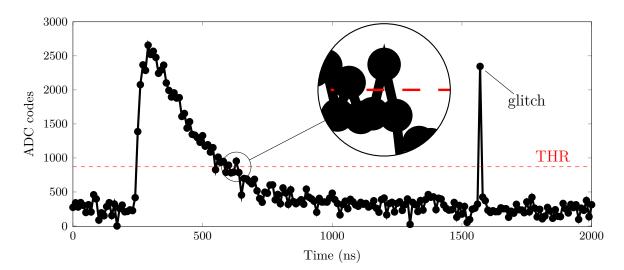

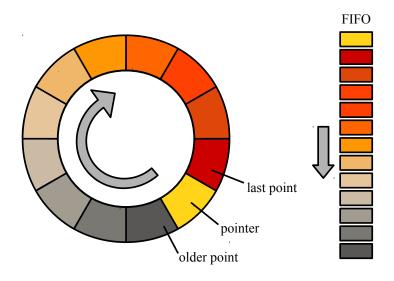

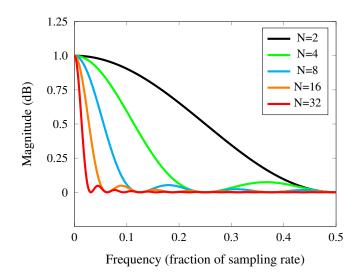

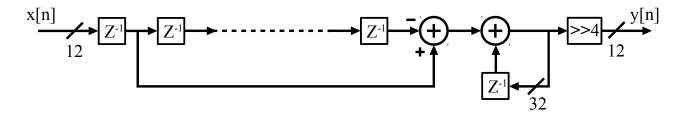

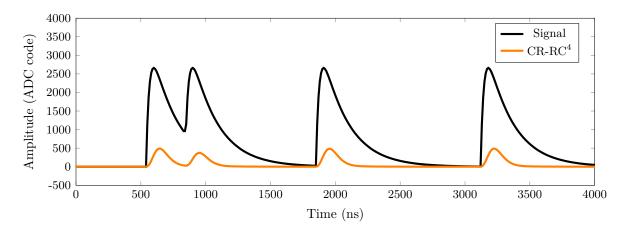

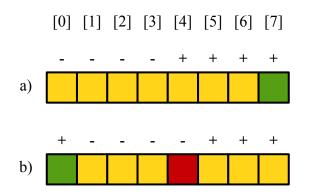

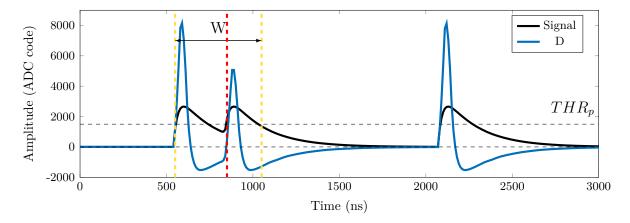

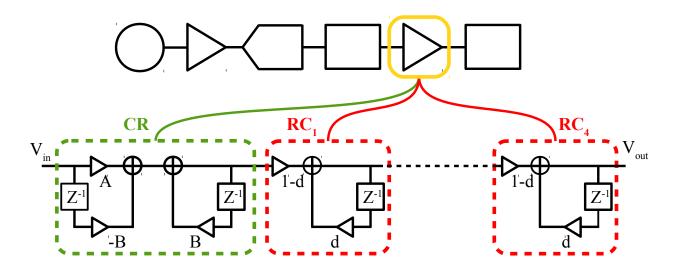

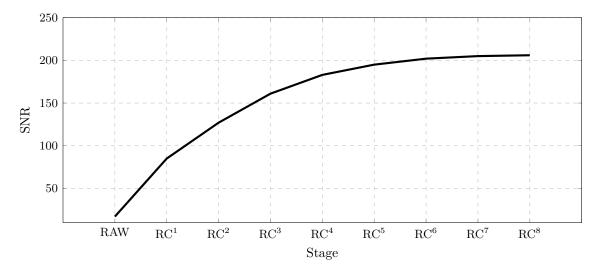

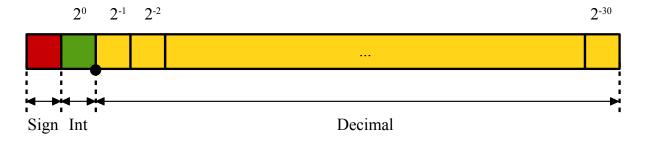

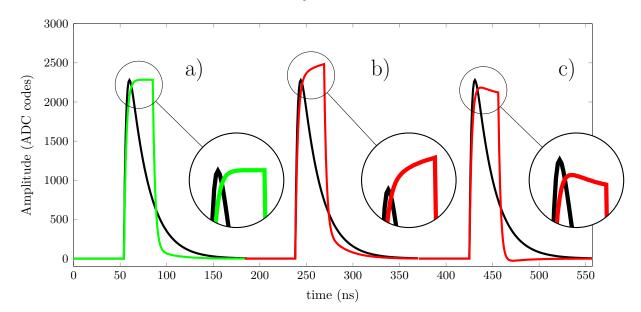

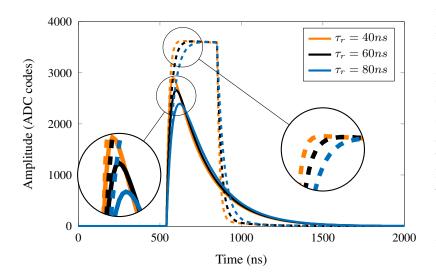

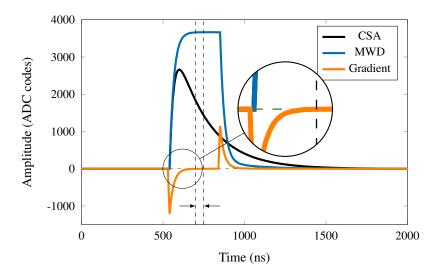

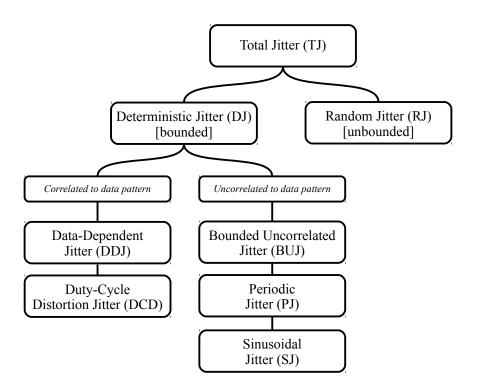

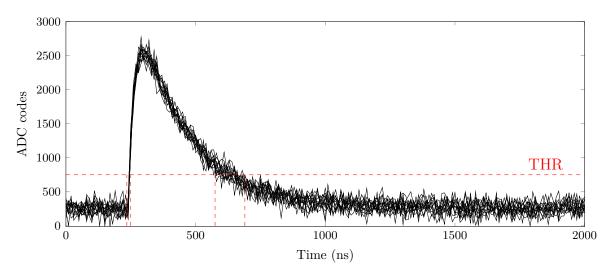

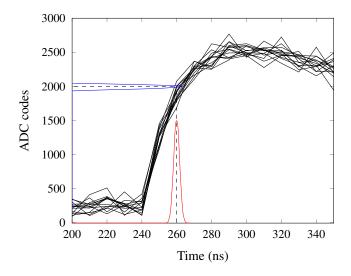

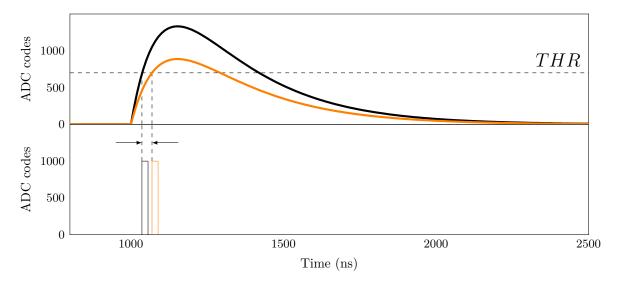

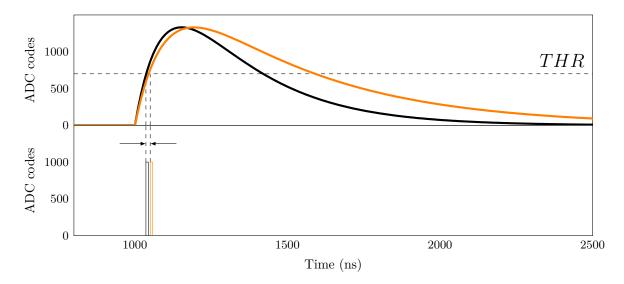

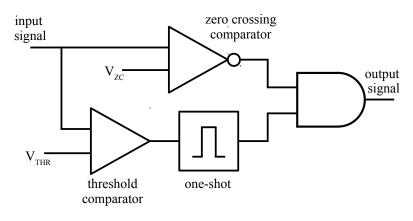

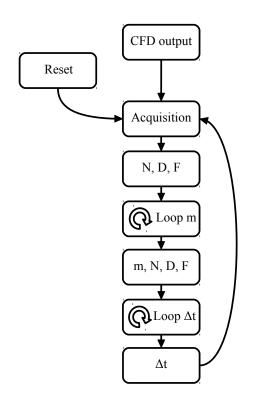

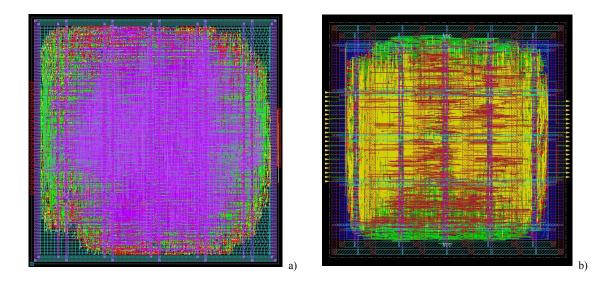

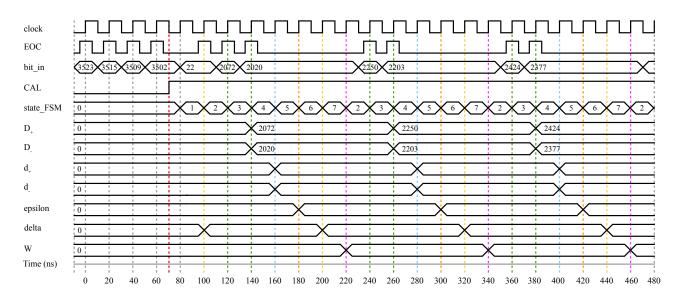

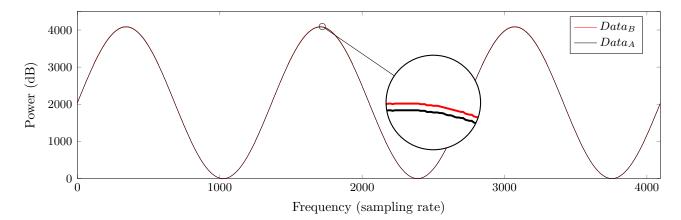

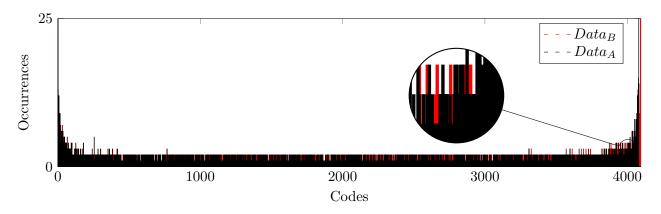

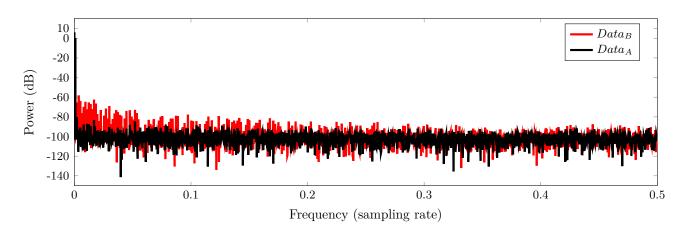

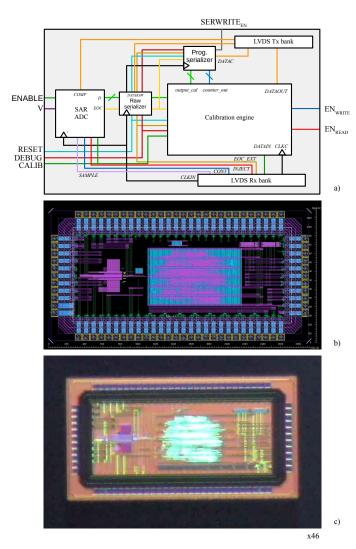

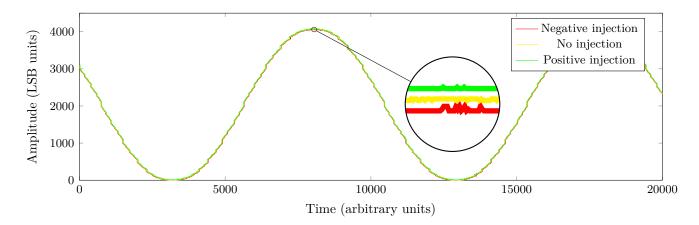

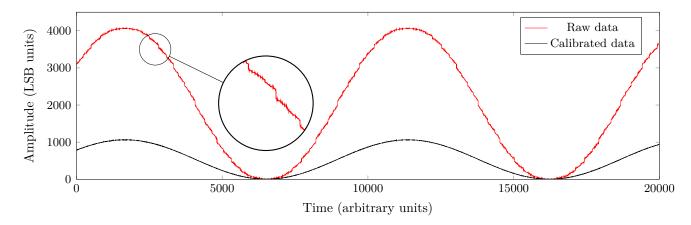

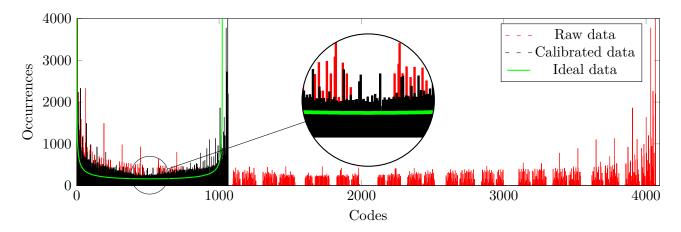

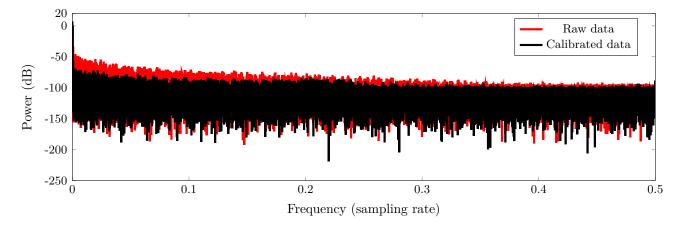

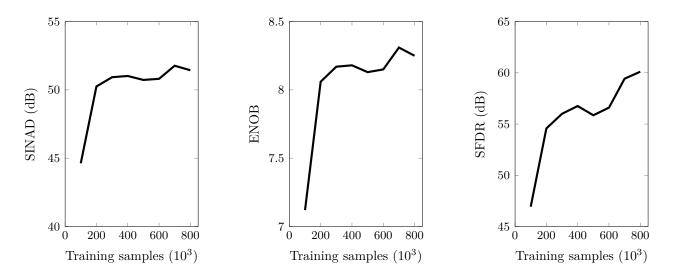

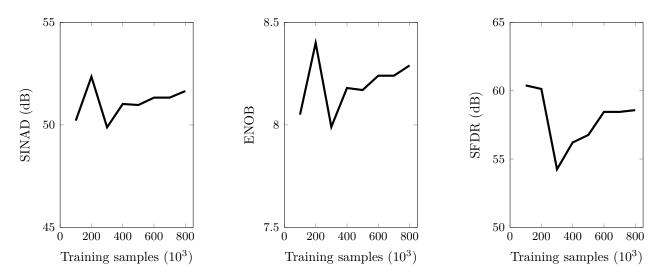

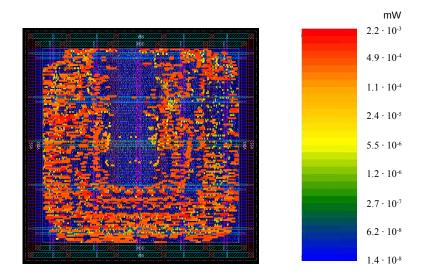

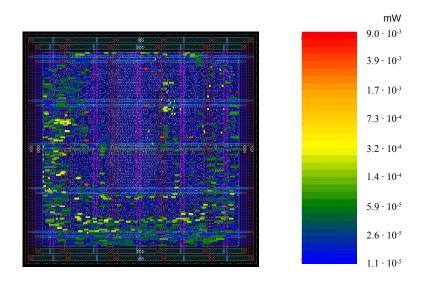

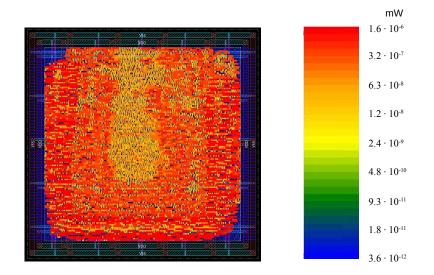

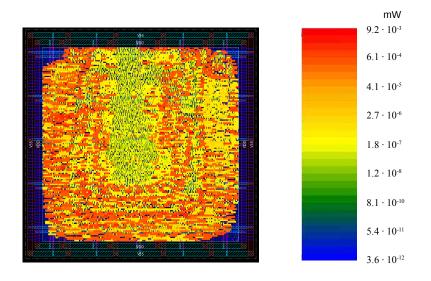

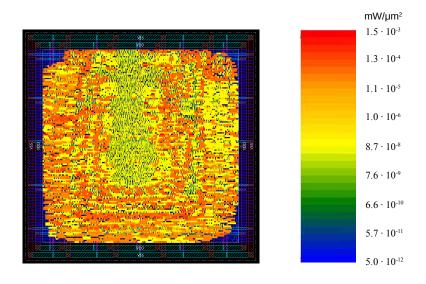

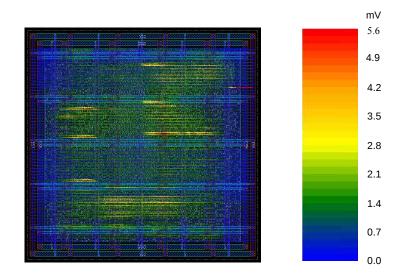

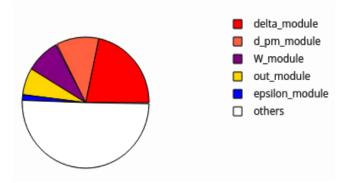

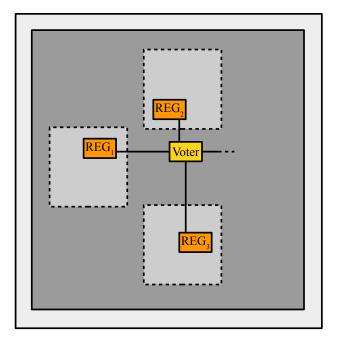

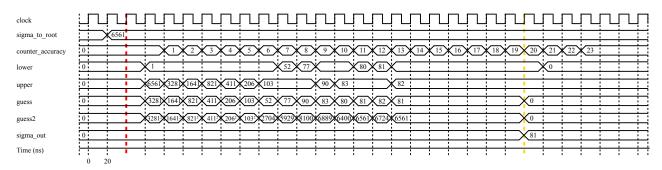

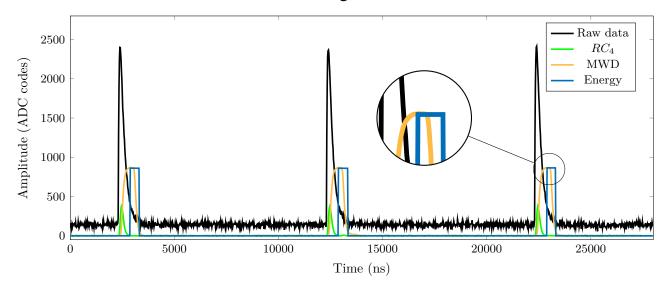

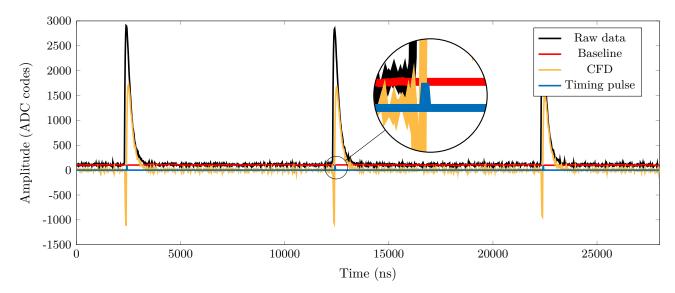

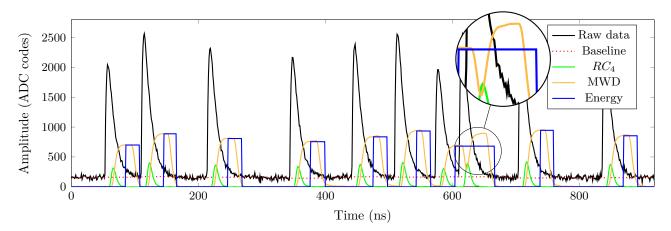

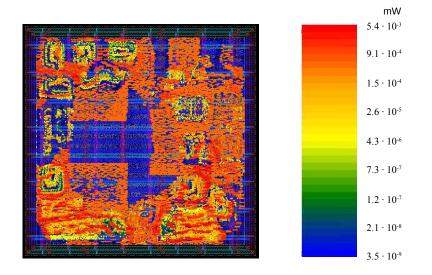

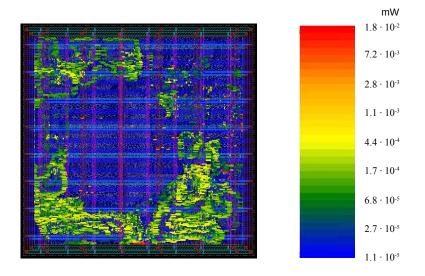

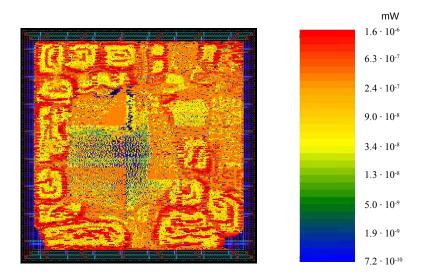

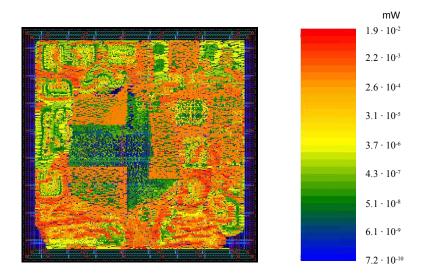

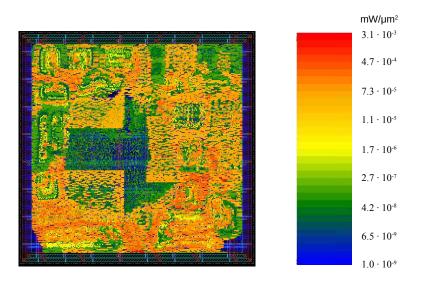

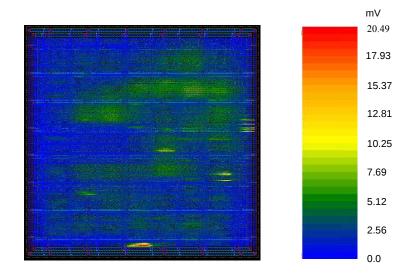

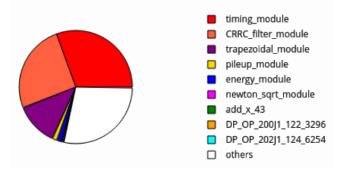

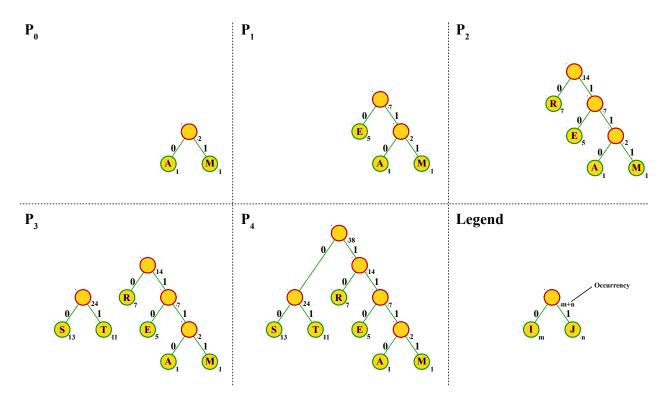

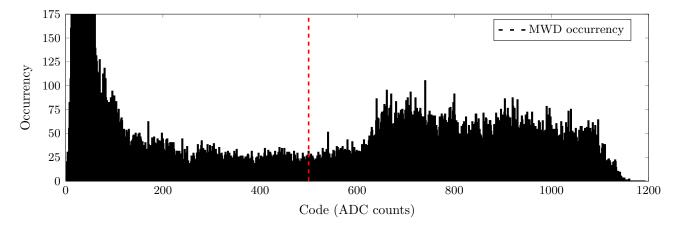

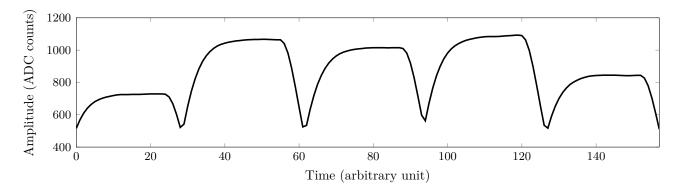

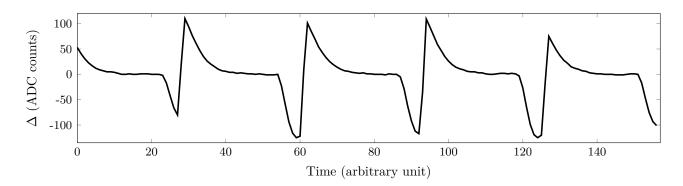

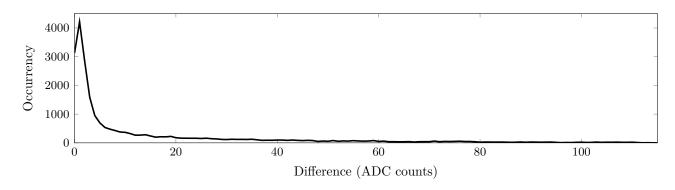

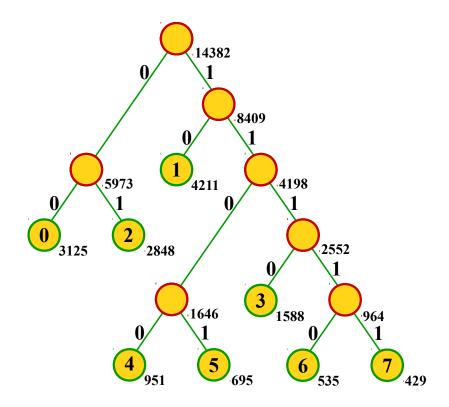

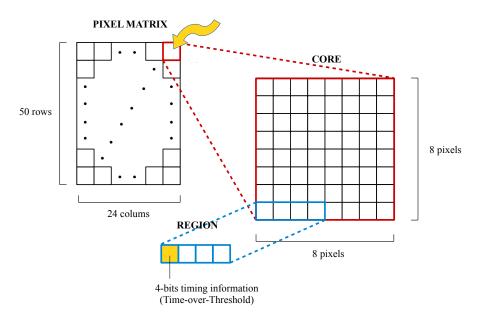

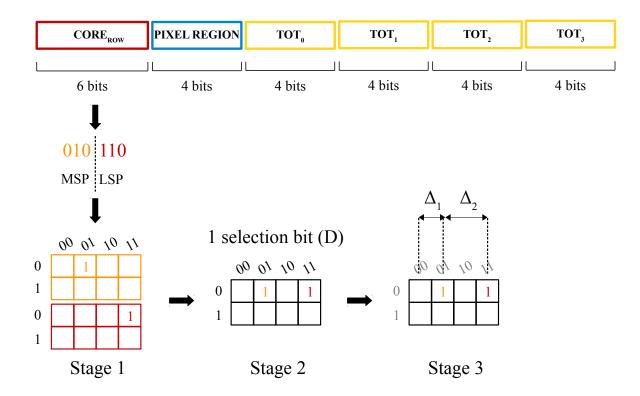

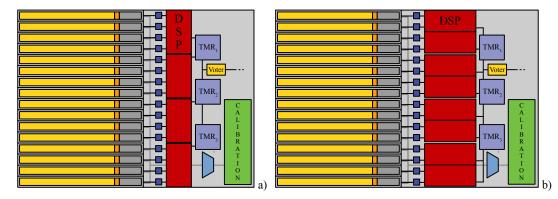

$$V_j = \pi f_{in} V_{REF} \sigma_t \tag{2.23}$$