####

## Self-Test Mechanisms for Automotive Multi-Processor System-on-Chips

## Andrea Floridia

\* \* \* \* \* \*

#### Supervisor

Prof. Ernesto Sanchez, Supervisor

#### **Doctoral Examination Committee:**

Prof. Alberto Bosio, Referee, Ecole Centrale Lyon

Prof. Giorgio di Natale, Referee, TIMA Laboratories

Prof. Liviu Miclea, University of Cluj-Napoca

Prof. Haralampos Stratigopoulos, Sorbonne Universitè

Prof. Matteo Sonza Reorda, Politecnico di Torino

Politecnico di Torino 23 September 2021

| NoDerivative Works 4.0 International | tive Commons License, Attribution - Noncommercial: see www.creativecommons.org. The text al purposes, provided that credit is given to |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ·                                    | d organisation of this dissertation constitute compromise in any way the rights of third e security of personal data.                  |

|                                      | Andrea Floridia<br>Turin, 23 September 2021                                                                                            |

|                                      |                                                                                                                                        |

## Acknowledgements

This work would not be possible without the support of many people. Foremost among them are, Ernesto Sanchez and Matteo Sonza Reorda, whom I thank for their encouragement and the opportunities they gave me.

To Aleksa and Esteban, just thank you (you know what I am referring to!).

To all the people in Lab3 and friends met in Turin in these five years, they have been a source of sanity in an endeavor that has occasionally been far from being sane.

To Roberta, that remembers me everyday how lucky I am.

Last but not least, my whole family, who have been enormously supportive even at 1500 kilometers away and always believed in me, even when no one else did.

## Summary

While the technology for enabling fully autonomous self-driving cars is still ahead, today automobiles massively rely on electronics for a variety of functionalities. As these functionalities require more and more computational power, the embedded systems introduced in the automobiles had to evolve accordingly. As of today, Multi-processor System-on-Chips (MPSoCs) are commonly found for these applications. Such SoCs embeds two or more processor cores within the same silicon die, in conjunction with different peripherals and levels of memories (both static and non-volatile). It is known that due to the harsh environment in which they are deployed, physical malfunctions due hardware faults can manifest. Periodic in-field self-testing represents a common countermeasure against these threats. These mechanisms can be implemented both in hardware and software but, most of them were originally devised for simpler single-processor SoCs. While in recent years there has been a considerable effort in improving the hardware-based selftest mechanisms, the same is not true for the software-based ones. Software-based approaches mainly consist in the application of software self-test routines (or procedures) of a Software Test Library (STL). Over the years they have been shown to be valuable especially for the processor core, being the most critical portion of the system.

Therefore, the first contribution of this thesis was to study the applicability of STLs in a multi-processor context. Rather than the development of new Software-Based Self-test (SBST) methods, the main focus was the parallel execution of already developed STLs. This originates from the fact that automotive MPSoCs reuse the same IP processor cores that have been used (and extensively verified) for single-processor devices. In MPSoCs, it has been widely reported that the major hurdle of embedded software is its predictability in terms of execution time. In fact, when all the processor cores are active at the same time, the system bus activity considerably increases with respect to a single-core system. This higher activity (which induces the processor pipeline to stall) impacts the performances of each processor, since the accesses to the memory sub-system are delayed. As the STL is in practice a piece of embedded software, it is exposed to the same issues.

The most significant achievement under this perspective consisted in the development of a software scheduler. Such a scheduler differs from any other software scheduler for embedded systems, since it is tailored for the needs of STLs in an automotive MPSoC. Through extensive experiments, it was proven to be a valid solution to fit the narrow test windows of industrial automotive MPSoCs (maximizing the overall system availability). At the same time, the proposed scheduler demonstrated a good execution time predictability. This is remarkable, since it was already mentioned that the embedded software execution time is hard to be predicted accurately.

Furthermore, the research developed in this thesis demonstrates for the first time through real industrial case study that this unpredictability is particular harmful for self-test procedures. Indeed, it was observed that such unpredictability not only alters self-test procedure execution time (when executed in parallel). Additionally, some self-test procedures intermittently fail when in field and/or produce a fluctuating fault coverage. For both cases, it was proposed a mitigation technique based on the usage of the inner most level of private cache memories. When the self-test procedures are executed from such private memories, with precautions, it is possible to isolate the self-test procedure execution form the rest of the system (thus achieving the required stability).

When dealing with self-test mechanisms, it exists a further category of mechanisms which are said to be hybrid. They indeed consist of both hardware and software cooperating together for implementing an efficient self-test. This thesis contributes to this new emerging self-test approach with a novel hybrid technique for checking the integrity of the comparators used in the lockstep configuration (commonly found in automotive MPSoCs).

The third contribution of this thesis consists of optimizing the fault grading methodologies to meet the necessities of the functional fault simulation. Functional fault simulation is an emerging approach for performing fault simulation in safety-critical applications when a processor executing software is involved. Recently, the Electronic Design Automation (EDA) companies are providing tools able to support these methodologies. However, different aspects must be taken into account, not previously considered with the traditional fault simulation approaches. It is worth noting that the applicability of these researches is not limited to processors of an automotive MPSoCs. One of the main applications of functional fault grading addressed in this thesis is in the STL development. The main bottleneck of the STL development remains the fault simulation. Therefore, part of the research efforts were directed towards the formulation of functional fault grading methodologies intended for STLs. The key concept behind these methodologies is the fault dropping which allows to considerably reduce the effort for the fault simulation.

The fourth contribution still concerns the functional fault grading, but in a rather different scenario. Due to the ever-increasing complexity of the newer devices, designers are shifting to emulation of the ASICs in order to speed up the verification process. The same emulators can be used as well for quickly evaluating the effectiveness of self-test mechanisms or general dependability analyses that

require functional fault grading. This can be achieved by instrumenting the original netlist, in order to enable the injection of different faults (most often either Single-Event Transient or stuck-at). In this context, this thesis introduces a fault emulation platform to support dependability analyses of safety-critical Application-Specific Integrated Circuits (ASICs). Differently than existing works, the focus was the fault detection mechanism that allows to mimic the detection mechanisms of a fault simulator (including fault dropping introduced above). The proposed platform can be integrated in the already-existing IEEE 1149.1 JTAG infrastructure of the target ASIC. Therefore, it can be easily accessed with standard tools and perfectly compatible with the modern industrial emulators based on Field-Programmable Gate Arrays (FPGAs).

This thesis is organized as follow: Chapter 1 is devoted to the introduction. The motivations leading to this thesis are discussed in great detail. Moreover, the basic terminology used throughout the manuscript is provided. Then, the thesis is divided into two main parts. The first one addresses the description of the self-test mechanisms for automotive MPSoCs (Chapter 2, 3, 4).

The second part instead, focuses on the improvements in the functional fault grading methodologies (Chapter 5, 6). In Chapter 7 concludes the thesis. In that chapter, both the major achievements and future research directions are analyzed.

## Contents

| Li | st of         | Table           | $\mathbf{s}$                                               | X   |

|----|---------------|-----------------|------------------------------------------------------------|-----|

| Li | st of         | Figur           | es                                                         | XII |

| 1  | Intr          | oduct           | ion                                                        | 1   |

| Ι  | Or            | n-line          | self-test mechanisms for automotive MPSoCs                 | 9   |

| 2  | Det           | ermin           | istic in-field parallel execution of self-test programs in | 1   |

|    | $\mathbf{MP}$ | $\mathbf{SoCs}$ |                                                            | 11  |

|    | 2.1           | Backg           | ground                                                     | 12  |

|    |               | 2.1.1           | Problem statement                                          | 12  |

|    |               | 2.1.2           | Related works                                              | 14  |

|    | 2.2           | The c           | ache-based execution approach                              | 15  |

|    | 2.3           | Exper           | rimental results                                           | 17  |

|    |               | 2.3.1           | Case study and experimental setup                          | 17  |

|    |               | 2.3.2           | Variability in MPSoCs                                      | 19  |

|    |               | 2.3.3           | Uncertain fault coverage                                   | 20  |

|    |               | 2.3.4           | Unstable signature                                         | 21  |

|    |               | 2.3.5           | Comparison with a TCM-based approach                       | 22  |

| 3  | Dec           | entral          | ized Schedulers for STLs in automotive MPSoCs              | 25  |

|    | 3.1           | Backg           | ground                                                     | 25  |

|    |               | 3.1.1           | Problem statement                                          | 25  |

|    |               | 3.1.2           | Related works                                              | 27  |

|    | 3.2           | The b           | oot-time tests schedulers                                  | 28  |

|    |               | 3.2.1           | Terminology and definitions                                | 29  |

|    |               | 3.2.2           | The common decentralized architecture                      | 30  |

|    |               | 3.2.3           | Multi-resource heterogeneous scheduler                     | 30  |

|    |               | 3.2.4           | Single-resource heterogeneous scheduler                    | 35  |

|    |               | 3.2.5           | Multi/Single-resource homogeneous scheduler                | 35  |

|    |               | 3.2.6           | Summary                                                    | 36  |

|          | 3.3               | Exper          | imental results                                                 | 37         |

|----------|-------------------|----------------|-----------------------------------------------------------------|------------|

|          |                   | 3.3.1          | Case study and experimental setup                               | 38         |

|          |                   | 3.3.2          | Single-resource homogeneous multi-core scheduler: serial schedu | 1-         |

|          |                   |                | ing                                                             | 40         |

|          |                   | 3.3.3          | Single-resource homogeneous multi-core scheduler: non-selfish   |            |

|          |                   |                | decentralized schedulers                                        | 40         |

|          |                   | 3.3.4          | Single-resource homogeneous multi-core scheduler: the De-       |            |

|          |                   |                | centralized Selfish Scheduler                                   | 43         |

|          |                   | 3.3.5          | Single-resource multi-core heterogeneous scheduler: the serial  |            |

|          |                   |                | scheduler                                                       | 47         |

|          |                   | 3.3.6          | Single-resource multi-core heterogeneous scheduler: the De-     |            |

|          |                   |                | centralized Selfish Scheduler                                   | 48         |

|          |                   | 3.3.7          | Multi-resource multi-core scheduler                             | 51         |

|          |                   | 3.3.8          | Final Considerations                                            | 53         |

| 4        | TT1               |                | . It is a self-to-st and a long-to-st first constant of a DCIC  |            |

| 4        | •                 |                | n-line self-test mechanism for comparators of a DCLS            |            |

|          | <b>pro</b><br>4.1 | Cessor         | mound                                                           | 55         |

|          | 4.1               | баске<br>4.1.1 | round                                                           | 55<br>55   |

|          |                   | 4.1.1          | Limitations of hardware and software self-test mechanisms       | 57<br>57   |

|          |                   | 4.1.2          | Related works                                                   | 58         |

|          | 4.2               | _              | sed hybrid self-test mechanism                                  | 59         |

|          | 4.2               | 4.2.1          | The overall architecture                                        | 59         |

|          |                   | 4.2.2          | The on-line self-test flow                                      | 62         |

|          |                   | 4.2.2          | Faults detection mechanism                                      | 65         |

|          | 4.3               |                | imental results                                                 | 65         |

|          | 1.0               | 4.3.1          | Case study                                                      | 66         |

|          |                   | 4.3.2          | Evaluation of software self-test mechanisms                     | 66         |

|          |                   | 4.3.3          | Evaluation of hardware self-test mechanisms                     | 67         |

|          |                   | 4.3.4          | Evaluation of the hybrid self-test mechanism                    | 68         |

|          |                   | 4.3.5          | Failure Mode Effect and Diagnostic Analysis results             | 70         |

|          |                   |                | Comparison of the hardware, software and hybrid self-test       |            |

|          |                   |                | mechanisms                                                      | 72         |

|          |                   |                |                                                                 |            |

|          |                   |                |                                                                 |            |

| II<br>gi | l li<br>les       | mprov          | vements of functional fault grading methodolo-                  | <b>7</b> 5 |

| 5        | Imr               | oroved         | fault grading techniques for STLs                               | 77         |

|          | 5.1               |                | round                                                           | 77         |

|          |                   | 5.1.1          |                                                                 | 77         |

|          |                   | 5.1.2          | Sequential circuit fault simulation (SC-FSIM)                   |            |

|   |                                                               | 5.1.3                                                                                   | Self-test procedures fault simulation (STP-FSIM)                                                                                                                                                          | 79                                             |

|---|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|   | 5.2                                                           | Basic                                                                                   | fault grading techniques                                                                                                                                                                                  | 81                                             |

|   |                                                               | 5.2.1                                                                                   | Fault grading of a single self-test procedure                                                                                                                                                             | 82                                             |

|   |                                                               | 5.2.2                                                                                   | Fault grading of a Software Test Library                                                                                                                                                                  | 83                                             |

|   | 5.3                                                           | Optim                                                                                   | nized fault grading techniques                                                                                                                                                                            | 84                                             |

|   |                                                               | 5.3.1                                                                                   | STP-FSIM3                                                                                                                                                                                                 | 84                                             |

|   |                                                               | 5.3.2                                                                                   | STP-FSIM4                                                                                                                                                                                                 | 85                                             |

|   |                                                               | 5.3.3                                                                                   | Summary of the different techniques                                                                                                                                                                       | 86                                             |

|   | 5.4                                                           | Case s                                                                                  | study and experimental results                                                                                                                                                                            | 86                                             |

|   |                                                               | 5.4.1                                                                                   | Experimental setup and case study                                                                                                                                                                         | 87                                             |

|   |                                                               | 5.4.2                                                                                   | STP-FSIM methods                                                                                                                                                                                          | 89                                             |

|   |                                                               | 5.4.3                                                                                   | Fault grading for DCLS-oriented STLs                                                                                                                                                                      | 92                                             |

| 6 | TOD A                                                         | C bos                                                                                   | and fault amplication platform for processor based ACICs                                                                                                                                                  | 95                                             |

| U | $\mathbf{J}\mathbf{L}P$                                       | iG-pas                                                                                  | ed fault emulation platform for processor-based ASICs                                                                                                                                                     | 90                                             |

| U | $\begin{array}{c} \mathbf{J} \mathbf{I} P \\ 6.1 \end{array}$ |                                                                                         | round                                                                                                                                                                                                     | 96                                             |

| U |                                                               |                                                                                         |                                                                                                                                                                                                           |                                                |

| U |                                                               | Backg                                                                                   | round                                                                                                                                                                                                     | 96                                             |

| U |                                                               | Backg<br>6.1.1                                                                          | round                                                                                                                                                                                                     | 96<br>96                                       |

| U |                                                               | Backg<br>6.1.1<br>6.1.2                                                                 | round                                                                                                                                                                                                     | 96<br>96<br>96                                 |

| U |                                                               | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                               | round                                                                                                                                                                                                     | 96<br>96<br>96<br>98                           |

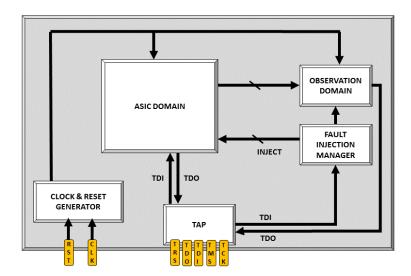

| U | 6.1                                                           | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                               | round                                                                                                                                                                                                     | 96<br>96<br>96<br>98<br>98                     |

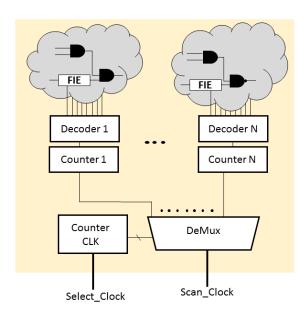

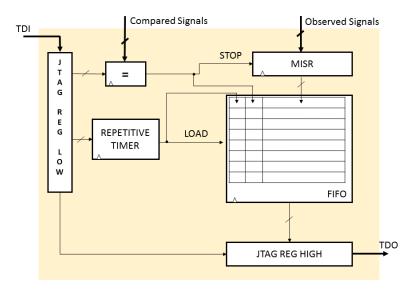

| U | 6.1                                                           | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>The fa                                     | round Introduction Related works and motivations The fault injection mechanism Terminology ult emulation platform The global architecture                                                                 | 96<br>96<br>96<br>98<br>98<br>99               |

| U | 6.1                                                           | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>The fa<br>6.2.1                            | round Introduction Related works and motivations The fault injection mechanism Terminology ult emulation platform The global architecture The observation domain                                          | 96<br>96<br>96<br>98<br>98<br>99               |

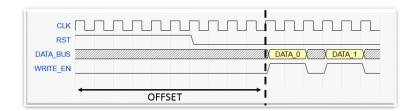

| U | 6.1                                                           | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>The fa<br>6.2.1<br>6.2.2<br>6.2.3          | round Introduction Related works and motivations The fault injection mechanism Terminology ult emulation platform The global architecture The observation domain The fault emulation flow                 | 96<br>96<br>98<br>98<br>98<br>99<br>99         |

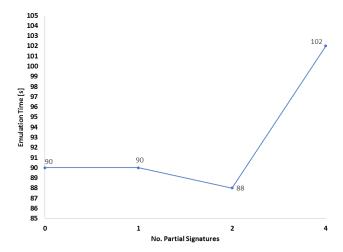

| 7 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                 | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>The fa<br>6.2.1<br>6.2.2<br>6.2.3<br>Exper | round Introduction Related works and motivations The fault injection mechanism Terminology ult emulation platform The global architecture The observation domain The fault emulation flow imental results | 96<br>96<br>98<br>98<br>99<br>99<br>100<br>101 |

## List of Tables

| 1.1 | SPFM and LFM Requirements for Safety-relevant Modules                | 2  |

|-----|----------------------------------------------------------------------|----|

| 2.1 | Parallel STLs Execution - Stalls (in Clock Cycles, CC) due to the    |    |

|     | Memory Subsystem                                                     | 20 |

| 2.2 | Forwarding Logic Fault Simulation Results                            | 21 |

| 2.3 | ICU and HDCU Fault Simulation Results                                | 22 |

| 2.4 | TCM-based versus Cache-based approaches for Imprecise Interrupts     | 22 |

| 3.1 | Single-core characteristics of the three STLs for the designs D1 and |    |

|     | D2                                                                   | 39 |

| 3.2 | Performances of the serial scheduler @16MHz for D2                   | 40 |

| 3.3 | Performances of different decentralized schedulers @16MHz for D2 .   | 40 |

| 3.4 | Performance counters values for the triple-core scenario for D2      | 41 |

| 3.5 | Performances of the Decentralized Selfish Scheduler @16MHz for D2    | 44 |

| 3.6 | Overhead of the Decentralized Selfish Scheduler for D2               | 44 |

| 3.7 | The single-resource serial scheduler @16MHz for D1                   | 48 |

| 3.8 | Multi-resource scheduler overhead for D1 and D2                      | 51 |

| 4.1 | Test algorithm for a 4-bit wide comparator                           | 58 |

| 4.2 | Characteristics of applications programs                             | 67 |

| 4.3 | STL characteristics                                                  | 67 |

| 4.4 | Hardware Self-Test [1] Synthesis: Area Breakdown                     | 68 |

| 4.5 | LSMU Synthesis: Area Breakdown                                       | 68 |

| 4.6 | Characteristics of the self-test programs exploiting the LSMU        | 69 |

| 4.7 | FMEDA LSMU: Failure Modes and Countermeasures                        | 72 |

| 4.8 | Area, fault coverage and test duration for the three approaches con- |    |

|     | sidered                                                              | 73 |

| 5.1 | Fault simulation techniques comparison                               | 86 |

| 5.2 | STL characteristics                                                  | 88 |

| 5.3 |                                                                      | 88 |

| 5.4 | Size of faults sets                                                  | 90 |

| 5.5 |                                                                      | 92 |

| 5.6 | $\circ$                                                              | 92 |

| 5.7 | STP-FSIM0 for DCLS-oriented STL grading                              | 93 |

| 6.1 | FPGA implementation details                                          | 04 |

## List of Figures

| 2.1 | (a) Single-core execution of the program. (b) Multi-core execution of the program. In red the different paths activated by the same |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

|     | program                                                                                                                             | 13 |

| 2.2 | The proposed Cache-based strategy. On the left-hand side the single-                                                                |    |

|     | core version. On the right-hand side the modified multi-core test pro-                                                              |    |

|     | gram version. In case of no-write allocate caches, the Test Program                                                                 |    |

|     | Body might be lightly modified.                                                                                                     | 16 |

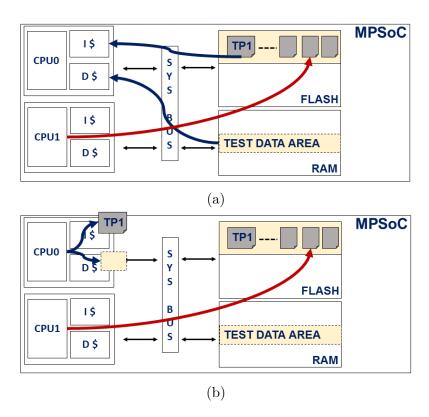

| 2.3 | Example of the proposed cache-based execution. In an MPSoC two                                                                      |    |

|     | CPUs (labeled with 0 and 1) execute in parallel an STL. CPU0 exe-                                                                   |    |

|     | cutes a test program TP1 that uses the cache-based execution, while                                                                 |    |

|     | CPU1 executes another portion of the STL. In (a) is represented                                                                     |    |

|     | the loading loop. In (b) the execution loop. It is worth mention-                                                                   |    |

|     | ing that normally in STLs the TEST DATA AREA is protected by                                                                        |    |

|     | access mechanisms. These are required for sake of determinism, for                                                                  |    |

|     | avoiding one core interfering with the execution of another                                                                         | 18 |

| 3.1 | Serial versus parallel execution of an STL in a multi-core scenario                                                                 | 26 |

| 3.2 | Temporal evolution of the execution of the two heterogeneous sched-                                                                 |    |

|     | ulers across the processor cores. The test programs in light gray                                                                   |    |

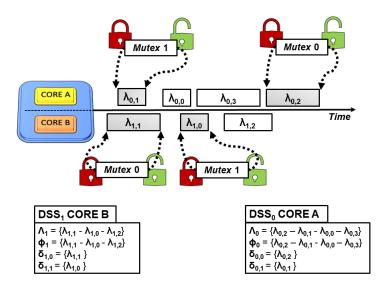

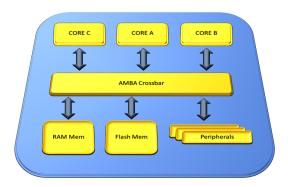

|     | indicates those accessing a shared resource                                                                                         | 36 |

| 3.3 | Internal architecture of the considered multi-core System-on-Chips.                                                                 | 39 |

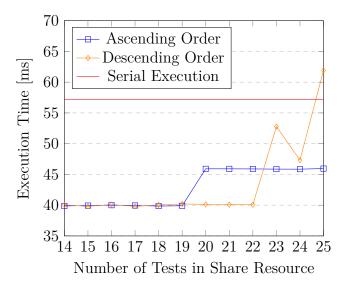

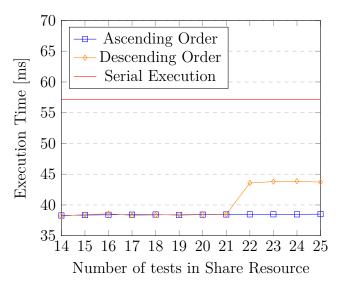

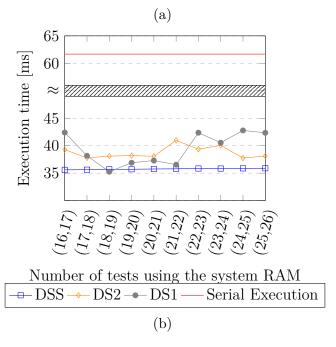

| 3.4 | For design D2, the DS3 execution time (y-axis) at 16MHz when                                                                        |    |

|     | increasing the number (x-axis) of self-test procedures in the Share                                                                 |    |

|     | Resource set in a dual-core scenario                                                                                                | 42 |

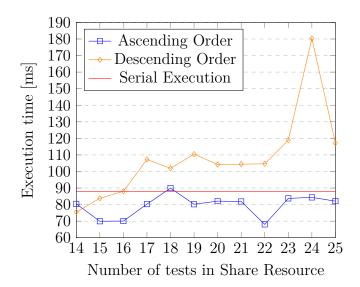

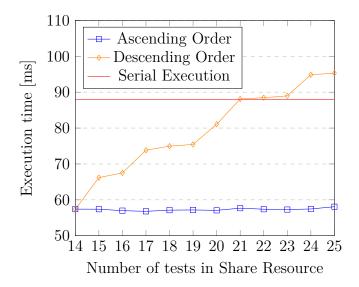

| 3.5 | For design D2, the DS3 execution time (y-axis) at 16MHz when                                                                        |    |

|     | increasing the number (x-axis) of self-test procedures in the Share                                                                 |    |

|     | Resource set in a triple-core scenario                                                                                              | 43 |

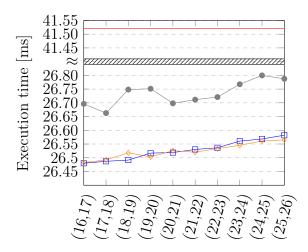

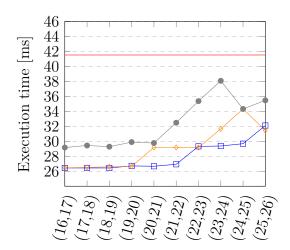

| 3.6 | For design D2, the proposed DSS execution time (y-axis) at 16MHz                                                                    |    |

|     | when increasing the number (x-axis) of self-test procedures in the                                                                  |    |

|     | Share Resource set in a dual-core scenario                                                                                          | 45 |

| 3.7 | For design D2, the proposed DSS execution time (y-axis) at 16MHz                                                                    |    |

|     | when increasing the number (x-axis) of self-test procedures in the                                                                  |    |

|     | Share Resource set in a triple-core scenario                                                                                        | 46 |

| 3.8  | For design D2, the proposed DSS execution time (y-axis) at 16MHz                                                                               |               |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|      | when increasing the duration (x-axis) of the Share Resource set. The                                                                           |               |

|      | blue and red dotted lines represent the serial scheduler for dual-core and triple-core scenarios, respectively                                 | 47            |

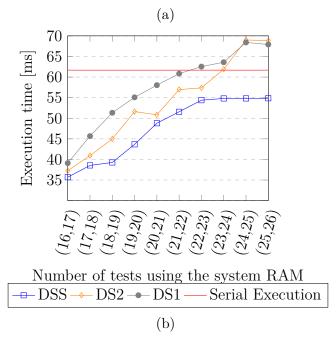

| 3.9  | · · · · · · · · · · · · · · · · · · ·                                                                                                          | 41            |

| 3.9  | For D1, evolution of the execution time at 16MHz of different single-                                                                          |               |

|      | resource decentralized schedulers with respect to the serial sched-                                                                            |               |

|      | uler when considering an ascending order. The dual-core scenario is                                                                            | 4.0           |

| 0.10 | shown in (a), the triple-core one in (b)                                                                                                       | 49            |

| 3.10 | For D1, evolution of the execution time at 16MHz of different single-                                                                          |               |

|      | resource decentralized schedulers with respect to the serial sched-                                                                            |               |

|      | uler when considering a descending order. The dual-core scenario is                                                                            | - 0           |

| 0.11 | shown in (a), the triple-core one in (b)                                                                                                       | 50            |

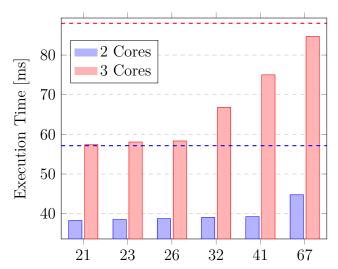

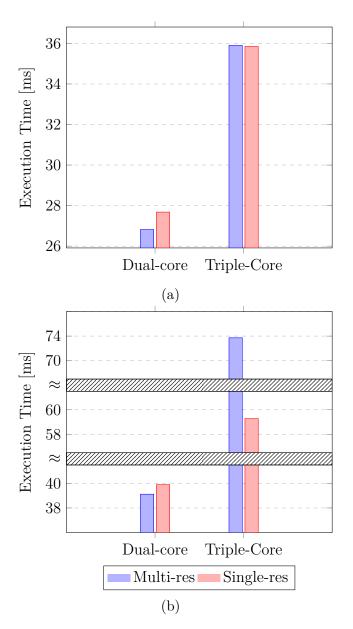

| 3.11 | Multi-resource scenario: schedulers performances in dual and triple-                                                                           |               |

|      | core configuration. Picture (a) reports the figures for the design D1,                                                                         |               |

|      | whereas (b) for D2. The light blue bars represent the multi-resource                                                                           |               |

|      | scheduler. The red ones represent the single-resource alternative,                                                                             |               |

|      | with the shared resources logically grouped into a unique shared                                                                               |               |

|      | resource. In (b) the y-axis was split in different ranges to allow a                                                                           | <b>-</b> c    |

| 4 1  | better observation.                                                                                                                            | 52            |

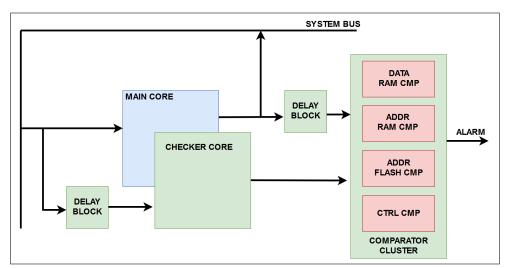

| 4.1  | Typical delayed DCLS architecture                                                                                                              | 56            |

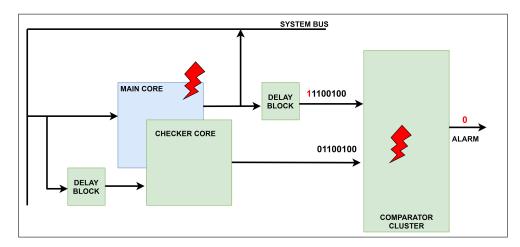

| 4.2  | Example of latent fault causing a failure of the main core being masked.                                                                       | 57            |

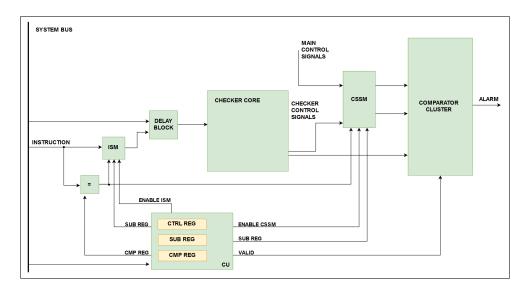

| 4.3  | Architecture of the system including the LSMU. For simplicity, the                                                                             | 0.0           |

| 4 4  | main core is not depicted in this picture                                                                                                      | 60            |

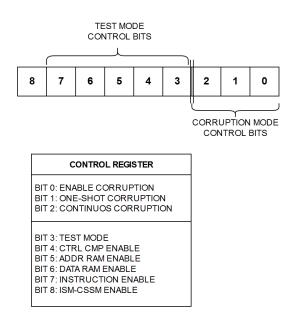

| 4.4  | Control register (CTRL REG) description. The ADDRESS FLASH                                                                                     | cc            |

| 4 =  | CMP are automatically enabled when the TEST MODE bit is set.                                                                                   | 62            |

| 4.5  | A possible self-test program that leverages the ISM for testing the                                                                            |               |

|      | DATA RAM CMP. Before ISM activation, both cores execute the                                                                                    |               |

|      | same instructions. After its activation, the instructions underlined                                                                           | CC            |

| 1 C  | in red are those substituted in the checker core                                                                                               | 63            |

| 4.6  | Fragment of self-test program testing the ADDRESS FLASH CMP.                                                                                   | 64            |

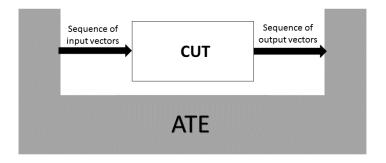

| 5.1  | Test vectors-based end-of-manufacturing test scenario for a generic                                                                            | 70            |

| T 0  | sequential CUT                                                                                                                                 | 79            |

| 5.2  | STL-based in-field test scenario for a CPU-based system                                                                                        | 80            |

| 5.3  | Graphical representation of the fault detection mechanism for STP-                                                                             | 0.5           |

| E 1  | FSIM1                                                                                                                                          | 83            |

| 5.4  | STP-FSIM3 scenario: the observability locations are marked in red.                                                                             | 85            |

| 5.5  | STP-FSIM4 scenario: the observability locations are marked in red. The OR1200 architecture.                                                    | 86            |

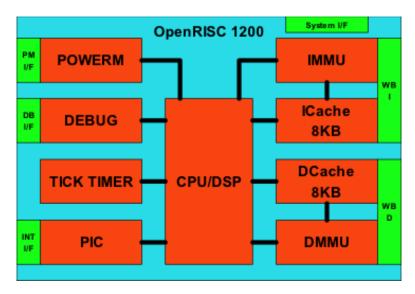

| 5.6  |                                                                                                                                                | 87            |

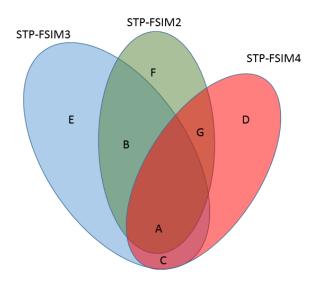

| 5.7  | The detected faults by STP-FSIM2, STP-FSIM3, STP-FSIM4 and                                                                                     | 00            |

| K 0  | their possible intersections. In this case, E=F=G=0                                                                                            | 90            |

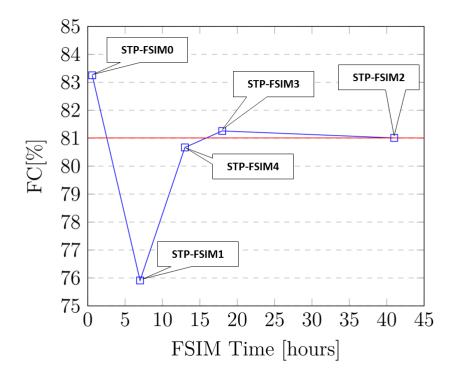

| 5.8  | Fault simulation methodologies: fault coverage accuracy versus fault simulation time. The red line represents the exact fault coverage figure. | <u>01</u>     |

|      | simulation time. The red line represents the exact fault coverage figure.                                                                      | $\mathcal{I}$ |

| 6.1 | The fault injection mechanism described [85]. The other design in-  |     |

|-----|---------------------------------------------------------------------|-----|

|     | puts and outputs are not shown here for simplicity                  | 98  |

| 6.2 | The proposed JTAG-based infrastructure. Only relevant pins are      |     |

|     | shown                                                               | 100 |

| 6.3 | Internal structure of the Observation Domain                        | 101 |

| 6.4 | Emulation Time vs Number of partial signatures                      | 104 |

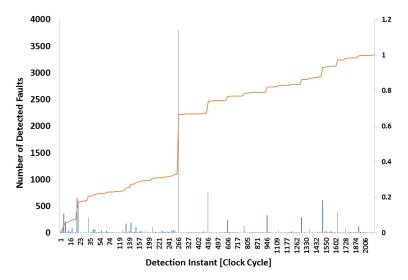

| 6.5 | Histogram and cumulative distribution function of the detection in- |     |

|     | stants (expressed in clock cycles)                                  | 105 |

## Chapter 1

## Introduction

Nowadays the automotive domain is one of the main drivers for the most recent technology advancements. The pursue over the last decade for fully autonomous (or self-driving) cars has radically changed the architecture of the embedded systems deployed in such domain. While originally relatively small System-on-Chips (SoCs) were deployed, today there is an opposite trend. Indeed, driven by the necessities of more complex software tasks required for implementing Advanced Driver Assistance Systems (ADAS), Multi-Processor SoCs (MPSoCs) can often be found in replacement of the simpler ones.

MPSoCs (or simply multi-core systems, the two terms are considered here as synonyms) are mixed-signal SoCs, since they include on the same silicon die both a digital (consisting of multiple processor cores, memories) and an analog portion (e.g. analog-to-digital converters). Since the focus of this thesis is on the digital portion, it is exclusively further discussed in the following. Before being adopted, the MPSoC must satisfy the requirements imposed by so-called functional safety standards. For the automotive field, the ISO 26262 [50] regulates the usage of electronics devices. The standard is an adaptation to automotive systems of the more general IEC 61508 [49]. The ISO 26262 covers the entire spectrum of the functional safety of electronics components for automotive applications, from the software to the hardware. Specifically to the hardware, the ultimate goal is to avoid that a failure in a given hardware block provoke a catastrophic consequence (e.g., damage to human beings). For avoiding such catastrophic consequences, the standard suggests different solutions. These are called *safety mechanisms*. A safety mechanism is a portion of the system intended for detecting faults and controlling system failures in order to achieve or maintain a safe state. Depending on the risk associated to the failure of the system, the standard defines the Automotive Safety Integrity Levels (ASILs). They are labeled with A, B, C and D. Systems, or more in general a hardware module, labeled as ASIL A signifies that the module is not safety relevant. On the other hand, modules labeled ASIL D are the most critical ones. For each of these levels, the standards defines the most appropriate safety mechanisms in order to meet some minimum reliability requirements. Failures are caused due to the occurrence of random hardware faults, which are distinguished in Single-Point Faults and Multi-Point Latent Faults. The former are immediately effective faults, meaning that when one of these faults occurs, the effects of its occurrence lead to a failure within few clock cycles. Instead, Multi-point Latent faults are faults within the safety mechanism. Their occurrence do not cause directly a failure. However, they might become dangerous when a second fault arise in the module guarded by the safety mechanism. Concerning these two types of faults, the ISO 26262 defines two metrics (directly related to the reliability requirments): The Single-Point Fault Metric (SPFM) and the Latent Fault Metric (LFM). Each of the above-mentioned ASILs has different requirements for these two metrics (Table 1.1). For assessing whether a given hardware module meets the required metrics for the targeted ASIL, the Failure Mode Effects and Diagnostic Analysis (FMEDA) [62, 73 is performed. It defines failure modes, failure rate and diagnostic capabilities for a given hardware module. In the context of this thesis, diagnostic capabilities refer to the ability of detecting specific faults (either single or multi-point faults). Together with the failure rate, they directly contribute to determine the SPFM. The failure rate is measured in FIT (Failure In Time) and strongly depends on the technology node used for manufacturing the device. The diagnostic capabilities are expressed with the Diagnostic Coverage (DC). The DC indicates the number of critical faults leading to a failure detected by the safety mechanism under analysis. It is normally computed resorting to fault injection campaigns. For these, two fault models are typically considered: the stuck-at and the Single-Event Upset or Transient (SEU and SET respectively). During early dependability analyses, the SPFM can be roughly approximated with the DC. Instead, the LFM indicates the number of latent faults covered in the safety mechanisms and it is computed considering exclusively stuck-at faults. Throughout this manuscript, the bare fault coverage of a given safety mechanism or self-test procedure is simply referred to as Fault Coverage. With Diagnostic Coverage instead the one considering the most critical faults only.

Table 1.1: SPFM and LFM Requirements for Safety-relevant Modules

| ASIL         | SPFM/DC     | LFM            |

|--------------|-------------|----------------|

| В            | $\geq 90\%$ | $\geq 60\%$    |

| $\mathbf{C}$ | $\geq 97\%$ | $\geq \! 80\%$ |

| D            | $\geq 99\%$ | $\geq 90\%$    |

For these two metrics, the standard also defines the Fault Tolerant Time Interval (FTTI). The FTTI is defined as the time interval required for detecting a fault and then react accordingly. For example, for ASIL D devices the FTTI for single-point

faults is in the range of 10-150ms. For the latent faults, the FTTI is expressed as a multiple of 10 hours.

In general, certifying an SoC for the highest ASILs (C or D) does not require deriving the SPFM and LFM metrics considering the SoC as a whole. Instead, it is followed the process known as ASIL decomposition. For each safety-relevant sub-module of the SoC, one or more safety mechanism is devised. Then, the final coverage achieved on the entire SoC is given by the combination of the coverages achieved in each sub-module. For example, considering the LFM for an ASIL D SoC, this implies in practice that it is not necessary to achieve a 90% coverage in each sub-module.

When considering the SPFM metric, the most commonly used safety mechanisms are based on redundancy. These are also called *primary safety mechanism*. When dealing with memories [38, 25, 63], Error Correction Codes (ECCs) are used to protect against bit flips or errors in the memory array. More recently, advanced schemes known as End-to-End ECCs [55] have been shown to be effective also to protect against faults arising in the data path from a processing element (e.g., a processor core) to the memory. As opposed with traditional approaches, End-to-End strategies computes the ECC when the data is actually leaving the processing element and it is send over the system bus to the memory. The ECC is send along with the data over the system bus. When the data reaches the memory, the ECC is computed again before being stored. In case the computed ECC differs with the one that was send, a fault occurred. In the most advanced schemes, the ECC is computed for control signals too.

For the processing elements as the processor cores, or safety-relevant hardware blocks as the Direct Memory Access (DMA), the most common strategy consists of replication [43]. For example, considering the processor core, the Dual-Core Lockstep (DCLS) [51] is the most commonly used. Two processor cores (main and checker) are paired together and fed with the same identical inputs. Their outputs are continuously monitored by a set of comparators that signal a mismatch due to the occurrence of a fault.

As already mentioned when introducing earlier the LFM metric, the additionally circuitry of these safety mechanisms is equally exposed to faults occurrence. This could invalidate the safety mechanism functionalities and might cause failures of the safety-relevant blocks to go undetected. Therefore, additional diagnostic safety mechanisms are required. They are exclusively intended for implementing in-field self-test mechanisms functionalities to avoid latent faults accumulation in the primary safety mechanisms. It is worth mentioning that the in-field test is more constrained in terms of resources and fault models compared to the end-of-manufacturing test. In general, the in-field test does not rely on an external tester (i.e., an ATE) and the test patterns must be internally generated/stored within the device itself. Moreover, since the test is performed when the device is already in the

mission environment there exist also narrow test windows in which test must complete. For these reasons, exclusively stuck-at faults are in practice considered when devising self-test mechanisms for the LFM metric. Indeed, if one would consider also more advanced faults models such as cell-aware ones [46], the test time required for reaching an acceptable coverage would exceed the available test window.

When considering automotive devices (either single or multi-core), the in-field test is further distinguished into the Power-On Self-Test (POST) and the on-line self-test [82]. The former is the self-test performed when the device is turned on. The latter, is the in-field test performed concurrently with the mission software that the SoC is supposed to be running.

During the POST, the preferred self-test mechanisms are based on the Logic and Memory Built-In Self-Test principle (LBIST and MBIST respectively)[89, 66]. The former addresses permanent faults in the safety-related digital logic. The latter instead within the embedded memories. In the literature there exist MBIST strategies [74] that allow for a transparent execution with respect to the memory content. On the other hand, the LBIST requires a full system reset after its completion. Indeed, LBIST is based on the already existing scan logic and thus it produces non-functional stimuli. Therefore, its applicability is limited to the POST only.

This could become problematic if the time interval between two power-on events is too long, as in the case of several hours of continuous operations. Consequently, since latent faults must be checked even when the system is fully on-line, Software Test Libraries are increasingly becoming used. An STL consists of a set of software self-test procedures (or programs), and the main target are permanent faults within the processor core [83, 58, 76, 42, 4, 41, 56, 81]. This technique is also known in the literature as Software-Based Self-Test or SBST. The idea is relatively simple: when the target device corresponds to or includes a processor, we can force it to execute a suitable piece of code, possibly reading some input data and processing them in a carefully selected manner. The produced output data are accumulated to form a test signature. Such a signature is then used in filed to determine whether the test passed or failed. Normally, this kind of self-test exclusively relies on the already-existing on-chip resources.

In contrast with the non-functional approaches such as the LBIST, the STL produces exclusively pure functional stimuli. However, unlike the traditional functional tests, this approach relies on structural information of the processor core under test (i.e., a gate-level description). Therefore, it is possible to compute a test coverage with respect to a given fault model. Since the self-test is performed with the processor operating in mission mode, normally this self-test approach complements the non-functional stimuli produced by the LBIST [65, 45]. Indeed, it is often the case that due to test mode constraints or clock gating structures, some portions of the design are not fully accessible by the LBIST.

When used in automotive devices [13], the STL has two main roles depending on the targeted ASIL. For ASIL B devices, the STL is often used in conjunction with other techniques as primary safety mechanisms to detect the occurrence of single-point faults. For the most critical ones (namely ASIL C or D), the STL is used for the purpose of detecting latent faults to avoid their accumulation in the checker (or main) core of the DCLS configuration.

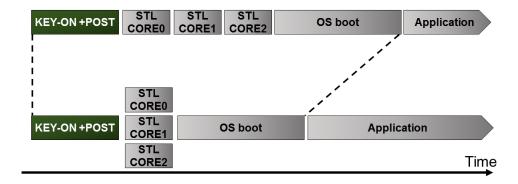

For both purposes, the STL is composed of two main portions: a boot-time and a run-time portion. The self-test programs belonging to the first category are executed during the namesake phase of the device, when the system is entering the on-line phase. In this phase, the processor initializes the different peripherals, the internal RAM blocks, the PLL and others. Before acting on these, the processor executes the boot-time self-test programs. The goal of this self-test is to check most of the processor functionalities. Self-test programs belonging to this category have complete access to the available hardware resources: the processor Special Purpose Registers, the Interrupt Vector Table. Additionally, they trigger exceptions and preemption is not allowed. For the sake of test purposes, they require to access specific addresses in the shared portion of the system RAM, outside the boundaries of the processor stack frame. Although there are in general fewer real-time constraints on the execution of these kind of self-test programs, there is typically an upper bound for the self-test to complete (also for sake of system availability). Indeed, the MPSoC is part of a lager Electronic Control Unit (ECU). Within an automobile, there are several ECUs that exchange information over a local network. At the key-on, all the ECUs execute their own self-test and acknowledge over the network the whether the test passed or failed. To avoid waiting endlessly for a control unit response (which might be stuck due to a fault), a timeout is typically set (which represents the aforementioned upper bound).

The self-test programs that belong to the second category are executed when the system is fully on-line. That is, the operating system and the application software are already running. They are conceived to coexist with the application source code and they target mainly the computational units (e.g., arithmetic units) within the processor core. Since they are executed in real time, they do not alter the processor status and can be interrupted in case higher priority tasks require to be executed. Differently than the boot-time self-test programs, the run-time ones do not access system RAM addresses outside the processor stack frame. This kind of self-test programs are designed to have minimal access to on-chip resources (i.e., minimal intrusiveness) due to the coexistence with the application software. Therefore, in general, the achievable coverage is lower compared to the boot-time ones.

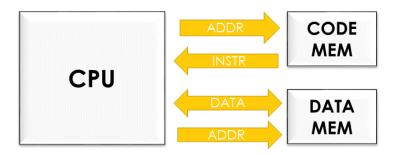

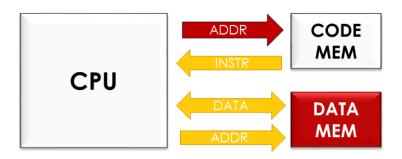

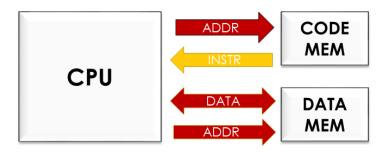

The effectiveness of an STL (technically called fault grading) is normally assessed with fault simulators [14] and it is historically the most expensive part of the development flow. Additionally, the functional fault simulation is increasingly often required. This kind of fault simulation is an emerging approach that stems from the needs of the FMEDA analysis. Recently, it is being supported by the EDA vendors too. This methodology differs from the traditional one since it simulates in a unique model both the processor and the memories (data and code). Specifically,

the stimuli are retrieved from the memories, unlike in the traditional one in which the fault simulator provides to the design under test (e.g., the processor) the input stimuli (usually stored in a textual file).

In general, fault simulation is a critical bottleneck in FMEDA analysis since it is required for several applications.

In order to address the growing complexity stemming from the usage of MP-SoCs, there has been a considerable effort from the research community in order to improve the self-test capabilities. Most of these efforts were directed towards the improvement of the LBIST [69, 60, 68, 67]. Specifically, the lager becomes the circuit under test the higher is the pattern count for reaching the target LFM coverage. This implies that the test application time increases, because patterns are generated internally. Furthermore, the scan shift frequency is normally limited for sake of power consumption. Towards this end, the main research efforts considered test point insertion (often shared with same test compression logic used for end-of-manufacturing testing) for reaching the same coverage while reducing the pattern count. Additionally, new LBIST schemes have been introduced that considers the necessities of the automotive integrated circuits such as the LBIST with Observation Scan Technology (LBIST-OST) [70]. In that approach, a dedicated scan chain is inserted in the design with the only purpose of capturing data from the combinational logic during the shift cycle. This yield a significant advantage, since traditionally exclusively during the capture cycle the combinational logic is observed.

For the STL-based approaches, or more in general, those based on the SBST principle the same is not true. Indeed, most of the research efforts focused on the end-of-manufacturing testing only. In that field, several works proposed different solution aiming at reducing the test application time [6, 5, 37]. Since the in-field self-test presents different constraints with respect to the scenario of the end-of-manufacturing testing, these techniques are clearly not applicable.

The main problem to be faced when considering STLs for the in-field self-test of MPSoCs is still the test application time. However, the problem is not related to the number of stimuli to be provided. The processor cores used in MPSoC are often the same used in single-core SoCs for sake of shortening the design cycle and time-to-market for new devices. Therefore, the processor complexity is not altered and the already-developed self-test algorithms for testing the processor modules are re-used. The difference in MPSoCs is that all the available processor cores must execute the same STL in almost the same test time window of the single-core SoC. Ideally, a parallel execution of the STL would be the best solution. However, this is not always possible, as it is better detailed in the dedicated chapter. Indeed, other complications arise since the on-chip resources (in terms of available memory) for the STL are usually limited.

For the reasons listed above, rather than the development of new self-test algorithms, the thesis focuses on effective strategies for the parallel self-test when in

field. The end goal is to reduce the test application time, while maintaining at the minimum the amount of required resources.

While there exist two main approaches for the self-test of latent faults (i.e., the software and the hardware ones), during the development of the thesis a further approach was explored: the hybrid one. This approach is based on a cooperation between software and hardware modules to implement the self test. Specifically to this thesis, a hybrid on-line self-test approach was investigated as countermeasure for latent faults in the comparators of a DCLS system. For this and similar purposes, the hybrid self-test approach is shown to be a valid alternative to the most expensive (in terms of physical resources) hardware-based approaches. At the same time, they inherit the flexibility of the software while overcoming the classical limitations of these approaches (i.e., they are able to produce functional stimuli only).

The second major focus of this thesis was on the fault grading process. On one hand the idea was to improve the fault simulation methodology for STL to meet the recent improvements concerning the functional fault simulation. Different techniques to alleviate the effort required for the functional fault simulation were proposed. Such techniques target the two different usages of the STL. That is, part of the techniques are for the STL used as primary safety mechanism. This is the case of single-core SoC or specific processor or co-processor within an MPSoC intended for security tasks. The other techniques are for the STL used against latent faults in a DCLS configuration. On the other hand, the fault grading process can be further improved when considering FPGA-based fault emulation. Historically, fault emulation was limited to transient fault models, most notably SET and SEU. This was due to the relative limited capacity of the emulators themselves. However, the recent improvements in the FPGA emulators capacity, now able to support several billions of logic gates, make the emulation of permanent faults affordable. Differently than the works present in the literature concerning fault emulation, in the scope of this thesis the focus was the observation mechanism. Such term refers to the mechanism through which a given fault can be marked as detected or not. The one developed in this thesis resembles the fault dropping mechanism implemented in modern fault simulators. This method allows to reduce the time required for each the fault simulation since faults are simulated until a difference is detected (with respect to a fault-free reference). The same principle was exploited in the proposed fault emulator too, allowing for a reduction of the effort required for the fault grading.

## Part I

## On-line self-test mechanisms for automotive MPSoCs

## Chapter 2

# Deterministic in-field parallel execution of self-test programs in MPSoCs

The purpose of this chapter is to introduce the problems to which self-test programs are exposed when executed in parallel in an MPSoC. These problems are always present independently from the selected scheduling approach. Indeed, embedded software executed in a multi-core context suffers of a limited timing predictability due to the higher system bus contention. When dealing with self-test procedures, this higher contention might lead to a fluctuating fault coverage or even the failure of some test programs when in field. To mitigate this issue, a cache-based strategy is proposed. The methodology does not require significant modifications of the already-existing algorithms and it does not introduce penalties from the memory footprint perspective. Along with these advantages, it does not require any additional on-chip resources.

This chapter is organized as follows: initially, a background section provides a clear problem statement and an overview of the related works already present in the literature. Then the proposed strategy is detailed. Finally, experimental results demonstrate that it is possible to achieve a stable execution while also improving the state-of-the-art approaches for the on-line testing of embedded microprocessors. The effectiveness of the methodology was exhaustively assessed on representative processor modules of an industrial MPSoC manufactured by STMicroelectronics.

This proposed approach and experimental results were published in [34].

#### 2.1 Background

#### 2.1.1 Problem statement

The main idea of the self-test via software is to convert test patterns into software instructions and accumulate their results to create a so-called test signature. Then, such a signature is compared with the expected test signature (obtained in a fault-free scenario, for example resorting to simulators) to determine whether the test passed or failed. When the test is executed in field, the test signature represents the only way to safely detect the occurrence of faults. When considering an MP-SoC, a parallel execution of an STL is attractive for shortening the test application time. For the vast majority of the self-test programs composing an STL, this does not constitute a problem. However, some boot-time self-test programs, in order to be effective, require a proper sequence of instructions to be executed without any interruption. In MPSoC, this assumption cannot be guaranteed anymore. Indeed, the embedded software running in a multi-core context suffers of a limited timing predictability [61, 20], due to the higher system bus contention. These conflicts on the system bus block the processor pipeline when fetching instructions from the main memory. Due to these clock cycles of stall, the exact stream of instructions entering the pipeline cannot be determined in advance anymore. In an MPSoC, this has two important consequences on the self-test procedures requiring a specific sequence of instructions. The first one concerns the fault grading: the fault coverage is uncertain and it might vary depending on which portion of the processor is excited due to the system bus activity. Because of this, a given fault location might not be excited correctly and therefore remains undetected. This represents a serious concern, since the ISO 26262 standard imposes stringent quality requirements in terms of achieved fault (or diagnostic) coverage. The second one is related to the signature generated by the test program, which is now unstable. It means that the self-test procedure cannot safely identify whether the mismatch in the signature is due to the occurrence of a fault or due to an unexpected instructions stream.

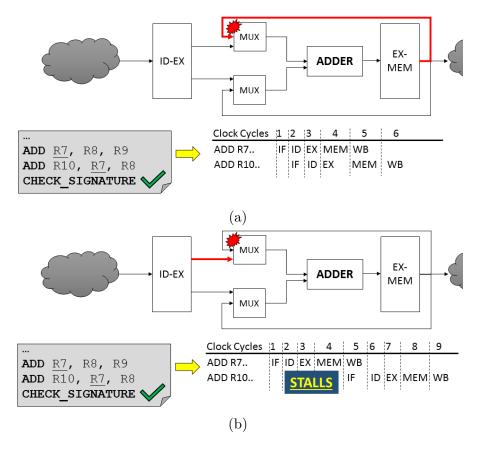

For better clarify this problem, let us consider two examples: the forwarding and hazard detection mechanism of the classical 5-stage pipeline of the DLX processor [77] and two self-test routines for testing such mechanisms.

Let us consider the forwarding mechanism. The reported example considers forwarding among two consecutive instructions. It is important to note that the same reasoning is perfectly applicable even to more complex multiple-issue processors. The only difference is that the forwarding can also take place among two consecutive issue packets. Let us focus on the following forwarding path: the EX to EX path that fed with the first operand the processor adder. Figure 2.1a shows a portion of the assembly code testing the aforementioned path, along with its evolution across the pipeline stages in a single-core scenario.

In this case, the forwarding mechanism is excited correctly. The second add

Figure 2.1: (a) Single-core execution of the program. (b) Multi-core execution of the program. In red the different paths activated by the same program.

instruction enters the pipeline exactly one clock cycle after the first one, since the memory subsystem has not produced any stall. Figure 2.1b represents still the same code fragment, but in a quite different scenario. It is assumed that the processor is part of a larger multi-core system, and the self-test procedure is executed in parallel by the other cores. As a result of the other processors' activities, the accesses to the memory subsystem are delayed. As depicted in that figure, the targeted forwarding path is not triggered at all. The second add enters the pipeline at the fifth clock cycle and can retrieve the content of R7 directly from the register file, without activating the forwarding path. This is a possible scenario that a self-test routine might encounter when executed in parallel in an MPSoC. In this context, the self-test procedure yield a correct signature. Indeed, the results produced by the two operations is still valid. However, the targeted forwarding path was not activated at all. Thus, although it returns a correct signature, the fault coverage is likely to be quite different since it varies according to the whole system activity.

When testing hazard detection mechanisms, in order to detect the occurrence of performance faults [48] the processor Performance Counters can be exploited

(when available). Performance Counters that count the number of pipeline stalls are particularly useful since they could ease the detection of malfunctions in the hazard detection unit (e.g., stalls inserted between instructions when not needed). The self-test programs is the same seen before for the forwarding mechanisms, but this time the Performance Counters contribute to the signature. In this case, it is likely that the test program will produce an unstable signature. Considering the examples of Figure 2.1b the execution time is slightly increased due to the additional stalls, but yet enough for altering the values of the Performance Counters, that will report 3 additional stalls. Once again, these stalls are completely unpredictable and consequently also the signature.

Even though these phenomena have been described using as examples the forwarding and hazard detection units, they are applicable to all those self-test procedures that require a specific sequence of instructions to be executed without interruptions.

To mitigate these issues and achieve a deterministic execution, a cache-based approach has been explored. This well matches the requirements of safety-critical embedded software, for which predictability is mandatory and the memory resources are limited.

#### 2.1.2 Related works

The usage of caches has been explored to store the self-test procedures intended for end-of-manufacturing testing of processors within a shared-memory multi-core system [6]. The purpose of that work was to reduce the test application time, avoiding off-chip memory accesses. The method is applicable exclusively for end-of-manufacturing, since it assumes that the self-test procedures are loaded into the caches through an external tester (which is not available when in field). Similarly, in [87] it was shown that a cache-aware test scheduler can take advantage of the memory hierarchy for speeding-up the run-time tests. Differently from these related works, the proposed approach deals with the in-field execution of boot-time procedures, and it uses caches for addressing the uncertainties introduced by a multi-core architecture.

A possible alternative to the proposed one consists in exploiting the processor Tightly-Coupled Memories (TCMs, also known as scratchpad memories) [7, 9]. This approach is typically adopted for the execution of real-time programs. Such programs are copied (during the system boot) and then executed from the instruction TCM when required. Conceptually, TCMs are similar to caches since they consist of a bank of SRAM local to each processor. Unlike caches, there is not the concept of cache miss or hit, since data or instructions have to be copied explicitly to these memories before being used. However, the fundamental drawback is that part of the TCM should be permanently reserved for test purposes (the amount of extra memory occupied is proportional to the size of the test program). Clearly,

this impacts negatively on both portability and flexibility of the STL.

## 2.2 The cache-based execution approach

The vast majority of computer programs exhibit the so-called principle of locality [77]: that is, a given program will access a (relatively) small portion of the available address space. Two locality principles exist: temporal and spatial locality. The former states that if a given memory address is referenced, then it is likely that it will be referenced again soon. The latter stems from the observation that programs are generally executed sequentially and they seldom branch far from the actual program counter value. Additionally, data are often stored in contiguous memory locations: therefore, if a given memory location is accessed, then it is likely that the locations nearby will be accessed soon. Caches leverage these principles, by storing the content the most referenced addresses (i.e., data and instructions). In a multi-processor system, this provides isolation, considerably increasing the processor performances. Although these advantages, the caches are not deterministic since the actual increase in performance depends on the program length and organization, the cache size itself, and how often a context switch is performed. Therefore, issues could arise when using caches in conjunction with self-test procedures, since some of them require a precise timing.

However, it is possible to achieve a deterministic cache-based execution if the test program:

- it is executed without any interruption;

- it exhibits strong temporal and spatial locality.

Given these two conditions, the idea is to move the self-test routine within the innermost level of caches (i.e., the ones private to each processor core), isolating its execution from the rest of the system.

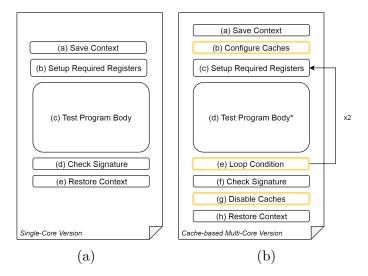

From the above mentioned definitions of the locality principles, it is possible to derive a general structure, that embeds the single-core version of the self-test procedure. Given a generic boot-time test program, the few modifications required are:

1. The test program should be executed twice in a loop-based fashion. The body of the loop (blocks c and d in Figure 2.2b) is represented by the instructions intended for testing the processor which compose the single-core self-test procedure (Figure 2.2a, blocks b and c). This allows for a strong temporal locality, since all the addresses are referenced exactly twice. During the first iteration (hereinafter loading loop, Figure 2.3a), the test program is moved into the instruction cache. At the same time, the content of the data memory addresses referenced (if any) during this first iteration are moved within the

Figure 2.2: The proposed Cache-based strategy. On the left-hand side the single-core version. On the right-hand side the modified multi-core test program version. In case of no-write allocate caches, the Test Program Body might be lightly modified.

data cache, assuming a write allocate cache memory. If this is not the case (i.e., a no-write allocate policy) each store operation must be followed by a dummy load operation to the same address. This will provoke a read cache miss, that in turn causes data to be moved within the data cache. Therefore, during the execution loop all the store operations will not generate a write miss, since they will find the proper data already in cache. It is important to note that during the loading loop the test program must not perform any check of the signature. Since the first execution might be still influenced by the other processors' activity, the computation of the signature is unreliable. Instead, the second iteration (the execution loop, Figure 2.3b) is the real test program execution. Since the program is executed entirely from the caches, the signature can be computed without the risk of being influenced by the rest of the system.

- 2. The entire test procedure code must be loaded in the instruction cache during the loading loop. This feature brings spatial locality and it avoids instruction cache misses during the execution loop that could potentially alter the signature. This condition implies that: