#### Doctoral Dissertation

Doctoral Program in Electrical, Electronics and Communications Engineering (34.th cycle)

## An Analog Pixel Front-End for High Granularity Space-Time Measurements

Lorenzo Piccolo

\* \* \* \* \* \*

Prof. Angelo Rivetti, Supervisor Prof. Michele Goano Co-supervisor

#### **Doctoral Examination Committee:**

Prof. A.B., Referee, University of ...

Prof. C.D., Referee, University of ...

Prof. E.F., University of ...

Prof. G.H., University of ...

Prof. I.J., University of ...

Politecnico di Torino June 22, 2022

| This thesis is licensed under a | Creative Commons License, Attribution - Noncommercial-                                                                                 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                 | attional: see www.creativecommons.org. The text amercial purposes, provided that credit is given to                                    |

| my own original work and doe    | nts and organisation of this dissertation constitute s not compromise in any way the rights of third to the security of personal data. |

|                                 | Lorenzo Piccolo Turin, June 22, 2022                                                                                                   |

|                                 |                                                                                                                                        |

### Summary

This thesis describes the results of the design and characterization work done to develop an analog front-end for a pixel front-end Application Specific Integrated Circuit (ASIC) with time measurement capability.

The work was carried out from 2018 to 2021, and has produced two prototype ASICs manufactured in a commercial 28 nm Complementary Metal—Oxide—Semiconductor (CMOS) technology. This includes the scheme design, simulation and implementation, as well as the experimental characterization of the prototypes and the design of the experimental setup employed. The main subject of the research is the analog part of the core channel of the ASIC. The main function of this circuit is to transduce the sensor signal into a format that best fits the input of the subsequent digitizer. Both of these functions play a crucial role in the time measurement process since they represent the first processing of the raw signal. Particular attention has been paid to minimize the time fluctuation contribution of this circuit to the overall system time fluctuation.

An important aspect to consider is that the front-end channel is part of a large multichannel system. This aspect influences the single channel design by imposing constrains arising from the pixel-matrix configuration. The channel must fit inside a limited pixel-area, while leaving room for the implementation of the other pixel dedicated circuits. The area limitation will also constraint the total power budget available to the analog front-end. Moreover, a certain degree of uniformity is required across the pixel matrix. These challenges have been addressed with novel architectural solutions. First, a new very front-end scheme has been designed in order to reduce the time fluctuations within the available power budget. Second, a discrete time technique has been implemented in order to equalize the channels while limiting the area and power consumption needed for this task.

The author's work was not only limited to the core channel. Given the systemlike nature of the project, design and test work was also carried out on a system level. The author is one of the three lead designers of the ASIC. Therefore, a crucial role has been covered in the definition of the pixels and matrix architectures and floor-plans. The main contribution was the integration of the full analog part of the pixel-matrix, including all the service and configuration blocks used to operate it. As a result, the whole pixel matrix can be operated by providing only one reference signal configured via a digital interface.

The main application for this type of ASIC is in future experiments in High Energy Physics (HEP). In this field, particles properties and trajectories are reconstructed by large detectors composed of many sensitive layers. The information gathered on the innermost layers is used to reconstruct the particle track in the process named tracking. This process is based on the particle hits positions and is used to date. However, HEP experiments such as the ones in Conseil Européen pour la Recherche Nucléaire (CERN), are planning to increase their accelerator nominal luminosity. In case of the Large Hadron Collider (LHC), this upgrade is scheduled in 2029. The luminosity boost will increase the chance of observing rare events by increasing the event rate. The downside of this approach is that the number of spurious events is also expected to rise, making current tracking techniques ineffective. This issue can be solved by adding a time measurement capability to the inner layers of the detector achieving what is called 4D-tracking. In principle, future detectors require a time resolution of at least 100 ps at the level of pixels tens of micrometers large. 4D-tracking demands therefore the research and development of new pixel front-end ASICs with timing measurement capability.

The construction of this type of detectors is beyond the sole scope of ASIC level design. In fact, in order to reach the required space-time resolution, the whole system must be tailored around this goal. The TimeSPOT project (Time and SPace real-time Operating Tracker) by the Italian institute for nuclear physics (Istituto Nazionale di Fisica Nucleare INFN) aims to research and develop a demonstrator detector suitable for high-luminosity HEP experiments. The demonstrator will be realized via a small-scale telescope that will include the pixel sensor matrix, the pixel front-end ASIC, and the readout electronics. The work presented in this thesis is actually part of the development of the Timespot ASIC family. The ASIC is researched in tandem with its sensor and readout in order to achieve the target specifications in terms of: space-time resolution, maximum event rate, data throughput, power consumption and radiation tolerance. The project time resolution specification has been defined on the basis of what is achieved by its sensor: 20 ps or better.

The 28 nm CMOS technology node was chosen over more conventional nodes for the field due to its superior jitter performance over power consumption. It also opens up the possibility to integrate more features in the same silicon area. The radiation hardness of this node is on par with the best results achieved in 65 nm and 130 nm nodes. The complexity of this technology has determined an additional challenge in terms of ASIC design.

Other applications for this ASIC can be found in other fields that require a granular space-time measurement such as: detector for space applications, medical equipments and in general detector for imaging applications.

The thesis will discuss the work done by starting with two introductory chapters and then moving to the description of the design and characterization work.

The introductory material is used to give context to the following chapter and to introduce concepts that will be extensively utilized throughout the whole thesis. Chapter 1 introduces the reader to the field of space-time measurement in HEP and its pixel front-end ASICs, including a small review of the ASICs currently in development. Chapter 2 presents the architecture, specifications and plans of the ASICs for the TimeSPOT project. Chapters 3 and 4 describe the design and characterization of Timespot0 analog front-end. Timespot0 is the first ASIC developed for the project. The design process is described in terms of the circuit architecture and implementation. A brief analytical derivation of the circuit operation is also included. Chapter 5 and 6 elaborates on the same topics regarding the second prototype: Timespot1. Timespot1 features a pixel-matrix with a thousand channels. The design description of chapter 5 is based on what was already presented in chapter 3 focusing on the changes between the two versions. This chapter also includes the system level work carried out specifically by the author. Finally, a brief conclusion is outlined at the end of the thesis.

## Acknowledgements

I would like to acknowledge Ilaria Gramigna Polic<br/>reti for the English proofreading.

I would like to dedicate this thesis to my colleagues from INFN Cagliari and INFN Milano. I hope that this thesis will serve as a reference for the future developments on our project.

## Contents

| $\mathbf{S}$ ι | ımm    | ary     |                                                         | III  |

|----------------|--------|---------|---------------------------------------------------------|------|

| Ta             | able ( | of Con  | atents                                                  | VIII |

| Li             | st of  | Table   | ${f s}$                                                 | XIII |

| Li             | st of  | Figur   | es                                                      | XIV  |

| 1              | Pix    | el Froi | nt-End ASICs with Timing                                | 1    |

|                | 1.1    | Overv   | riew                                                    | 1    |

|                |        | 1.1.1   | Space-Time Measurements in High Energy Physics          | 2    |

|                |        | 1.1.2   | Pixel Sensors with High Time Resolution                 | 4    |

|                |        | 1.1.3   | Pixel Front-End ASICs                                   | 6    |

|                | 1.2    | Archit  | tectures and Concepts                                   | 9    |

|                |        | 1.2.1   | The Electronics Chain                                   | 10   |

|                |        | 1.2.2   | Topology                                                | 12   |

|                |        | 1.2.3   | Readout Modes, Measurable Quantities and Data Formats . | 14   |

|                | 1.3    | Pixels  | s with Timing                                           | 18   |

|                |        | 1.3.1   | Resolution Contributions                                | 18   |

|                |        | 1.3.2   | Goals and Challenges                                    | 23   |

|                | 1.4    | Revie   | w on Timing Front-End ASICs                             | 25   |

|                |        | 1.4.1   | Timepix 3                                               | 25   |

|                |        | 1.4.2   | TDCpix                                                  | 27   |

|                |        | 1.4.3   | ALTIROC                                                 | 29   |

|                |        | 1.4.4   | Timepix 4                                               | 30   |

|                |        | 1.4.5   | ETROC                                                   | 33   |

|                |        | Revie   | w Table                                                 | 36   |

| 2              | The    | Time    | SPOT ASICs                                              | 37   |

|                | 2.1    | The T   | TimeSPOT Project                                        | 37   |

|                |        | 2.1.1   | The TimeSPOT Sensors                                    | 39   |

|                |        | 2.1.2   | The 28 nm CMOS Process                                  | 44   |

|                | 2.2    | The A   |                                                         | 47   |

|   |                | 2.2.1     | The Timespot  ASIC                   | 49        |

|---|----------------|-----------|--------------------------------------|-----------|

|   |                | 2.2.2     | The Timespot1 ASIC                   | 52        |

| 3 | Firs           | st Prot   | totype: the Timespot0 Analog-FE      | 59        |

|   | 3.1            |           |                                      | 59        |

|   | 3.2            |           |                                      | 61        |

|   |                | 3.2.1     | 1                                    | 63        |

|   |                | 3.2.2     |                                      | 64        |

|   |                | 3.2.3     |                                      | 67        |

|   |                | 3.2.4     |                                      | 67        |

|   |                | 3.2.5     |                                      | 68        |

|   |                | 3.2.6     | 1                                    | 69        |

|   | 3.3            |           |                                      | 70        |

|   |                | 3.3.1     |                                      | 71        |

|   |                | 3.3.2     |                                      | 72        |

|   |                | 3.3.3     |                                      | · -<br>73 |

|   |                | 3.3.4     |                                      | 74        |

|   | Trai           |           |                                      | 76        |

|   |                |           |                                      | 77        |

|   |                |           |                                      | 78        |

|   | Дау            | <i>.</i>  |                                      | •         |

| 4 | Tin            | espot     | 0: Analog Front-End Characterization | 81        |

|   | 4.1            | Setup     | and Method                           | 81        |

|   |                | 4.1.1     | Setup                                | 81        |

|   |                | 4.1.2     | Method                               | 84        |

|   | 4.2            | Measu     |                                      | 86        |

|   |                | 4.2.1     |                                      | 86        |

|   |                | 4.2.2     | Discriminator Characterization       | 90        |

|   | Exp            | eriment   |                                      | 95        |

|   |                |           |                                      | 96        |

|   |                |           |                                      |           |

| 5 | $\mathbf{Sec}$ | ond P     | rototype: the Timespot1 Analog-FE    | 97        |

|   | 5.1            | Archit    |                                      | 98        |

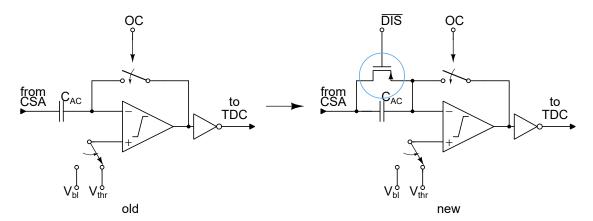

|   |                | 5.1.1     | Core Channel Updates                 | 98        |

|   |                | 5.1.2     |                                      | 05        |

|   |                | 5.1.3     | Digital Controls and TDC interface   | 10        |

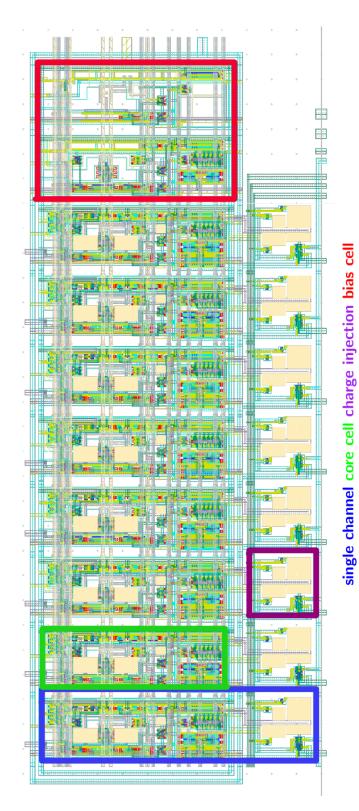

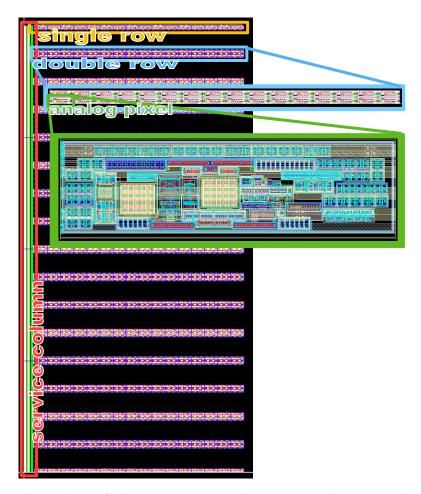

|   | 5.2            | Imple     | mentation                            | 13        |

|   |                | 5.2.1     | Analog-Pixel                         | 13        |

|   |                | 5.2.2     | Analog-Column                        | 15        |

|   | Trai           | nsistor i |                                      | 17        |

|   | Trai           | nsistor   | Sizing                               | 18        |

|   | Lavo           |           | •                                    | 19        |

| 6 T   | imespot  | 1: Analog Front-End Characterization | 121 |

|-------|----------|--------------------------------------|-----|

| 6.    | 1 Setup  | and Method                           | 121 |

|       | 6.1.1    | Setup                                | 122 |

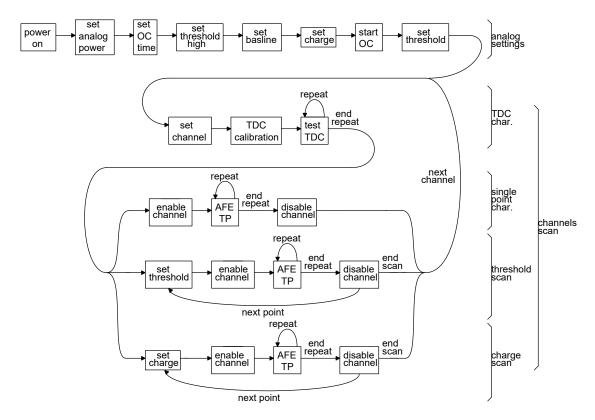

|       | 6.1.2    | Method                               | 124 |

| 6.    | 2 Meas   | urements                             | 128 |

|       | 6.2.1    | Offset Correction Operation          | 128 |

|       | 6.2.2    | Timing Performance                   | 131 |

| E     | xperimen | atal Setup Scheme                    | 135 |

| Cond  | clusions |                                      | 137 |

| Acro  | onyms    |                                      | 143 |

| Bibli | iography | <b>√</b>                             | 145 |

## List of Tables

| 1.1 | Review table of the most important pixel front-end ASICs operated |     |

|-----|-------------------------------------------------------------------|-----|

|     | in the first years of LHC                                         | 9   |

| 1.2 | State of art of Timing Front-End ASICs                            | 36  |

| 3.1 | Transistor sizing of the Timespot0 analog front-end               | 77  |

| 5.1 | Transistor sizing of the Timespot1 analog front-end               | 118 |

## List of Figures

| 1.1  | Layout of the new CMS Tracker                                       |

|------|---------------------------------------------------------------------|

| 1.2  | Example of particle tracking                                        |

| 1.3  | A high-pileup event                                                 |

| 1.4  | Concept of a 3D sensor                                              |

| 1.5  | Architecture of the focal plane imaging sensors developed at Hughes |

|      | Aircraft Co                                                         |

| 1.6  | SEM image of the Omega2 chip                                        |

| 1.7  | General electronics chain of a pixel front-end ASIC                 |

| 1.8  | Example of a possible floor-plan of a pixel front-end ASIC 13       |

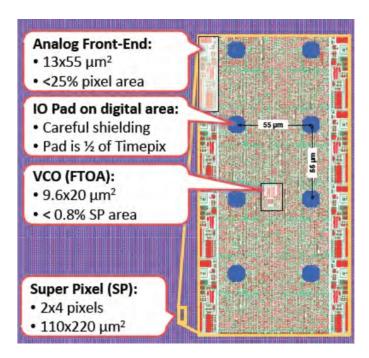

| 1.9  | Timepix3 super-pixel layout                                         |

| 1.10 | Schematic block representation of the Timepix3 super-pixel archi-   |

|      | tecture                                                             |

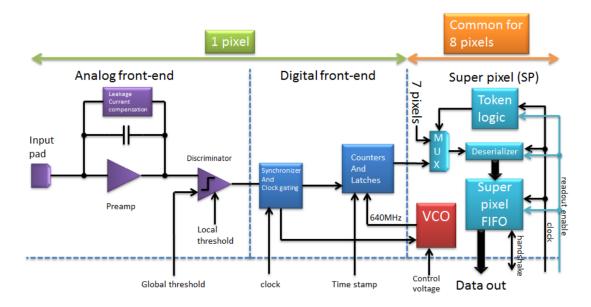

| 1.11 | TDCpix architecture and floor plan                                  |

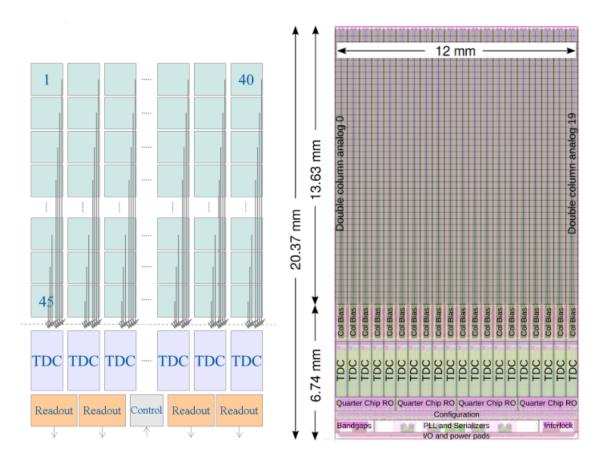

| 1.12 | ALTIROC1 layout                                                     |

|      | ALTIROC1 pixel architecture                                         |

| 1.14 | Timepix4 floor plan                                                 |

| 1.15 | Timepix4 pixel, super-pixel and column architecture                 |

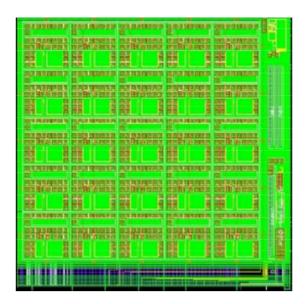

| 1.16 | ETROC1 architecture                                                 |

| 1.17 | ETROC analog pixel architecture                                     |

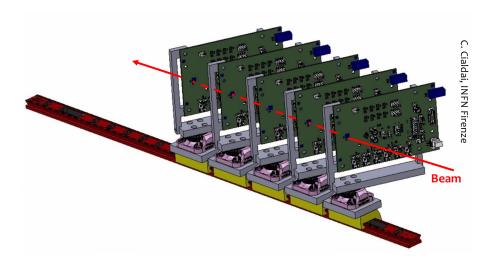

| 2.2  | TimeSPOT demonstrator telescope                                     |

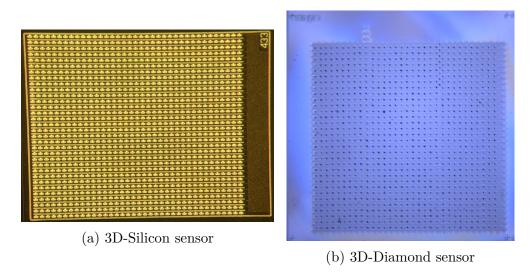

| 2.3  | Photograph of the TimeSPOT Sensors                                  |

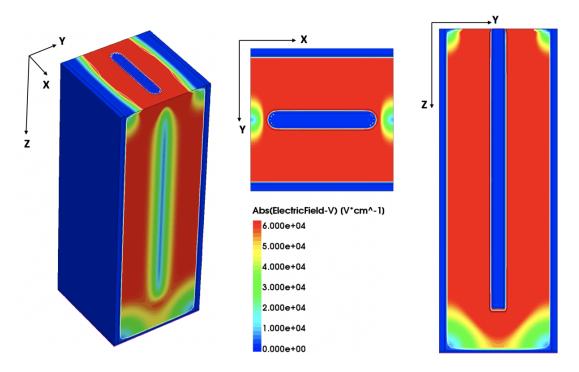

| 2.4  | Elementary cell of the TimeSPOT 3D-Silicon sensor 40                |

| 2.5  | Simulation: 3D-Silicon sensor signals TA distribution 41            |

| 2.6  | Measured signal characteristics of the 3D-Silicon sensor            |

| 2.7  | Elementary cell of the TimeSPOT 3D-Diamond sensor                   |

| 2.8  | Simulation: signals of the TimeSPOT 3D-Diamond sensor 43            |

| 2.9  | Plot: timing characteristics of the 3D-Diamond sensor               |

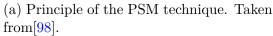

| 2.10 | Phase shifting mask technique and dummy gates 45                    |

| 2.11 | Photograph: channel strain                                          |

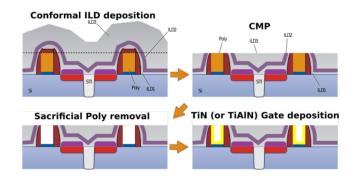

|      | Gate-last technique                                                 |

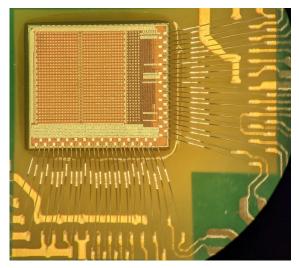

| 2.13 | Photograph of the TimeSPOT ASICs in scale                           |

| 2.14       | Photograph of the components used to interface the Timespot1 ASIC         |     |

|------------|---------------------------------------------------------------------------|-----|

|            | to the read-out system                                                    | 49  |

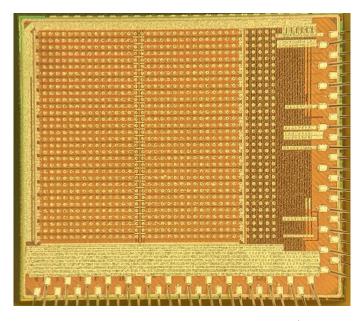

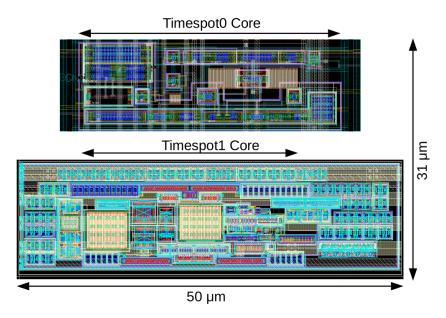

| 2.15       | Layout of Timespot0                                                       | 50  |

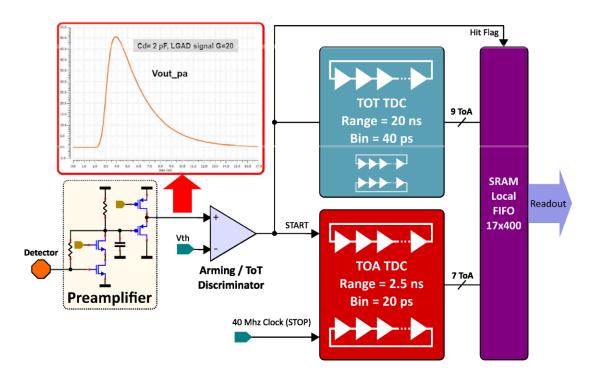

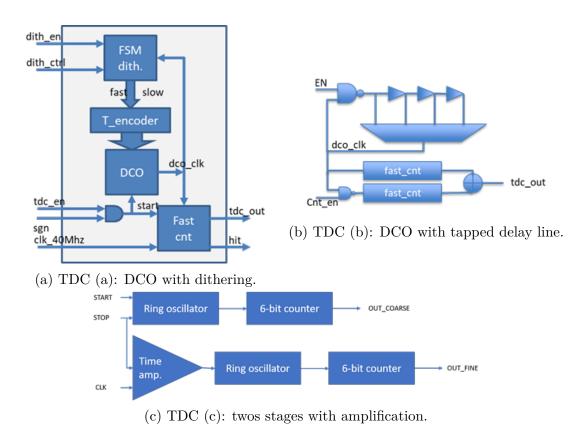

| 2.16       | Architectures of the three TDCs implemented in Timespot0                  | 51  |

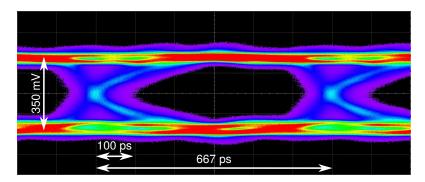

| 2.17       | Eye diagram of the LVDS                                                   | 52  |

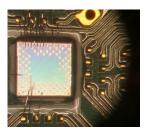

| 2.18       | Photograph of the Timespot1 ASIC                                          | 52  |

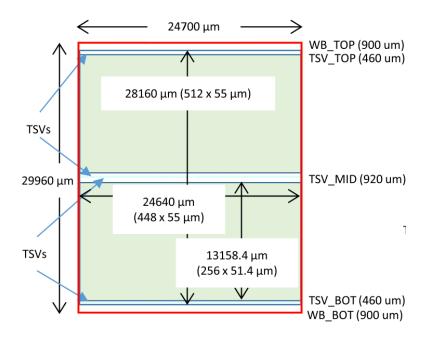

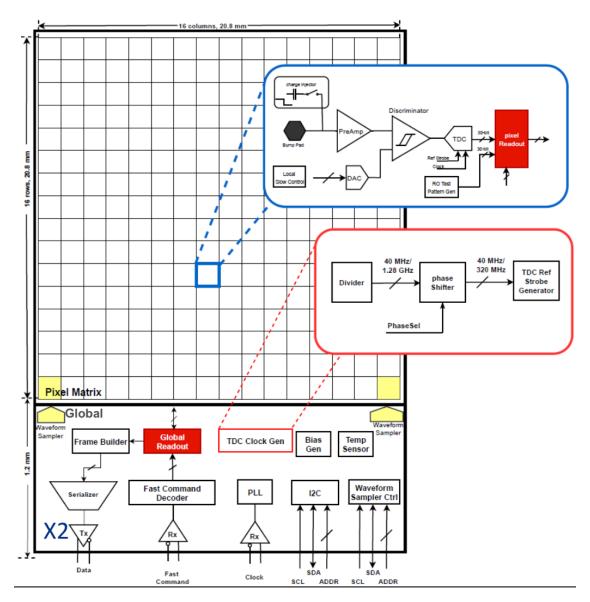

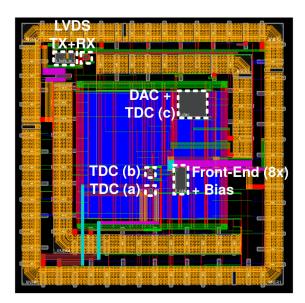

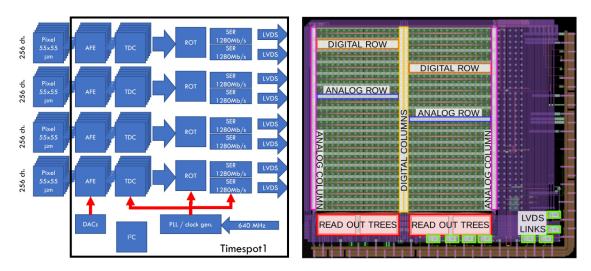

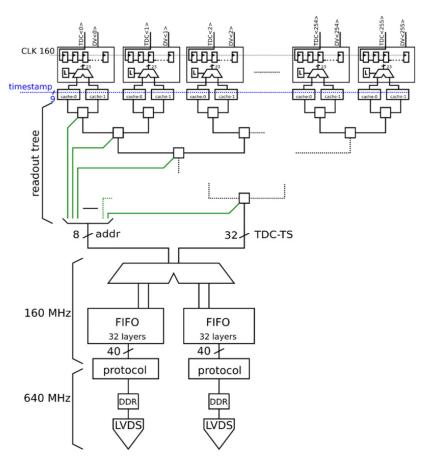

| 2.19       | Schematic block representation and layout of the Timespot1 ASIC.          | 54  |

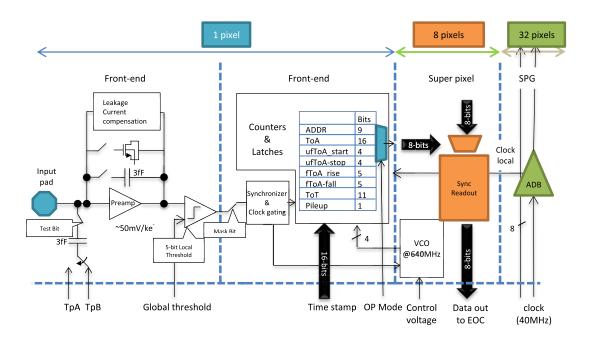

| 2.20       | Timespot1 pixel architecture                                              | 55  |

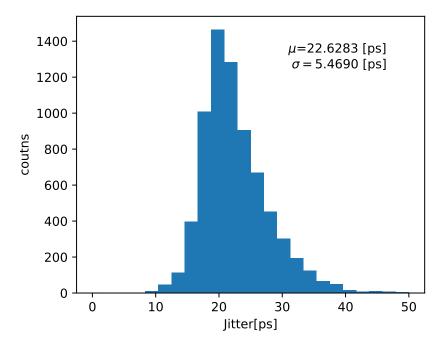

| 2.21       | Plot: distribution of the Timespot1 TDC time resolution                   | 56  |

| 2.22       | Timespot1 data-transmission circuit                                       | 57  |

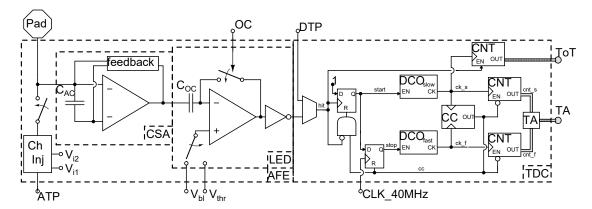

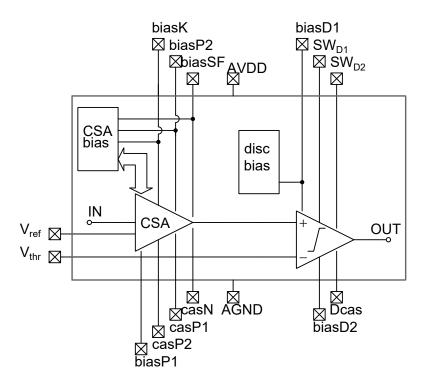

| 3.1        | Schematic block representation of the Timespot0 analog front-end          | 59  |

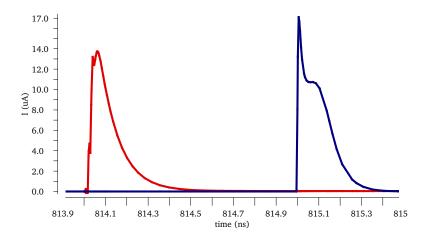

| 3.2        | Simulation: input signals                                                 | 61  |

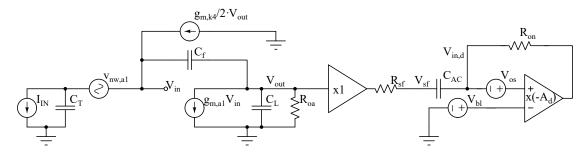

| 3.3        | Small signal equivalent circuit of the Timespot0 analog front-end         | 62  |

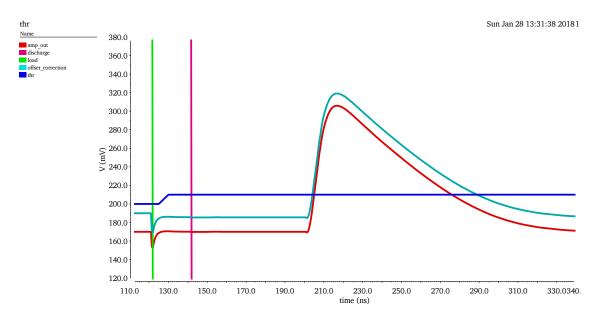

| 3.4        | Simulation: offset correction procedure                                   | 66  |

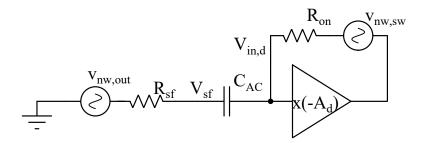

| 3.5        | Small signal equivalent circuit used to compute the discriminator jitter. | 70  |

| 3.6        | Timespot0 AFE biasing scheme                                              | 73  |

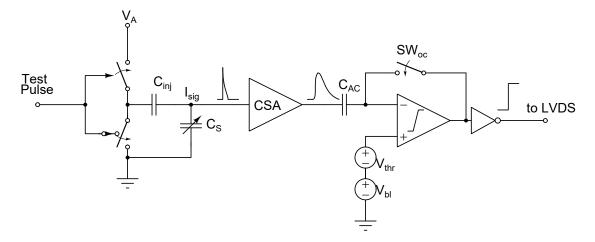

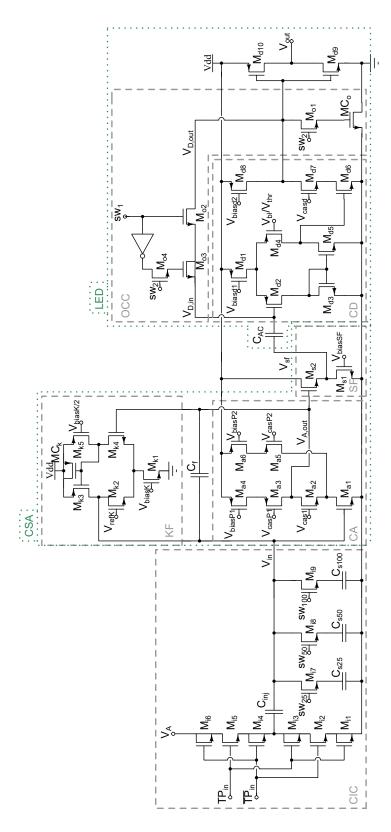

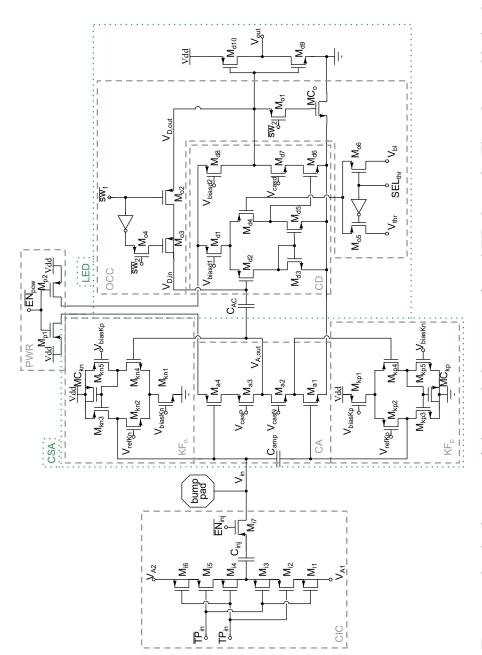

| 3.7        | Transistor level schematic of the Timespot0 analog front-end              | 76  |

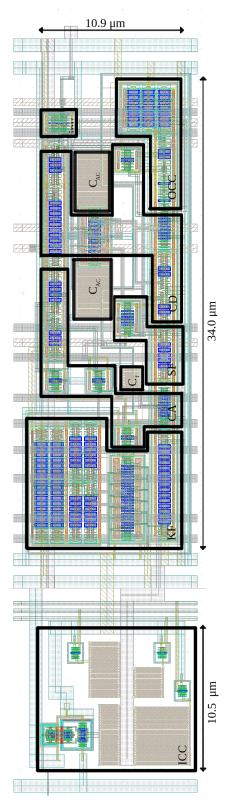

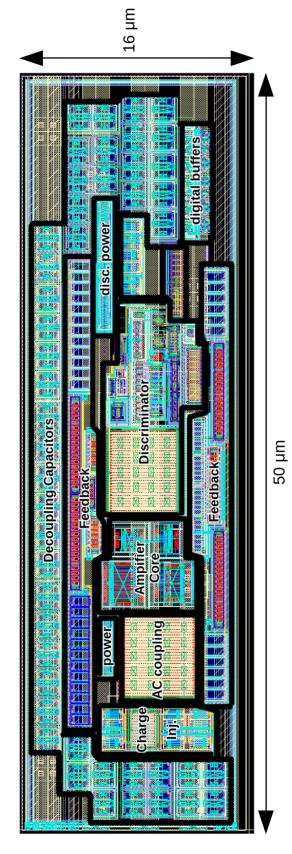

| 3.8        | Layout of the Timespot0 analog front-end                                  | 78  |

| 3.9        | Layout of the Timespot0 AFE channels and bias-cell                        | 79  |

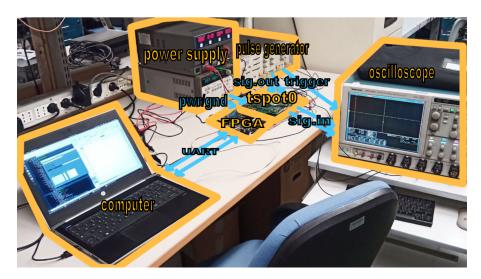

| 4.1        | Photograph of the setup used for the Timespot0 AFE characterization.      | 82  |

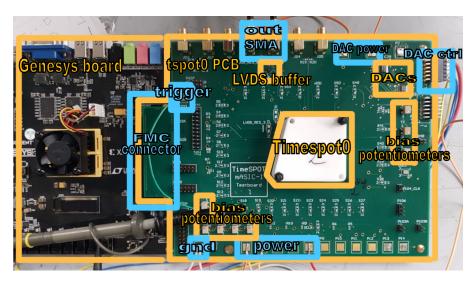

| 4.2        | Photograph of the tspot0-PCB                                              | 83  |

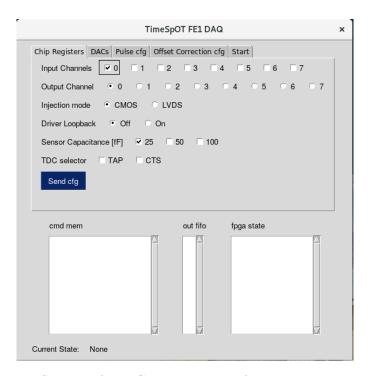

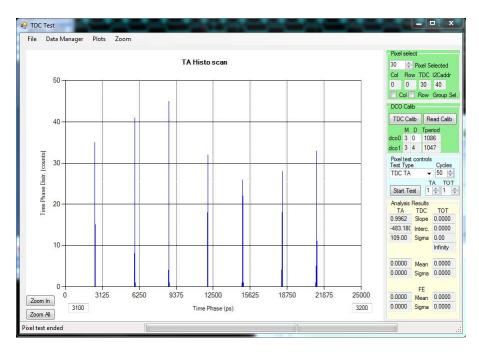

| 4.3        | Screen of the GUI developed for the Timespot0 DAQ                         | 84  |

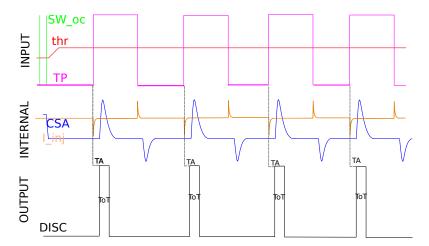

| 4.4        | Pulsing procedure used to test the Timespot0 AFE                          | 85  |

| 4.5        | Plot: Timespot0 AFE S-curves                                              | 87  |

| 4.6        | Plot: Timespot0 AFE Jitter and Slew-Rate                                  | 88  |

| 4.7        | Plot: Timespot0 AFE Threshold Scan Reconstruction                         | 86  |

| 4.8        | Plot: Timespot0 AFE Noise                                                 | 90  |

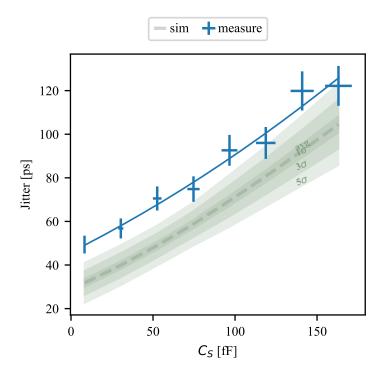

| 4.9        | Plot: Timespot0 AFE Jitter versus Sensor Capacitance                      | 91  |

|            |                                                                           | 92  |

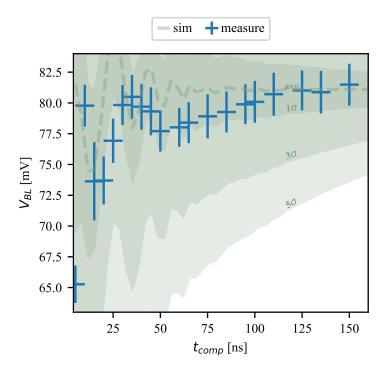

|            | Plot: Timespot0 AFE Baseline Setting Time                                 | 93  |

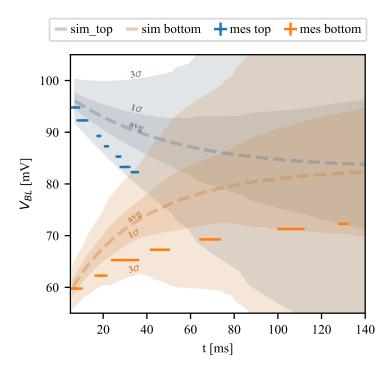

|            | Plot: Timespot0 AFE Baseline Drift                                        | 94  |

| 4.13       | Schematic of the experimental setup used for the Timespot0 AFE            |     |

|            | characterization.                                                         | 95  |

|            | DAQ Firmware Flow Chart.                                                  | 96  |

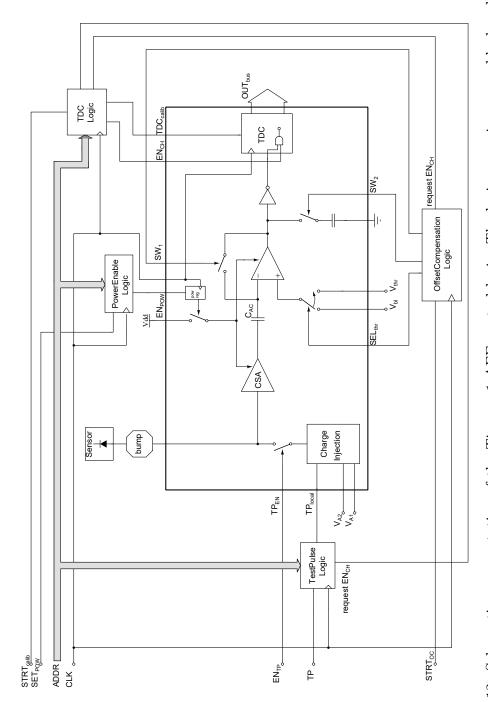

| 5.1        | Analog pixel architecture of the Timespot1 ASIC                           | 98  |

| 5.2        | Small signal equivalent circuit of the core amplifier of the Timespot1    |     |

| <b>.</b> . |                                                                           | 100 |

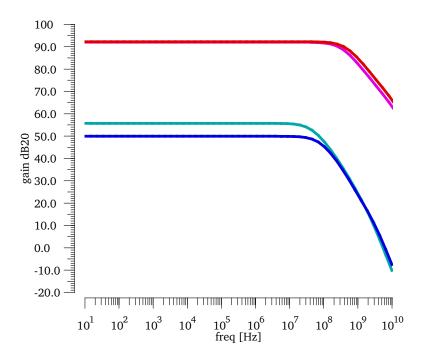

| 5.3        | Simulation: comparison of the frequency response between the single       |     |

| ٠.         | *                                                                         | .01 |

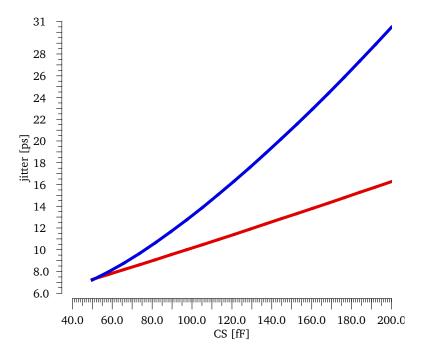

| 5.4        | Simulation: comparison of the output CSA jitter as function of the        |     |

|            | bias currents between Timespot1 and Timespot0                             | 0.3 |

| 5.5  | Simulation: comparison of the output CSA jitter as function of the                  |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | input capacitance between Timespot0 and Timespot1                                   | 104 |

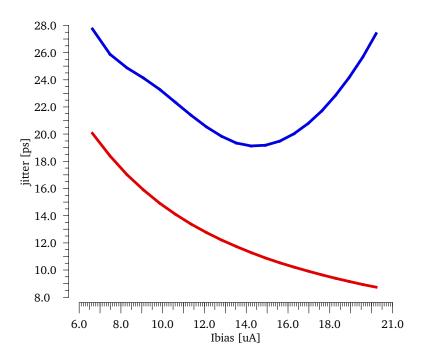

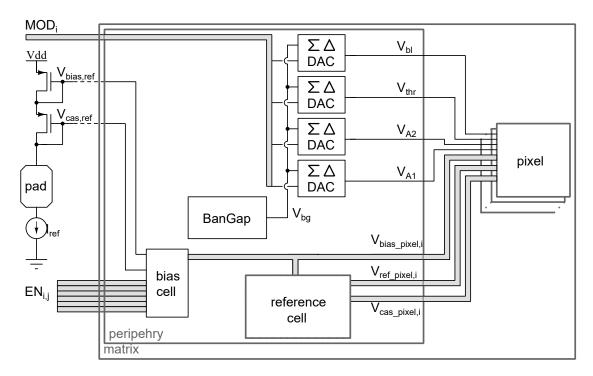

| 5.6  | Schematic representation of the Timespot1 analog periphery                          | 106 |

| 5.7  | Schematic representation of the Timespot1 bias-cell                                 | 107 |

| 5.8  | Analogy between the cascoded inverter and the telescopic cascode                    |     |

|      | amplifier                                                                           | 108 |

| 5.9  | Schematic representation of the Timespot1 reference-cell                            | 109 |

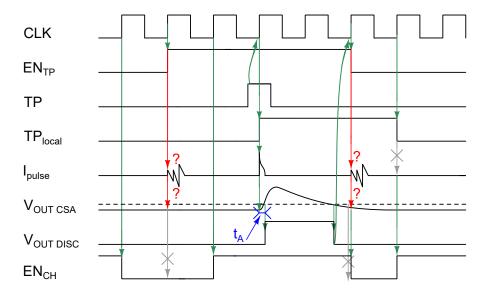

| 5.10 | Waveform representation of the offset compensation control logic                    | 110 |

| 5.11 | Waveform representation of the test pulse control logic                             | 111 |

| 5.12 | Schematic representation of the Timespo1 AFE control logic                          | 112 |

| 5.13 | Comparison between the Timespot0 and Timespo1 pixel electronics                     | 113 |

|      |                                                                                     | 115 |

| 5.15 | Transistor level schematic of the Timespot1 analog pixel electronics.               | 117 |

| 5.16 | Layout of the Timespot1 analog front-end core channel                               | 119 |

| 6.1  | Photograph of the experimental setup used to test Timespot1                         | 122 |

| 6.2  | TSPOT1 PCB                                                                          | 123 |

| 6.3  | Example of a screen of the DAQ software used to test the Timespot1                  |     |

|      | front-end                                                                           | 124 |

| 6.4  | Flow chart of the Timespot1 AFE characterization procedure                          | 125 |

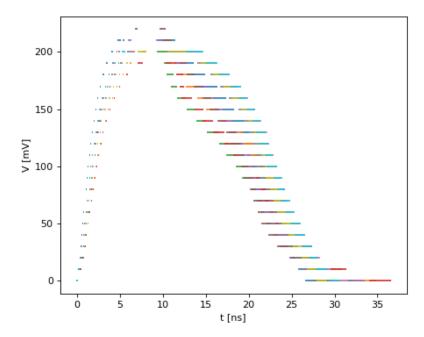

| 6.5  | Plot: threshold scan reconstruction of 32 Timespot1 channels                        | 126 |

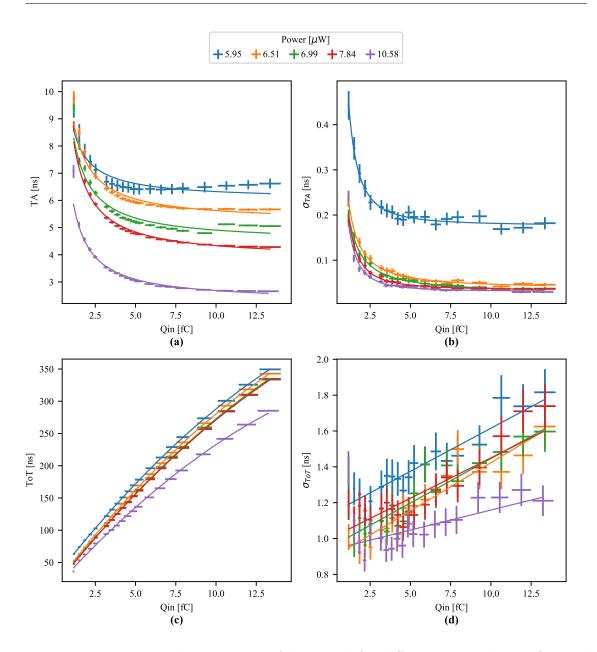

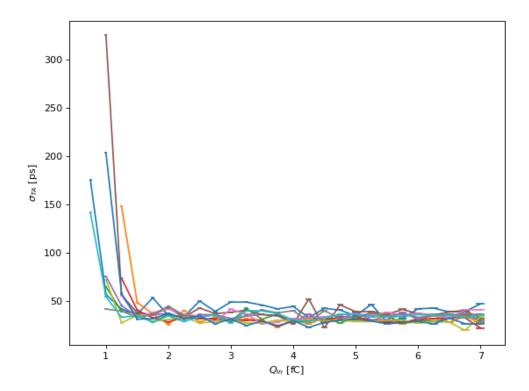

| 6.6  | Plot: $\sigma_{TA}$ charge scan of 32 Timespot1 channels                            | 127 |

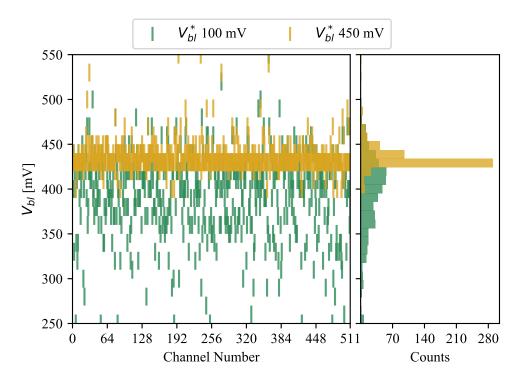

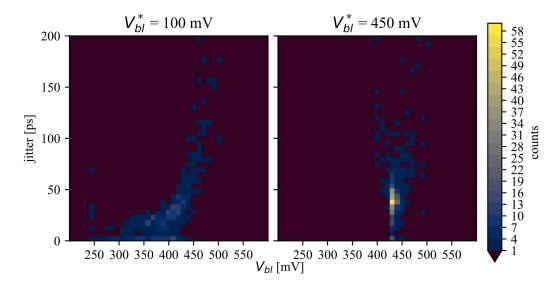

| 6.7  | Plot: Timespot1 AFE baseline distribution                                           | 129 |

| 6.8  | Plot: Timespot1 correlation of $\sigma_{AFE}$ to $V_{bl}$                           | 130 |

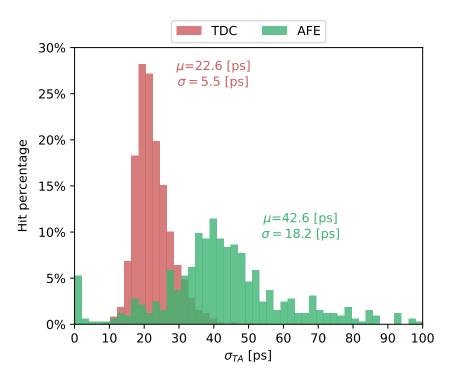

| 6.9  | Plot: $\sigma_{TA,AFE}$ histograms for the Timespot1 AFE and TDC                    | 131 |

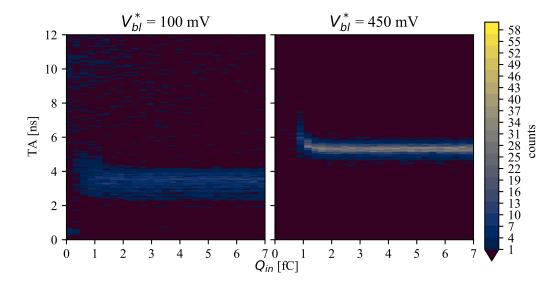

| 6.10 | Plot: TA values of the Timespot1 AFE as function of the input charge.               | 132 |

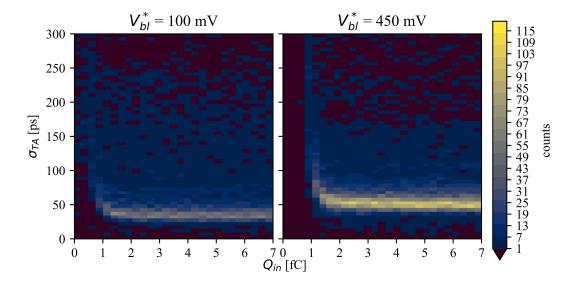

| 6.11 | Plot: $\sigma_{\text{TA,AFE}}$ values of the Timespot1 AFE as function of the input |     |

|      | charge                                                                              | 133 |

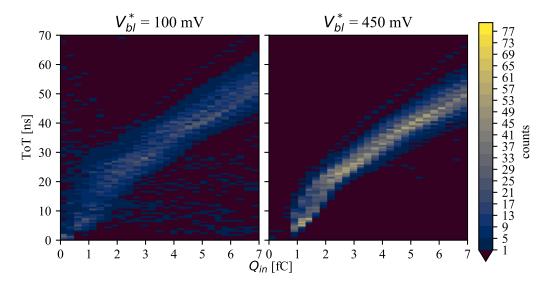

| 6.12 | Plot: $ToT_{AFE}$ values of the Timespot1 AFE as function of the input              |     |

|      |                                                                                     | 133 |

| 6.13 | Plot: $\sigma_{ToT}$ values of the Timespot1 AFE as function of the input           |     |

|      | charge                                                                              | 134 |

| 6.14 | Plot: TA versus ToT correlation for the Timespot1 AFE                               | 134 |

| 6.15 | Schematic of the experimental setup used for the Timespot1 AFE                      |     |

|      | characterization                                                                    | 135 |

| 6.16 | Timespot1 ASIC hybridized with the TimeSPOT 3D-Silicon sensor.                      | 137 |

| 6.17 | Purposed correction for the offset compensation circuit                             | 138 |

## Chapter 1

# Pixel Front-End ASICs with Timing

This chapter illustrates the state of the art in the field of pixel front-end ASIC with timing measurement capability. First of all, section 1.1 presents the state of the research in the field of timing measurement for HEP: starting from a discussion on the need to update the current detectors to include the time information, moving to the candidate sensors for this purpose and ending with a general presentation of the ASICs used in this field. Section 1.2 illustrates the general structures and concepts in common to the architectures of these type of ASICs. Section 1.3 will articulate on the goals and challenges of implementing the measurement of the time information in the pixel ASIC architecture. Finally, section 1.4 will present a review on the state of the art of the timing pixel front-end ASICs currently in development for HEP experiments.

#### 1.1 Overview

This section presents the field of application of timing pixel front-end ASICs for HEP. The first part will elaborate on the needing of the time information in HEP, whereas the second one presents the major candidate as pixel sensors for this purpose. The pixel sensor represents a key constraint in the design of a front-end ASIC.

The second part describes the historical process which has led to the development of pixel front-end ASICs, and their advantage compared to other solutions for radiation detection.

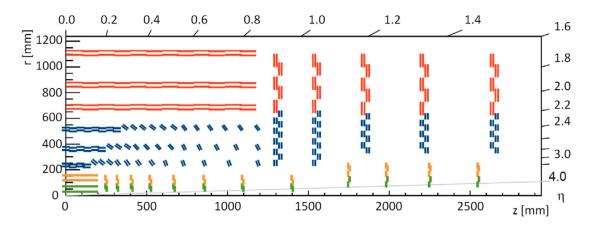

Figure 1.1: Layout of the new CMS Tracker. Taken from [25].

#### 1.1.1 Space-Time Measurements in High Energy Physics

The goal of HEP is investigating the fundamental working principles of matter by studying the properties of its constituents: the elementary particles. This goal is achieved by the observation of exotic states of matter produced through the interaction of common particles (such as protons or electrons) accelerated to speeds close to the one of light. The particles produced with this process are statically determined, wherein the interesting states of matter constitute a small fraction of rare events. In particle colliders two bunches of accelerated particles are crossed at a constant rate, the interaction point of this reaction is positioned inside a particle detector which detects the fragments and secondary products of the generated particle. The typical particle detector consists of different sensitive layers used to identify the particle position or energy. Particle momentum is then reconstructed by tracking the position of signals matching the same particle. The innermost layers of the detector are called tracker [41] and feature a high granularity space measurement. An example of a particle tracker is shown in figure 1.1. The outer layers are constituted of larger sensitive units with a more coarse space measurement, but with different measurement of other event properties (such as energy in calorimeters [28]).

In the Large Hadron Collider (LHC) at Conseil Européen pour la Recherche Nucléaire (CERN) bunches of  $10^5$  protons accelerated to 6.5 TeV are condensed to an interaction point of  $64\,\mu\mathrm{m}$  in size and crossed every 25 ns producing about 27 collisions each time. A key parameter in determining collision probability is the luminosity L (cm<sup>-2</sup>s<sup>-1</sup>), it expresses the probability of interaction per unit time, area and cross-section. In order to find more rare events in the same observation time, HEP experiments are planning to increase their nominal luminosity. In High-Luminosity LHC (HL-LHC) the nominal luminosity is planned to be increased from  $10^{34}\,\mathrm{cm^{-2}s^{-1}}$  to  $10^{35}\,\mathrm{cm^{-2}s^{-1}}$  [7] with an expected hit-rate per unit area of

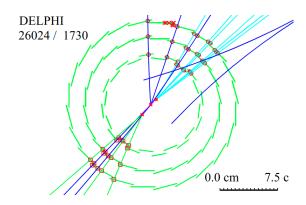

Figure 1.2: Example of particle tracking: a b-event with the DELPHI vertex detector. Taken from [41].

$3\,\mathrm{GHz\cdot cm^{-2}}$ . In this regime, the number of collisions per bunch crossing will increase to 200.

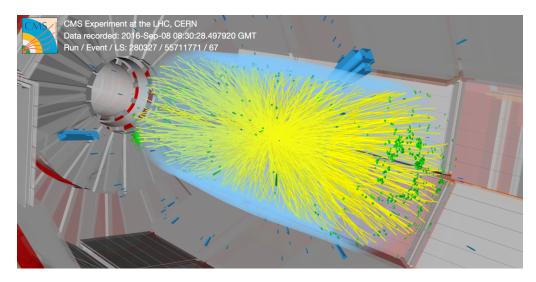

In this condition typical tracking techniques based on hit position will fail to reliably separate particles hitting the same area. An example of a reconstructed event is shown in figure 1.2. The tracking algorithms will occur in mainly two artifacts which will compromise the benefits of the luminosity increase: miss-tracks and ghost-tracks. Miss-tracks, as the name implies, are tracks which has been detected but were not recognized because they were overshadowed by the noise floor formed by the hits of other tracks. Ghost tracks, on the other hand, are fake tracks that the reconstruction algorithm improperly reconstruct from hits belonging to other tracks. An example of a high pileup event is shown in figure 1.3.

A possible solution to mitigate the pile-up problem is to supplement the position information with a high-resolution timing measurement [44]. The time information will not only provide a new dimension for implementing the track reconstruction algorithms, but it will also reduce the observation timeframe of the single snapshot of an event. The full evolution of the event will be observed, as opposed to be integrated over a large time. The advantages of the time measurement will start to become relevant for resolution better than 100 ps. The two candidate position inside the detector for the insertion of the timing measurement are the inner tracker or a single dedicated timing layer. The first case defines the 4D Tracking [76]: a high-granularity multilayer detector close to the interaction point (with a spatial resolution in the order of  $10\,\mu\text{m}$ ). The alternative solution is to insert an additional layer inside the particle detector specifically for the timing information [114]. The advantage of this last approach is connected to the fact that both the radiation hardness and the granularity of the detector can be reduced (with a spatial resolution in the order of 1 mm), prioritizing the time resolution.

The research activities in HEP are now focused on the development of this new generation of detectors from the point of view of the system, its sensors, and their

Figure 1.3: A high-pileup event with 86 reconstructed vertices observed by the CMS detector. Taken from [24].

read-out and front-end electronics. A front-end ASIC in this environment must reach the required time-resolution, and cope with the challenges related to the increased data-throughput and radiation hardness.

#### 1.1.2 Pixel Sensors with High Time Resolution

The first requirement to develop a timing pixel detector is the availability of a high resolution sensor. A general pixel sensor consists of reversed-biased semiconductor junction [66]. Inside the sensor volume, an electric field is formed. When a particle interacts with the semiconductor lattice, it looses some energy that locally produces free charge carriers. An electrical signal is induced by the migration of these free carriers towards the sensor electrodes. In the case of pixel-sensors, the typical geometry is planar: both the electrodes are realized on the surface of the material, with the active area between them. In terms of their coupling with the front-end electronics, two variations of pixel sensors exist: monolithic detectors [103] and hybris detectors. In monolithic detectors the sensitive area is created in the same substrate of the pixel electronics, with the two sharing the total surface. In hybrid pixel-detector the sensor and the electronics are implemented in two different chips, with different process, and then coupled together via bump bonding. The two chips must feature a bump-bond matrix with equivalent pitch.

In order to adapt the conventional technology to obtain a timing detector, the sensor design must be improved in terms of its signal variability. In particular, a timing signal must be reliable and stable. The signal must provide the event timing regardless of its other properties, like interaction position or deposited charge. The strength of the field, for example, influences the drifting velocity of the carriers

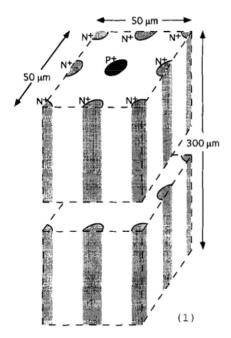

Figure 1.4: Concept of a 3D sensor. Taken from [81]

toward the electrodes. If the field is sufficiently low, the carrier will move by diffusion, which greatly increases their collection time. In a sensor in which the field is non-uniform, the arrival time of a signal is strongly related to the position of the interaction point. The condition of full depletion is the one that maximizes the field uniformity, therefore it is a characteristic necessary in timing sensors.

A sensor topology with promising timing properties is the so-called 3D sensor[81]. In 3D sensors the electrodes are built in vertical columns normal to the sensor surface. The electrodes and therefore the sensitive area, will extend deeply on the whole bulk of the material. A schematic representation of this sensor topology is shown in figure 1.4. The impinging particle will have a longer path to deposit the charge, as a consequence it will deposit more charge compared to a planar sensor with the same pitch. The reduced inter-electrodes distance will benefit the timing for different reasons: it will create a more uniform field, reduce the probability of delta rays <sup>1</sup> and reduce the variability of the drifting path of the carriers. The main draw back of this architecture is the larger capacitance between the electrodes. Both the signal strength and the sensor capacitance will affect the total system resolution because they influence the Signal to Noise Ratio (SNR) of the very front-end.

In this regard, another approach to increase the time resolution of the system

<sup>&</sup>lt;sup>1</sup>Secondary electrons produced inside the bulk that will interact with the sensor in a second moment, or escape from the sensor entirely.

is to increase the SNR of the signal through the insertion of a gain layer inside the sensor. This is the case of an Avalanche Photo Diode (APD)[45]. In this sensor the internal gain is provided by a multiplication of the electron number due to the avalanche effect. The reason behind the development of the APD was related to the necessity to increase the detection limit for low energy signal. Due to the multiplication, however, the APD features a large noise and leakage current. By creating a sensor with lower gain, a Low Gain Avalanche photo-Diode (LGAD)[71], these two drawbacks can be avoided. With an LGAD with a gain factor from 10 to 50 it is possible to improve the system SNR and therefore its time resolution. The main disadvantage of this approach is the presence of an additional variability source connected to the multiplication process.

One last approach is to leverage the intrinsic advantage of the monolithic sensor to obtain a high time resolution. Monolithic sensors can be suitable for timing since the absence of coupling reduces the sensor capacitance and allows producing these sensors with more aggressive pitch[54]. Moreover, advancements in their manufacturing process has opened the possibility to fully deplete them. The main disadvantage of this sensor is its relatively lower radiation-hardness.

#### 1.1.3 Pixel Front-End ASICs

Nowadays pixel front-end ASIC based detectors represent a fundamental instrument for key applications in radiation detection such as HEP, x-ray imaging, medical instruments and dosimetry. This kind of detector opens up the possibility to perform a spatially resolved measure by using a local micron-sized electronic chain. In particular, in HEP, pixel detectors have been developed and used since the beginning of the nineties [43].

The concept of an active pixel sensor comes as a natural evolution of the Charge-Coupled Device (CCD)[15] based sensor. In CCDs the charge deposited by an impinging particle is stored inside an array of MOS capacitors coupled together. The stored information can be read serially by transferring the charge from one pixel to the next, like in a shift-register. This is performed by acting on the common bias voltages. This configuration creates a limit for the maximum readout speed of a full matrix, making it impossible to observe events at a high rate which will be inevitably integrated by the CCD.

In order to overcame this limitation, the information needs to be processed locally and converted to a format more versatile from the point of view of data transmission. Therefore the basic pixel architecture must include at least the frontend electronics as well as a transmission interface. The development of such detector has become possible in the mid-eighties due to the advancement in the CMOS manufacturing process as well as the development of reliable techniques for sensor coupling via bump-bonding. From the point of view of the sensor, the timing was also ideal due to the maturity in the development of micro-strip sensors [4].

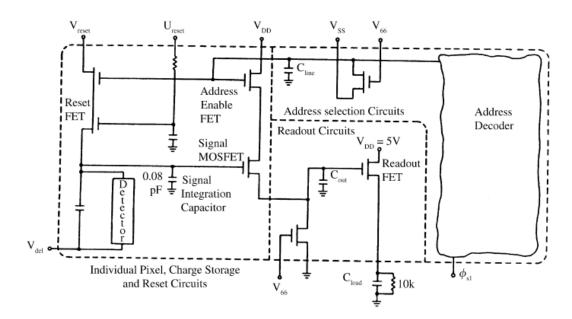

Figure 1.5: Pixel and readout architecture for the first ever pixel front-end ASIC: the readout chip for the focal plane imaging sensors developed at Hughes Aircraft Co. Taken from [34].

Micro-strips feature the desired topology of a planar sensitive area with micron-sized patterning. The sensitive area has its characteristic elongated aspect-ratio as a consequence of the need of realizing the wire-bond pads on the perimeter of the chip. Pixel sensors does not have this limitation and, moreover, the smaller size will grant a low leakage current which in turn will enhance the detector SNR. The bias voltage required to bias the sensor will also scale quadratically with the inter-electrode distance, enhancing the ease of use of the system. Moreover, another advantage of the pixel topology comes from the fact that performing imaging with strip sensors requires multiple parallel sensitive planes. The image reconstructed with coincidences of the hits on these planes will tend to become ambiguous in case of an excessive particle flow.

The first ever pixel front-end ASIC was developed in these times is the readout chip for the focal plane imaging sensors developed at Hughes Aircraft Coonment in 1984 [34]. The pixel and readout architecture of this chip is presented in figure 1.5. This ASIC was developed for x-ray imaging. The pixel architecture implements a binary front-end composed of only four transistors, it was directly connectable to the sensor via bump-bonding. The term binary front-end refers to the fact that the circuit is only capable to register the occurrence of an event, with no additional information. Each pixel integrates the signal into its capacitor whereas the interface is used to both transmit the state of the pixel and reset its stored information.

Following this chip, a research effort was carried out in the HEP field in order

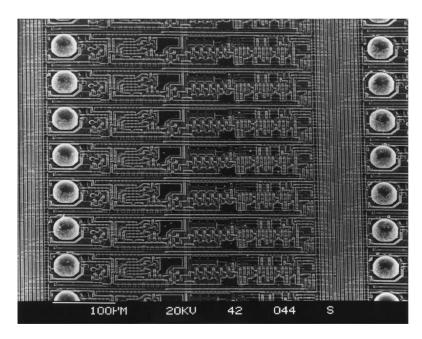

Figure 1.6: SEM image of the Omega2 chip. For reference, the bump-bond ball has a diameter of 38 µm. Taken from [43].

to develop a suitable pixel ASIC for the RD19 project[12]. This R&D produced the Omega ASIC family, with Omega2[22] being the first large-area pixel ASIC for HEP in 1994. The chip has been developed using a 3 µm Self Aligned CMOS technology. This ASIC was designed to cover an area of  $5 \,\mathrm{cm} \times 5 \,\mathrm{cm}$  with each chip having 1006 pixels of  $75 \,\mu\mathrm{m} \times 500 \,\mu\mathrm{m}$  organized in a matrix of  $64 \times 16$  pixels. A Scanning Electron Microscope (SEM) imagine of a set of Omega2 channels is shown in figure 1.6. The Omega front-end is binary with a continuous sensitive input amplifier and an asynchronous discriminator with a total power consumption of just 30 µW per channel. In this way the channel does not latch the information, but instead it registers it on a dedicated register which is read via an external trigger. The external trigger is provided as a per-column strobe signal. By synchronizing the delays of the strobe along the column, it is possible to read the column state with a 16 bits serial bus. The initial timing requirement in HEP was to be able to read the data inside a 25 ns period in order to assign the event to the correct LHC bunch crossing which is operated at 40 MHz. Table 1.1 shows a comparison between the ASICs operated in experiments in the first years of this field.

In the following years down to the present day, pixel ASICs have evolved iteratively by integrating more features both at pixel and chip level in order to achieve cutting-edge performances in radiation detection. The advancement on the sub-micron CMOS process has been critical for these progresses, enabling the integration of more features in the pixel area. The latest ASICs in the field are being developed in 65 nm and 28 nm. Front-ends can be realized in more complex

Comparison of pixel detectors operated in experiments

|                         | WA97/NA57 (RD19)               | DELPHI VFT  | NA50                |

|-------------------------|--------------------------------|-------------|---------------------|

| First year              | 1994                           | 1996        | 1997                |

| Last year used          | > 2000                         | 2000        | 1998                |

| # kpix                  | 1093                           | 1226        | 67                  |

| Area (cm <sup>2</sup> ) | 372                            | 1335        | 18                  |

| # Chips installed       | 792                            | 2432        | ~ 200               |

| # Readout wafers        | ~ 60 Ø 100 mm<br>~ 50 Ø 150 mm | nn Ø 100 mm | none<br>(From WA97) |

Table 1.1: Review table of the most important pixel front-end ASICs operated in the first years of LHC presented in [43]

architectures than the binary one in order to extract more information from the incoming particle, such as the deposited charge and the precise time of hit arrival. Thus, more information on the particle energy and momentum can be inferred, enhancing the overall quality of the event reconstruction. The measured value can be transmitted to a readout circuit in an analog format or directly digitized at the pixel level. Moreover, a local memory can be integrated inside the pixel, making the whole pixel matrix an event buffer. In this way the readout mode can divert from a trigger based one to the one most suited for the application. The active pixel can also process and filter the local signal in order to compress it or discard spurious events. In this way the readout circuit is offloaded of these tasks, enhancing the ASIC and thus the detector throughput. Finally, the ASIC can be made more flexible by integrating configurable circuits; and more autonomous by adding service blocks for local reference generation.

The next section illustrates various typical structures in pixel front-end ASICs that are commonly found in this type of chips.

#### 1.2 Architectures and Concepts

This section presents the architecture and concepts typical of a pixel front-end ASIC. The aspects outlined in this section are of a general nature, they represent practical implementations depending on the application. The general architecture will be firstly described starting from the electronics chain connecting the sensor to the ASIC output. After this, the section will describe the topological implication of implementing this chain in a pixel-matrix structure. The end of the section presents the measurable quantities and the data format and readout modes used to transfer the measured information outside the chip.

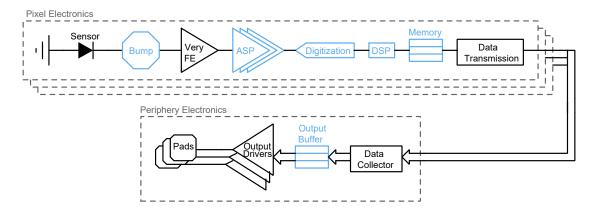

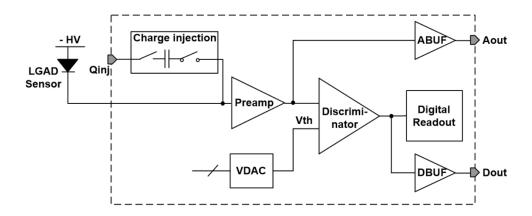

Figure 1.7: Schematic representation of the general electronics chain of a pixel front-end ASIC. The scheme follows the signal and data path. Optional blocks are drawn in light blue.

#### 1.2.1 The Electronics Chain

A pixel front-end ASIC solves basically two functions: processing at pixel level the signal coming from a sensor and transmitting the data generated from the pixel matrix to outside the chip. From the point of view of the signal and data path, the architecture consists of the following elements:

- 1. The Sensor: this is the area in which the sensor is realized in monolithic detectors. Depending on the technology, it can also be possible to integrate the front-end transistors inside this area.

- 2. The very front-end: it consists in the first stage of the electronics chain which is directly connected to the bump-bond pads in case of an hybrid detector, or more generally, to the sensor. It has the function of sensing the input signal and adapting it to the next stage.

- 3. An Analog signal processing block (optional): it is the set of analog stages which alter the signal to properly suit the measurement process. Some examples of possible stages can be a filter for noise reduction, a shaper stage or a simple discriminator used to produce binary signals. The discriminator also solves the function of rejecting uninteresting signals.

- 4. A Digitizer (optional): in this stage the signal is converted to the digital domain. This stage is present whenever the readout interface is digital. In case of binary front-ends it can consist of a simple buffer or latch, but in case of more complex architectures it can include converters such as an Analog to Digital Converter (ADC) for amplitude measurements or a Time to Digital Converter (TDC) for direct time measurement. Ideally, it is also possible to insert a full signal sampler at this stage.

- 5. A Digital Signal Processing (DSP) (optional) block: it can be used as in point 3 to modify the signal properties depending on the needs. For example, it can be used to enhance the signal SNR, filter spurious events or compress the data. Performing these operations locally can increase the data throughput and offload the subsequent data processors of some tasks.

- 6. A local memory (optional): it can be used to store locally the data produced by the front-end. This can consists in a single event memory for a basic trigger-based readout. The depth of this memory is greatly constrained by the available space on the pixel area. Usually at least a simple buffer memory is required due to bandwidth bottlenecks on the data transmission interface.

- 7. The local data transmission interface: this block includes all the circuits which operate the data transmission from the pixel to the rest of the chip. It can consist of a serializer or deserializer if the data are stored in a digital format, or a form of line driver in case of analog data. In any case, it must provide a form of address identification and, in case of shared busses, a method for arbitration. This stage can also implement additional features such as zero suppression, signaling the presence of event pile-up or referring the data to a specific time reference.

- 8. The data collection interface: this block collects the data from many pixels in order to distribute them to the output buffers. The data words coming from this stage must include a geographical address and an eventual time reference. Both these functions must be provided by this block. If the transmission data bandwidth is insufficient, a de-randomization step is required. This can be implemented, for example, with a simple First In First Out (FIFO) stage.

- 9. An output buffer (optional): the data formatted by the collector can be stored in this memory. This stage is necessary in cases in which the output driver bandwidth is insufficient. Again, if an arbitration of the output resources is required, a de-randomization step must also be inserted.

- 10. The output transmission drivers: these are the transmitters responsible for outputting the data generated by the whole ASIC. The driver must sustain the target analog bandwidth while driving the external impedance. Their number is usually limited by the pads availability or the power consumption budget. Output drivers can be realized according to various standards such as: full CMOS signaling, Low-Voltage Differential Signaling (LVDS), Scalable Low-Voltage Signaling (SLVS), Current Mode Logic (CML), etc.

A schematic representation of this electronics chain is presented in figure 1.7.

#### 1.2.2 Topology

From a topological point of view, these blocks must be organized to accommodate the data flow from the matrix configuration of the sensor to the output drivers. It is evident that every circuit described from point 1 to 7 must be implemented locally, near the sensor or bump-pad; whereas the others are bounded to be integrated in proximity of the output connections.

Typically, the output drivers are connected to the outside of the chip via wire-bonding. Wire-bond pads are usually realized on the perimeter of the chip, and in some cases, they can be realized in multiple parallel lines. The number of parallel lines is limited by the difficulty to connect the wire-bonds to the innermost pads. Moreover, in the case of a hybrid detector, the chip top surface is already occupied by the bump-bond pads. For these reasons, it is usually practical to create at most two parallel lines of staggered pads. Redistributing the data in such configuration means interfacing a planar topology to a linear one. This creates an intrinsic problem in the ASIC floor-plan: the number of pixels will scale quadratically with the chip size, whereas the number of output drivers will scale linearly. As a consequence, large-area ASICs will suffer from a congestion in data lines and a bottleneck in the data redistribution bandwidth.

Moreover, the pixel matrix area must accommodate not only the pixels own electronics but also the data lines. If the data lines consist of per-pixel dedicated buses, the congestion will grow from the innermost pixel to the external ones. This problem can be circumvented by having a common bus or a daisy-chain connection between the channels. The first solution will, however, increase the data transmission latency requiring more bits to refer the event to the correct reference period (time-stamping), thus reducing the overall maximum processable event rate. In the same way, the second solution will require some form of arbitration which will increase again the average latency and reduces the data bandwidth to the one of the shared bus.

The floor-plan must also accommodate for redistribution of the power net, the ground net and all the reference signals used to operate the individual pixels. These references can be analog voltage levels and current biases or digital configurations, clock nets and dynamic digital signals (e.g. a trigger). The path of these nets will follow inversely the data path, encountering the same geometrical problems and bottlenecks. Therefore, large-area pixel ASICs shows a challenging power distribution. Additionally, the majority of these references can be generated inside the chip using dedicated blocks. For instance, the analog voltages and currents can be provided by integrating a dedicated Digital to Analog Converter (DAC) coupled with a Band-gap, while the reference clock can be generated internally and phased with an input one using a Phased Locked Loop (PLL). The area not dedicated to the pixel must also accommodate the necessary configuration registers.

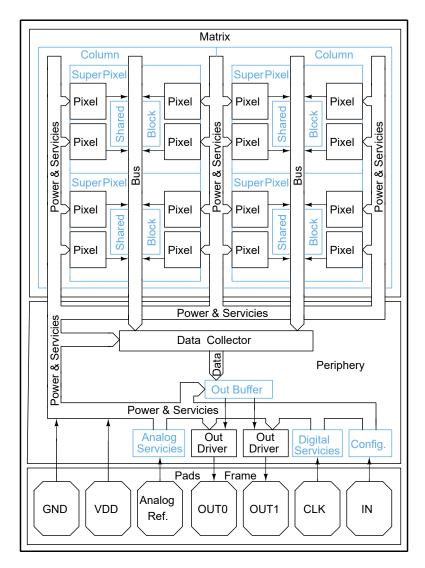

By taking into account the aforementioned considerations, the general topology

Figure 1.8: Example of a possible floor-plan of a pixel front-end ASIC. The scheme is not in scale. In this example the pixel matrix is composed of  $4\times4$  pixels grouped together in two double-columns of  $2\times4$  pixels, every  $2\times2$  pixels shares part of their electronics in a super-pixel. Optional blocks are drawn in light blue.

of a pixel ASIC with IO and power connection realized with wire bonding consists of the points below. The structures are ordered in a bottom-up order from the pixel to the chip.

1. Pixel: the individual repeated unit connected to the sensor. Each pixel can include all the circuits described in the previous list from point 1 to 7 and some local services. Some examples of local services can be: local configurations or per-pixel calibration circuits.

- 2. Super-pixel (optional): a set of pixels sharing part of their electronics. Sharing electronics enables to save chip area and power at the cost of the arbitration of these resources.

- 3. Column or row (optional): a repeated structure of pixels comprising their transmission lines as well as the reference and power redistribution. They usually identify a subset of geographical addresses. The column or row name is conventional and interchangeable: the name comes from the convenience of building them in a straight path. Often a double column configuration is preferred since it enables to integrate the data and power paths in a shared area.

- 4. Matrix: the whole set of pixels with their interfaces.

- 5. Periphery: the set of circuits connected to the matrix which are used for IO purposes, configuration and services. Its portion directly connected to the columns is often called End of Column (EoC). The number of these units does not scale with the number of pixels.

It must be noted that inside a single ASIC both the matrix and the periphery can be subdivided into some repeated blocks, making them appear as sub-matrices from the rest of the system.

Most of the topological problems described above can be avoided by realizing the IO and power interconnection leveraging the whole ASIC area. Using Through Silicon Via (TSV)[75], for instance, it is possible to create a dense pattern of vertical interconnections from the chip bottom face down to the device level. In this way, the ASIC can be connected with a matrix of bump-bonds to the sensor and with a matrix of TSVs to the carrier board. Moreover, with 3D integration, it is theoretically possible to cover a large area by tiling together multiple chips without dead-area. Without the need of redistributing the nets to the perimeter of the chip, it is ideally possible to create a periphery-less ASIC in which all the IO and service blocks will be integrated seamlessly inside the pixel matrix.

## 1.2.3 Readout Modes, Measurable Quantities and Data Formats

The pixel ASIC can be seen as a data source with a specific mode and protocol. In each possible implementation of the protocol, the possibility that a hit arrives when the dedicated memory is full must be foreseen. Some measures are thus applied to address the data-loss: the new event can be ignored or one of the stored data can be overwritten. Additionally, a pile-up flag can be raised for signaling the occurrence of this event. Three major categories of readout modes can be identified:

- Frame based: the state of the ASIC is continuously readout for the entire matrix. A frame is a single snapshot of the entire matrix. The refresh-rate identifies the rate at which a full frame can be acquired. This readout mode requires a straightforward readout electronics and is suitable for applications in which the available memory is sufficient to buffer all the hits arriving during the refresh period.

- Trigger based: the data is stored inside the ASIC waiting to be readout. An external trigger signal initiates the acquisition of the stored data for the entire matrix or a subset of it. The maximum sustainable per-pixel hit-rate is limited by the time required to read the full trigger set. Therefore, a trigger based readout is not suitable for an application which involves a constant monitoring of a high hit-rate system. The main advantage of this mode is the possibility to discard spurious events a-priori, without overloading the following readout by leveraging the trigger system.

- Data driven: individual pixel data are continuously transmitted off-chip as they are produced. As described in the previous section, it is unrealistic to expect a per-pixel transmission line with sufficient bandwidth to serve the full matrix. For this reason, this type of system has heterogeneous transmission lines which involve arbitration and de-randomization. The readout of this type of ASIC tends to be more complicated compared to the previous ones, but offers the most flexible solution. This readout-mode is most suited for sparse events with unpredictable or uneven space and time phases.

The relation between the impinging particle properties and the measurable quantities is strongly related to the operating principles of the sensor. As explained in section 1.1.2, the typical sensor response is a current signal induced by the drift of the charges deposited by a particle from the deposition point to the sensor electrodes. More specifically, the particle deposits the charge in multiple points along its tracks. The deposited charge, and therefore the integral of the current signal, is proportional to the kinetic energy lost by the particle during the interaction. Even though the charge represents the primary information, additional information on the particle-sensor interaction can be derived from the time development of the signal. In any case, the pixel structure will naturally provide the spatial information by the means of the centroid of the activated pixels. From the point of view of the pixel electronics the measured quantities can be classified as:

Particle passage: the occurrence of an event during a time period. This

quantity represents the most basic information on the interaction and can be

provided by a simple binary front-end. It must be noted that even in the

most simple front-end, a discrimination process will take place; otherwise the

front-end be triggered inevitably by noise. As an indirect effect of the noise

discrimination, the front-end will still produce an indication that the signal amplitude exceeds a certain amplitude. Moreover, by integrating a local counter, the number of occurrences on a certain time frame can be provided.

Charge: the deposited charge can be retrieved by integrating the whole signal. This can be done simply using a capacitor or an active Charge Sensitive Amplifier (CSA) stage. The integrated amplitude can be digitized by with a local ADC. The digitization process must be triggered after the full integration time. In systems featuring a discrete-time discharge it is trivial to implement this trigger. To clarify, a discrete-time discharge front-end is typically implemented with a discharge switch is parallel to the integrating capacitor, the switch is toggled periodically in order to transit from an infinite resistance loop (integration) to a zero resistance one (discharge).

A smart solution for charge measurement is to leverage a TDC to perform it. In particular this can be done in systems in which there is a monotonic and reliable relation between the integrated amplitude and the signal time development. The simplest example is the case of a CSA with constant current discharge. If the input signal time development is shorter than the CSA integration time, the total signal length is proportional to its amplitude and therefore to the input charge. By using a discriminator with a programmable threshold it is possible to produce a digital pules with a certain Time over Threshold (ToT). By digitizing it, the charge information can be acquired.

• Time: this measurement can be performed by directly measuring the timing characteristics of the very-front signal after a discrimination process. The key parameter is represented by the Time of Arrival (TA) of the signal, which is the measure of the elapsed time between the event to be measured and a reference signal. Typically the rising or falling edge of these two signals is used to initiate and end the measurement. Another parameter is the ToT.

The analog front-end has only the function of providing the signal to be digitized. If it is implemented with a Trans Impedance Amplifier (TIA) with sufficient bandwidth, the timing characteristics of the signal will remain unchanged. However, if a form of integration takes place the TA will depend on the input charge. The limit case is represented by the CSA in which the rising time is independent from the signal charge, whereas the slew-rate and therefore the TA will depend inversely on the input charge. This phenomenon is named time walk: the drifting of the TA measurement as the charge decreases. The time-walk represents a systematic effect which can be corrected by knowing the input charge. A convenient time-walk correction method can be based on the ToT. An alternative solution to the time-walk correction is to utilize Constant Fraction Discriminator (CFD)[35][68] combined with a CSA which automatically moves the threshold in order to contrast the time walk.

The digitization is carried out using a TDC which can be implemented in various architectures. The most basic TDC can be implemented by counting the number of oscillations of a local Voltage Controlled Oscillator (VCO)[113] or Digital Controlled Oscillator (DCO)[84], which are elapsed during the time to be measured. Higher resolutions can be obtained by using a delay chain with the purpose of registering its state at the end of the measuring process. In this way the resolution limit is determined by the delay of a single element. This last configuration can be looped in a Delay Locked Loop (DLL) combining both of the two aforementioned methods [84]. Furthermore, using a Vernier configuration, two parallel lines of this kind can be used to encode the information on the phase difference between them[21][52]. A time amplification technique can also be used to increase the time to be measured [72][73], which is then digitized using one of the previous architectures. Another completely different solution is the pulse-shrink architecture [20][47]: the input pulse is iteratively shirked until it surpass the detection limit; the number of iterations provides the measurement. Finally, the timing characteristic of a signal can be directly converted to an analog amplitude using a Time to Voltage Converter (TVC) [79], and then digitized with an ADC.

- Amplitude: this parameter can be measured at the output of the pre-amplifier. In the case of a TIA, the relation between its output voltage and the input current amplitude is linear and well known. The digitizer (e.g. an ADC) must sample the signal at the correct point of its development, therefore the frontend must also provide a signal that triggers the digitization. For example, the peak of a signal can be triggered using a differentiator stage in parallel to the main channel. Similarly, a CFD can trigger the digitization of a certain relative threshold.

- Full signal development: the full signal can be recorded using a Sample and Hold (S/H) process. This measurement is the most power and area consuming. Since it samples the signal it produces a really flexible information at the cost of a higher bit length per event. Moreover, it requires a S/H implementation with a sample rate adequate to measure the signal. For these reasons, it is often unfeasible to insert a full S/H circuit in a pixel front-end for HEP.

The typical data format of a word produced by a pixel front-end ASIC with digital readout is composed of:

- Measurement: the output bits of the digitizer corresponding to the measured quantity described in the previous paragraph.

- Address: an index or couple of indices that identify the pixel position.

- Time-stamp: an identifier, usually an integer, which correlates each measurement with the reference clock period in which the measurement took place. This procedure constitutes a form of coarse time measurement. Time-stamping may be required in cases in which the data cannot be readout within the period of the reference clock.

- Additional information: additional bits are often reserved for some utilities.

For example, these bits can be used for the signaling of a pileup event, as described above.

#### 1.3 Pixels with Timing

This section explains the research challenges concerning the addition of a high resolution time measurement to a typical pixel detector. The topic will be introduced by analyzing the general components which affect the time resolution in this type of detector. After this, the section will discuss the challenges of implementing a high time resolution electronics in the specific case of a pixel front-end ASIC.

#### 1.3.1 Resolution Contributions

The resolution of a timing system can be quantified with the standard deviation of a set of repeated measurements of different events occurring at the same time. Therefore the timing system must be insensitive to the other properties of the event such as its charge. Using the probabilistic definition of standard deviation and imposing the average value equal to zero, the timing resolution becomes:

$$\sigma_{t,res} = \sqrt{\int_{-\infty}^{+\infty} P(t)t^2 dt}$$

(1.1)

where P(t) is the Probabilty Density Function (PDF) of the measured time t.

The most general system is composed of a sensor, a very front-end and a digitizer (see 1.2.1). This kind of system is able to produce a digital code corresponding to the time of arrival of a certain event. As explained earlier, the function of the very front-end is to adapt the sensor signal to the digitizer input. Considering these contributions to be independent one from the other, the resolution can be expressed as:

$$\sigma_{t,res} = \sqrt{\sigma_{t,sens}^2 + \sigma_{t,ana}^2 + \sigma_{t,digi}^2 + \sigma_{t,corr}^2}$$

(1.2)

where  $\sigma_{t,sens}$  is the sensor intrinsic contribution of the total resolution,  $\sigma_{t,ana}$  is the contribution from the very front-end and  $\sigma_{t,digi}$  is the contribution from the digitization process.

The last term,  $\sigma_{t,corr}$ , represents the error related to an eventual digital correction of systematic effects. This is not part of the core time measurement process, but it is able to enhance the overall measurement resolution. The tradeoff of correcting a measurement is connected to the error generated from this operation.

Additionally, by multi-sampling the same event, the resolution can be further enhanced. In particular, all the random contributions non-related to the sensor variations  $(\sigma_{t,ran})$  can be reduced with the square root of the number of samples  $N_s$ :

$$\sigma_{t,res} = \sqrt{\sigma_{t,sens}^2 + \frac{\sigma_{t,ran}^2}{N_s} + \sigma_{t,sys}^2}$$

(1.3)

Where  $\sigma_{t,sys}$  are all the systematic contribution to the time variation. Again in this case, the systematic component can be eliminated using a digital correction:

$$\sigma_{t,res} = \sqrt{\sigma_{t,sens}^2 + \frac{\sigma_{t,ran}^2}{N_s} + \sigma_{t,corr}^2}$$

(1.4)

All the components will be now analyzed one by one.

#### Sensor contribution

The sensor current signal can both vary in its total charge and in its time development. To be accurate, the whole signal shape will inevitably affect its timing. It is convenient to disentangle the two components since the sensor acts as transducer for the energy lost by the particle in the interaction to a charge. Therefore  $\sigma_{t,sens}$  accounts for all the non charge related signal variations. The major time variability source is related to the geometrical non-uniformity of its field. This component is in principle independent of the impinging particle charge, and it is related only to the interaction position and angle of incidence. Therefore it can be assumed as timing variability on the charge generation  $\sigma_{t,gen}$ . Another component can be introduced by an eventual gain layer  $\sigma_{t,gain}$ , and it is connected to the characteristic time of the process. In any case the two components can be assumed to be independent, resulting in a total sensor contribution expressed as:

$$\sigma_{t,sens} = \sqrt{\sigma_{t,qen}^2 + \sigma_{t,qain}^2} \tag{1.5}$$

The distribution of the first term is complex and it depends on the detector and sensor geometries, whereas the second one typically follows a Landau distribution.

The other source of variability is the quantity of charge deposited by the particle  $q_i$ . This quantity will vary with a certain PDF  $P_{dep}(q_i)$  which is directly connected to the radiation-matter interaction.  $P_{dep}(q_i)$  can be assumed to be a Landau distribution. Even though this component will not affect the intrinsic timing properties of the sensor ad its signal, it will in turn influence the response of the very front-end.

#### Very front-end contribution

The very front-end response to the input signal can be generally expressed as a function of the sensor current signal  $i_i(t)$ . For the purpose of describing only the very front-end contribution to the total timing the charge development is considered to be instant, and therefore the input signal will be represented with a delta-like pulse with a certain charge:

$$i_i(t) = \delta(t)q_i \tag{1.6}$$

Where  $q_i$  is the total deposited charge. The front-end output  $t_{ana}$  will be a time value representing the arrival time of the input signal. Its operation can be generally represented as:

$$t_{ana} = T_{q \to t}(q_i) + \chi_{jit}(q_i) \tag{1.7}$$

where  $T_{q\to t}$  is the charge to time transfer function of the analog processor and  $\chi_{jit}(q_i)$  is a stochastic term representing the output jitter contribution added by the circuit intrinsic noise. The decision to represent this stage as a charge dependent one is not related to the very front-end own architecture, but again only a mean of separating the input variations from the ones introduced by this stage. In this regard,  $T_{q\to t}$  can assume any kind of non-linear form. Going into detail, a timing very front-end will convert through a two stage process: firstly it will convert the signal into an analog amplitude signal  $a_o(t)$  (namely a current or a voltage) and then it will convert it to a digital pulse with a well-defined transition. In this way  $T_{q\to t}$  can be decomposed as the convolution of the two transfer functions:

$$a_o(t) = T_{q \to a}(\delta(t)q_i) \tag{1.8}$$

$$t_o = T_{a \to t}(a_i(t)) \tag{1.9}$$

$$t_o = T_{q \to t}(q_i) = [T_{a \to t} * T_{q \to a}](q_i)$$

(1.10)

$a_o(t)$  is the time development of the front-end output signal and  $T_{q\to a}$  is the transfer function which relates it to the input charge development.  $t_o$  is the output timing signal and  $T_{a\to t}$  represents the discrimination process. It is safe to assume that  $T_{q\to a}$  is monotonically increasing and  $T_{a\to t}$  is monotonic decreasing.

As a result, the first term of (1.7) will generally produce a time-walk effect. The most probable value of the output time  $\hat{t}_{ana}$  can be computed on the basis of  $P_{dep}(q_i)$ :

$$\hat{t}_{ana} = \int_0^{+\infty} P_{dep}(q_i) \cdot T_{q \to t}(q_i) \, dq_i \tag{1.11}$$

This value is computed in the whole charge range, even though  $P_{dep}(q_i)$  is non-zero only in a limited range. Likewise, the standard deviation of this parameter is computed as:

$$\sigma_{tw} = \sqrt{\int_0^{+\infty} P_{dep}(q_i) \cdot (T_{q \to t}(q_i) - \hat{t}_{ana})^2 dq_i}$$

(1.12)

This term can be interpreted as the time-walk dependent component of the analog electronics time variation. In general the PDF resulting from this conversion  $P_{tw}(t)$  is a transformation of a random variable [101] from the charge to a time:

$$P_{tw}(t) = P_{dep}(T_{q \to t}^{-1}(t)) \cdot \left| \frac{d}{dt} T_{q \to t}^{-1}(t) \right|$$

(1.13)

Therefore it has a shape related to  $P_{dep}(q_i)$ .

Moving to the front-end intrinsic jitter, it can be usually expressed as:

$$P_{iit}(t|q_i) = \phi(t|\sigma_{fe}(q_i)) \tag{1.14}$$

where  $\phi(t|\sigma_{fe}(q_i))$  is a zero centered Gaussian PDF defined as follows:

$$\phi(x|\mu,\sigma) = \frac{e^{-\frac{x^2}{2\sigma^2}}}{\sqrt{2\pi\sigma^2}}$$

(1.15)

This distribution is related to the PDF of the electronics intrinsic noise, in which the main contributor is the thermal noise [50]. This component can be altered by the presence of other noise components (such as 1/f) or by the presence of noise filtering stages. The standard deviation of the distribution can be generally connected to the stage output noise as  $\sigma_{na}$ :

$$\sigma_{fe}(q_i) = \frac{\sigma_{na}}{a_o'(q_i)} \tag{1.16}$$

In which  $T'_{q\to a}(q_i)$  is the derivative of the charge to amplitude transfer function at the sampling point:

$$a'_o(q_i) = \frac{d}{dt}[a_o(t)] = \frac{d}{dt}[T_{q\to a}(\delta(t)q_i)]$$

(1.17)

The amplitude noise is converted to a time one by the means of amplitude signal transient  $a'_o(q_i)$  (namely its slew-rate) which connects the magnitude of this variation to the input charge. Since the resulting distributions will be all centered in zero, the standard deviation of the jitter across the whole input range can be computed as:

$$\sigma_{jit}(t) = \sqrt{\int_0^{+\infty} \sigma_{fe}^2(q_i) P_{dep}(q_i) dq_i}$$

(1.18)

In order to compute the total PDF of the two components, it is helpful to write  $\sigma_{fe}$  as a function of the output time using  $T_{q\to t}(q_i)$ :

$$\sigma_{fe}(t_0) = \frac{\sigma_{na}}{T'_{q \to a}(T_{q \to t}^{-1}(t))}$$

(1.19)

Using this expression in (1.14) in combination with (1.13), the total PDF  $P_{t,ana}(t)$  can be computed with:

$$P_{t,ana}(t) = \int P_{jit}(t - t_0 | \sigma_{fe}(t_0)) \cdot P_{tw}(t_0) dt_0$$

(1.20)

The resulting distribution is an interplay of the two contributions, in which the total standard deviation can be computed using the general relation:

$$\sigma_{t,ana} = \sqrt{\int_{-\infty}^{+\infty} P_{t,ana}(t) \cdot (t - \hat{t}_{ana})^2 dt}$$

(1.21)

It can be easily verified that:

$$\sigma_{na} \to 0 \Rightarrow \sigma_{t,ana} \to \sigma_{tw}$$

(1.22)

$$\sigma_{tw} \to 0 \Rightarrow \sigma_{t,ana} \to \sigma_{jit}$$

(1.23)

The first case represents a very front-end with no intrinsic noise, whereas the second represents a very front-end with no time-walk. The second case can actually be found in a system in which the time-walk is actively compensated with a discrimination process insensitive to the time-walk (for example with a CFD). In those cases  $T_{q\to a}$  and  $T_{a\to t}$  contrasts each other cancelling their respective distributions.

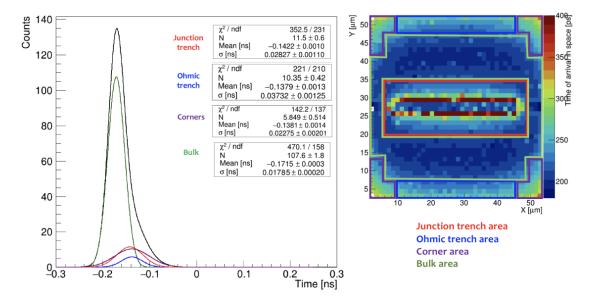

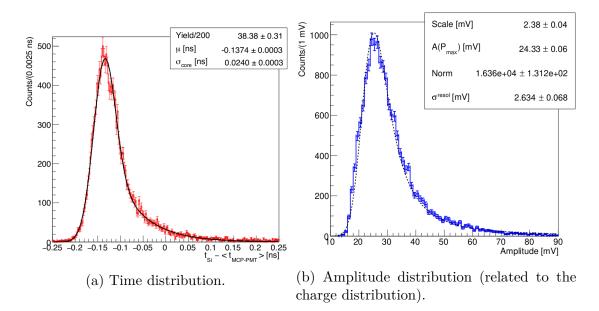

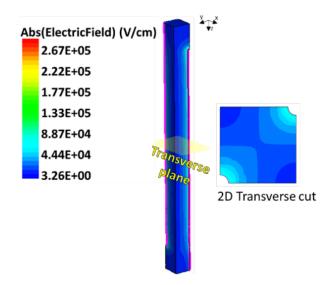

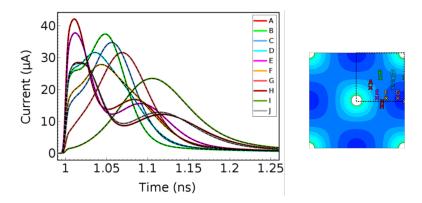

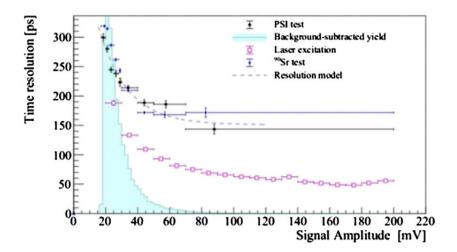

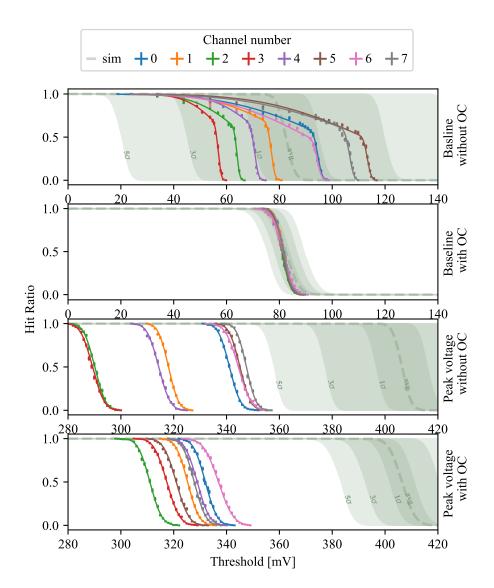

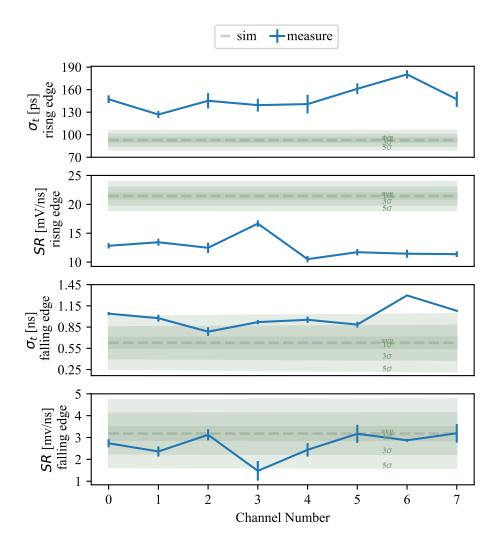

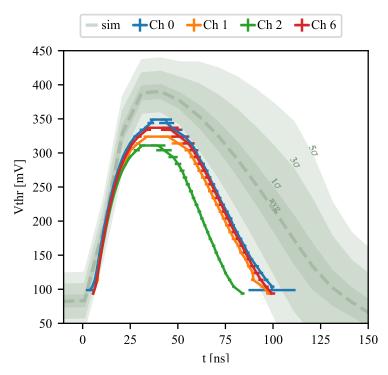

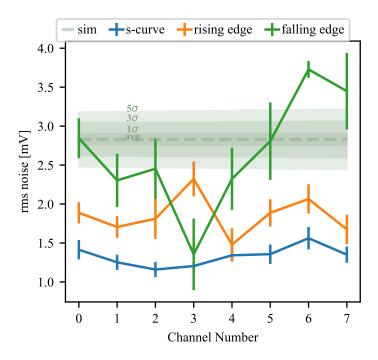

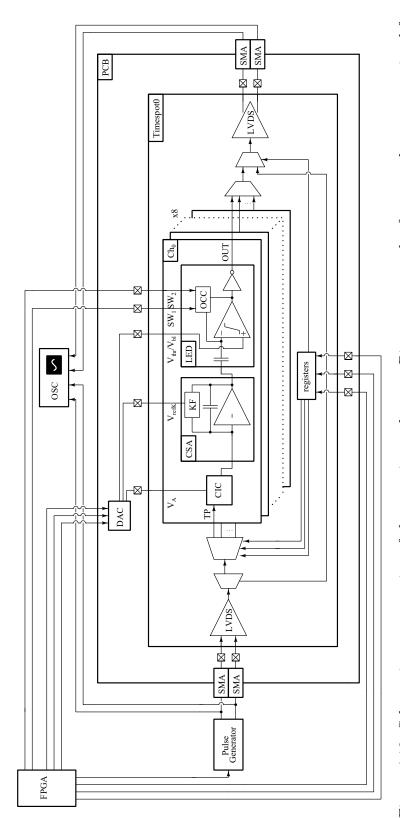

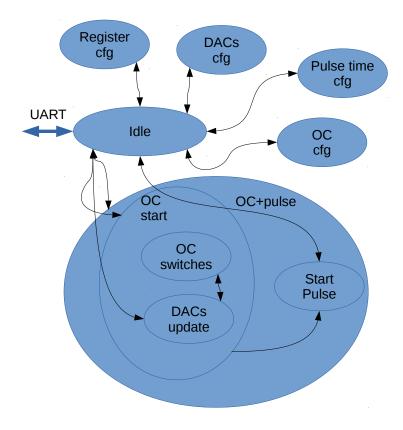

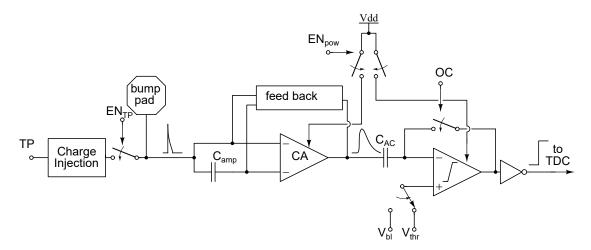

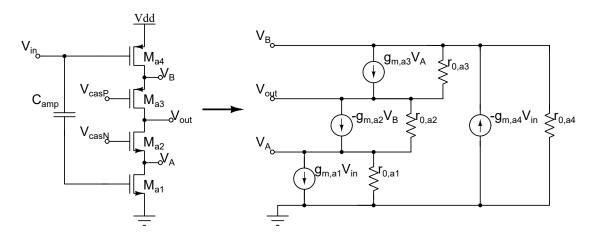

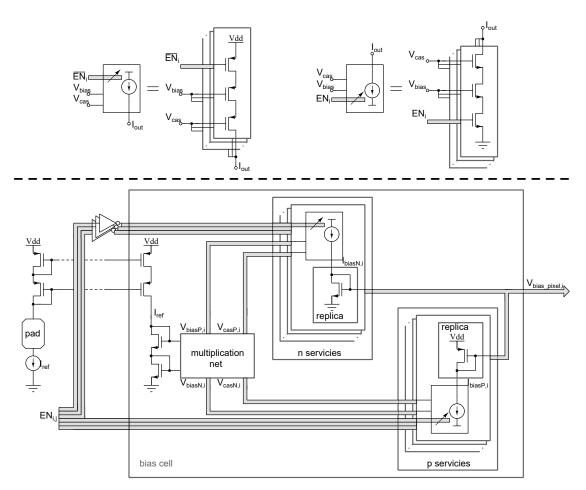

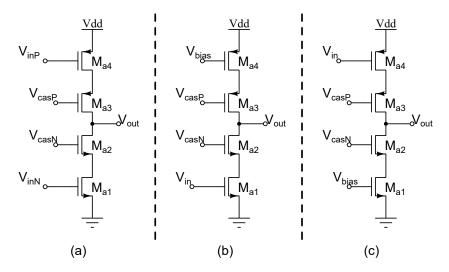

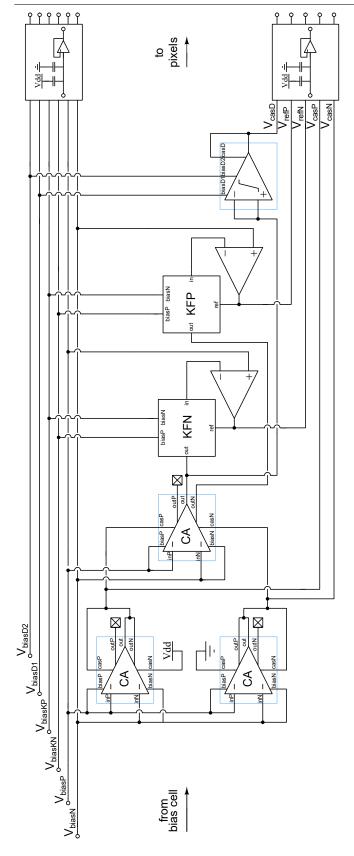

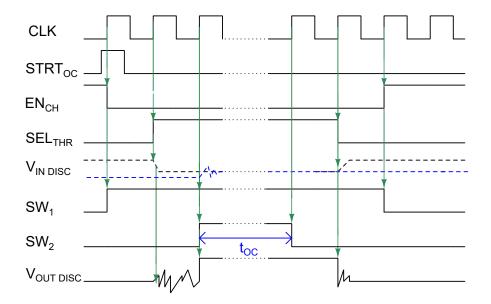

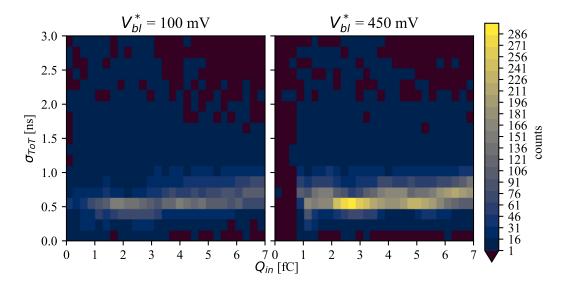

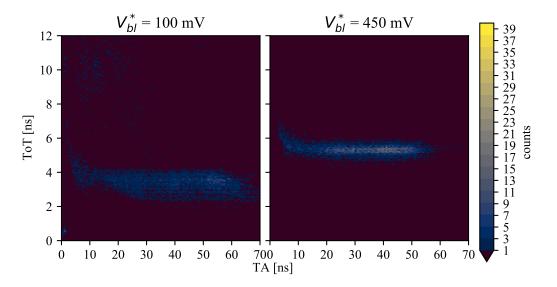

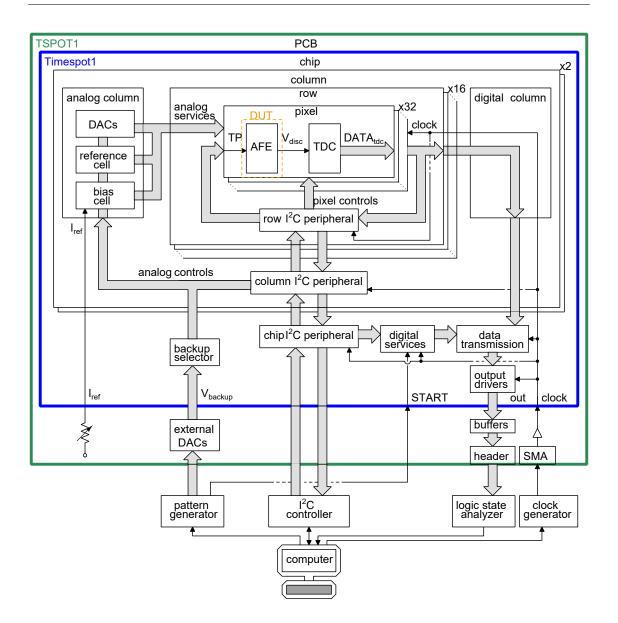

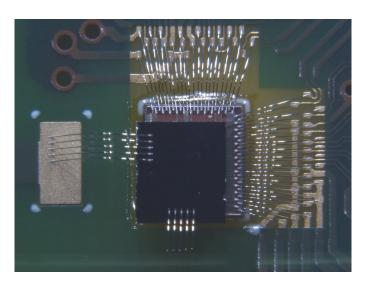

In summary, the best very front-end for timing must firstly minimize its output jitter. This can be done by minimizing the stage intrinsic noise while maximizing the time derivative of its amplitude. The time-walk component can be minimized by choosing a charge to time transfer function which minimizes the dependency from the input charge distribution. This can be achieved at the amplitude level by having a steeper conversion relation or with a limited bandwidth system. From this point of view, the jitter and time-walk components can be reduced together. Finally, the time walk can be also be limited with specific circuital solution on the discrimination process.