# Doctoral Dissertation Doctoral Program in Energy Engineering (36<sup>th</sup>cycle)

# Mix & Latch: High-Performance Designs with Single-Clock Mixed-Polarity Latches and Flip-Flops

By

## Filippo Minnella

\*\*\*\*\*

#### **Supervisor(s):**

Prof. Luciano Lavagno Prof. Mihai Lazarescu

#### **Doctoral Examination Committee:**

Prof. Peter Beerel, Referee, University of Southern California, Los Angeles, USA

Prof. Sachin Sapatnekar, Referee, University of Minnesota, Minneapolis, USA

Prof. Jordi Cortadella, Universitat Politècnica de Catalunya, Barcelona, Spain

Prof. Alex Yakovlev, Newcastle University, Newcastle upon Tyne, UK

Prof. Mario Casu, Politecnico di Torino, Torino, Italy

Politecnico di Torino 2024

## **Declaration**

Filippo Minnella 2024

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

#### **Abstract**

Sequential circuits often use flip-flops (FFs) or latches for data storage. Latches have advantages in error-resilient applications, lower supply voltage operation, reduced power consumption, and increased operating frequency. However, complex timing constraints have limited their adoption in commercial and industrial designs. To overcome this limitation, researchers have explored the automatic conversion of FF-based designs into latch-based designs, primarily focusing on performance enhancement by reducing the clock period and considering potential area improvements.

Different solutions have been proposed, including pulsed latch designs, multiphase clocking schemes and retiming methodologies. All of them have specific drawbacks that limit their deployment in industrial design flows which consist in: preventing pulse signal degradation in all operating conditions, increasing the area due to additional retimed registers, lack of fomal verification methodology or requiring multiple clocks generation and complex clock distribution networks.

In this thesis, we introduce a methodology called *Mix&Latch*, designed to address the mentioned limitations.

The key-points of the proposed flow are: trasforming flip-flop designs into positive transparent latches (PTLs) based designs that leverage time borrowing, incorporating negative transparent latches (NTLs) as retention barriers, instead of relying on delay padding, to address short-path hold constraints, employing a single clock tree throughout the design and merging adjacent latch pairs into positive-edge-triggered flops (PETFs) or negative-edge-triggered flops (NETFs) to reduce area overhead.

The first part of this thesis provides a comprehensive explanation of the proposed methodology. It describes the modeling of circuit timing and positional data, the conversion of the optimization problem into an integer linear programming (ILP) form and the enhancements made to the original methodology.

The second part of this thesis presents the experimental results obtained. In the initial version, experimental evaluations demonstrate the advantages of this approach on a suite of benchmark circuits. The enhancements to the algorithm are then evaluated on a *RISC-V* processor, showing a reduction in the implementation flow runtime, diminished area overhead, and enhanced timing performance in comparison to retiming, which was executed using a state-of-the-art commercial tool.

# **Contents**

| Li | List of Figures |               |                                          |      |

|----|-----------------|---------------|------------------------------------------|------|

| Li | st of '         | <b>Fables</b> |                                          | X    |

| 1  | Mot             | ivations      | 5                                        | 1    |

|    | 1.1             | Challe        | nges in sequential circuits design       | . 1  |

|    | 1.2             | Latch-        | based designs                            | . 3  |

|    | 1.3             | Proble        | m statement                              | . 5  |

| 2  | Prel            | iminary       | y analysis                               | 6    |

|    | 2.1             | Timing        | g analysis                               | . 6  |

|    | 2.2             | Clock         | skew                                     | . 8  |

|    | 2.3             | Retimi        | ing                                      | . 11 |

|    | 2.4             | Analyz        | zing different optimization models       | . 12 |

| 3  | Met             | hodolog       | gy                                       | 15   |

|    | 3.1             | Origin        | al flow                                  | . 15 |

|    |                 | 3.1.1         | Mix & Latch Optimization Flow            | . 18 |

|    |                 | 3.1.2         | Positive transparent latch-based circuit | . 20 |

|    |                 | 3.1.3         | Graph model                              | . 21 |

|    |                 | 3.1.4         | Timing Graph                             | . 21 |

vi Contents

|    |        | 3.1.5   | Short-Path Graph                                   | . 27 |

|----|--------|---------|----------------------------------------------------|------|

|    |        | 3.1.6   | Integer Linear Programming model                   | . 28 |

|    | 3.2    | Update  | ed flow                                            | . 31 |

|    |        | 3.2.1   | Post Synthesis Flow                                | . 33 |

|    |        | 3.2.2   | Reduce Pessimism                                   | . 33 |

|    |        | 3.2.3   | Worst-Path Flow                                    | . 34 |

|    |        | 3.2.4   | Formal verification                                | . 34 |

| 4  | Exp    | eriment | tal Results                                        | 35   |

|    | 4.1    | Origin  | al flow                                            | . 35 |

|    |        | 4.1.1   | Timing closure                                     | . 37 |

|    |        | 4.1.2   | Area comparison                                    | . 37 |

|    |        | 4.1.3   | Algorithm tuning to reduce area overhead           | . 38 |

|    |        | 4.1.4   | Comparison with other work                         | . 39 |

|    | 4.2    | Update  | ed flow                                            | . 39 |

|    |        | 4.2.1   | Test Setup                                         | . 39 |

|    |        | 4.2.2   | Performance, Area, and Power Analysis              | . 40 |

|    |        | 4.2.3   | Logic Cell Utilization                             | . 42 |

|    |        | 4.2.4   | Power Contributions                                | . 43 |

|    |        | 4.2.5   | Mix & Latch With Retiming                          | . 44 |

| 5  | Con    | clusion | and Future Work                                    | 49   |

| Re | eferen | ices    |                                                    | 51   |

| Δr | nend   | liv A F | Formal verification of the Mix & Latch methodology | 55   |

# **List of Figures**

| 1.1 | FF-based design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | latch-based design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

| 1.3 | dual_latch-based design                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4  |

| 1.4 | Mix & Latch-based design                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5  |

| 2.1 | Useful skew example                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8  |

| 2.2 | Constraint graph of the circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10 |

| 2.3 | Retiming example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 |

| 2.4 | Critical paths of the circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13 |

| 2.5 | Delay padded circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14 |

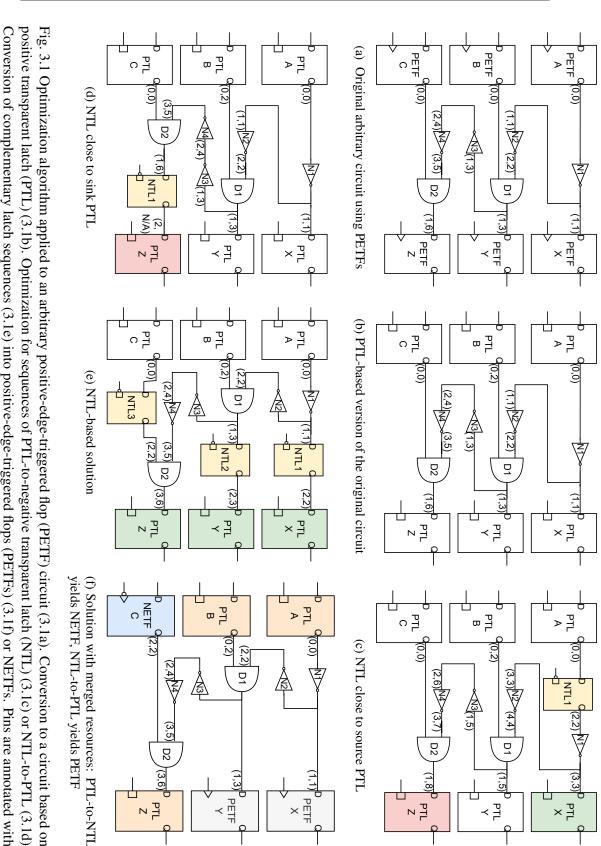

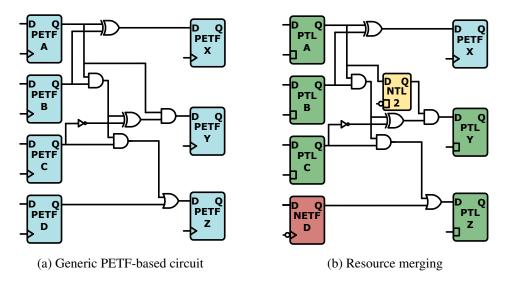

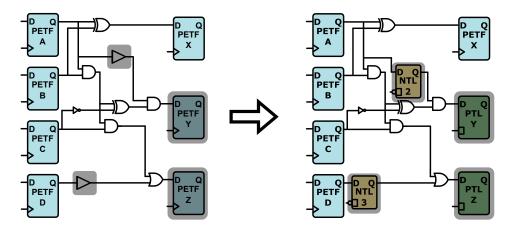

| 3.1 | Optimization algorithm applied to an arbitrary positive-edge-triggered flop (PETF) circuit (3.1a). Conversion to a circuit based on positive transparent latch (PTL) (3.1b). Optimization for sequences of PTL-to-negative transparent latch (NTL) (3.1c) or NTL-to-PTL (3.1d). Conversion of complementary latch sequences (3.1e) into positive-edge-triggered flops (PETFs) (3.1f) or NETFs. Pins are annotated with ( <i>minimum arrival time (AT</i> <sup>min</sup> ), <i>maximum arrival</i> |    |

|     | time $(AT^{\text{max}})$ ). Gate delays are unitary and sequential delays are zero                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

viii List of Figures

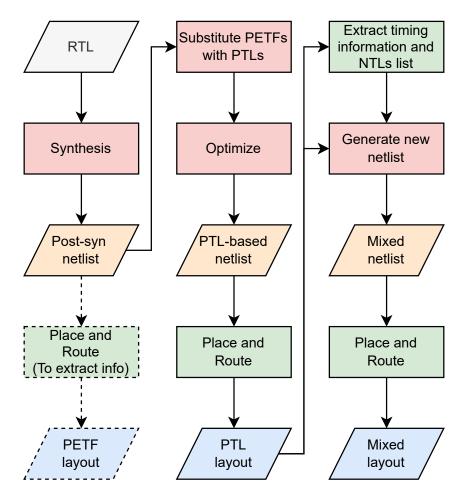

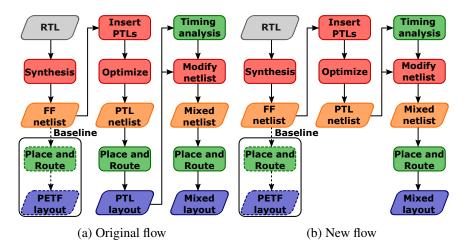

| 3.2 | Implementation flow starting from the register transfer level (RTL) description using positive-edge-triggered flops (PETFs), positive transparent latches (PTLs), and negative transparent latches (NTLs). Synthesis steps are in red, post-synthesis netlists in orange, layout steps in green, and post-layout netlists in blue. The PETF layout is only used to provide the baseline results                                                                                      | 19 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

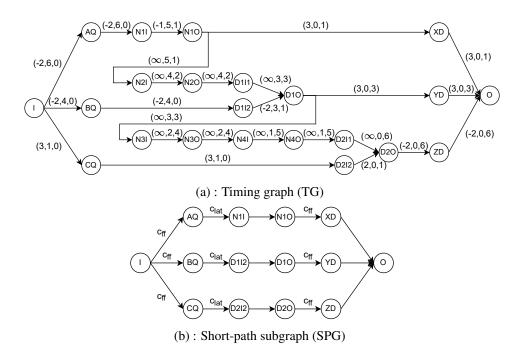

| 3.3 | Graph generation: (a) TG of the example in Fig. 3.1b. The attribute is a 3-tuple with elements computed using Alg. 2, Eqn. (3.6), and Eqn. (3.5), respectively. The first value is an estimation of the setup slack caused by NTL insertion, the second and third values are the lengths of the sub-paths generated by NTL insertion. (b) SPG of the same circuit: it has fewer edges and vertices than TG because it considers only pins and connections that belong to short paths | 22 |

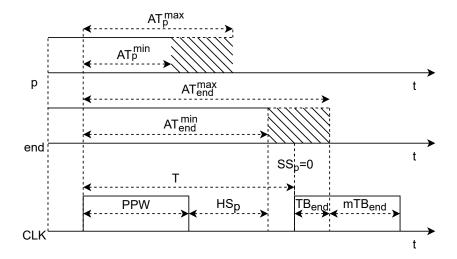

| 3.4 | Timing diagram, showing the arrival times and the slacks related to an ideal clock. During attribute computations the clock latencies are real and referred to the clock tree built in the PTL-based netlist. Because maximum arrival time at the endpoint pin $(AT_{\rm end}^{\rm max})$ arrives during the PTL transparent window, $setupslack(SS)_p$ is $0.\ldots$ .                                                                                                              | 23 |

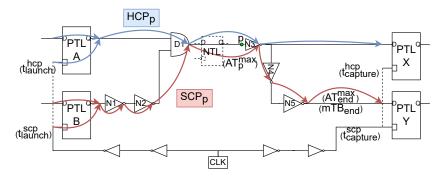

| 3.5 | Circuit showing how the information from the static timing analysis (STA) tool is extracted                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

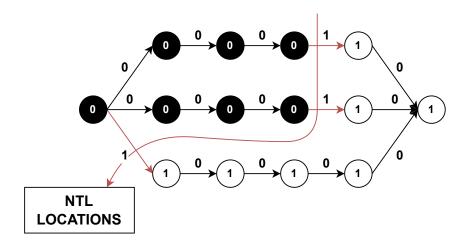

| 3.6 | Solution example showing the cut chosen for the SPG from Fig. 3.3b. The vertex attributes correspond to the $P$ variables of the ILP model and the edge attributes represent the edge selection value $(R(e,X))$ computed for each edge. The vertices with input edge attribute equal to 1 are selected for NTL insertion                                                                                                                                                            | 30 |

| 3.7 | Example of <i>Mix &amp; Latch</i> optimization on a PETFs-based circuit (Fig. 3.7a). Merge sequences of complementary latches: PTL-to-NTL into NETF, NTL-to-PTL into PETF (Fig. 3.7b). Combinational gates have unit delay only for ease of explanation. We consider as short paths those that cross one gate                                                                                                                                                                        | 31 |

List of Figures ix

| 3.8 | Comparison between the original (Fig. 3.8a) and the new post-synthesis (Fig. 3.8b) implementation flow. The new flow performs timing information extraction and netlist manipulation after the PTL-based netlist synthesis.                                                                                                                                  | 32 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | bused nethist synthesis                                                                                                                                                                                                                                                                                                                                      | 32 |

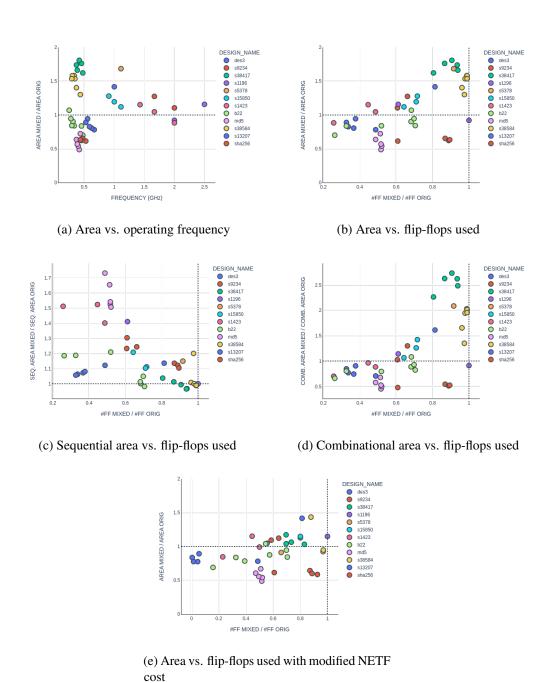

| 4.1 | Results of area comparison when both the mixed-based netlist and the PETF-based one successfully yield a layout                                                                                                                                                                                                                                              | 45 |

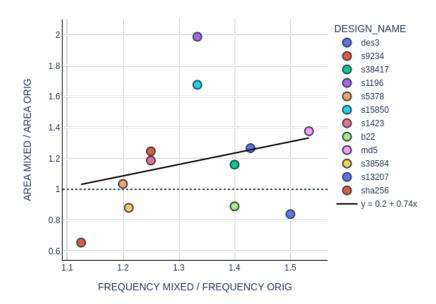

| 4.2 | Ratio of post-layout area, considering the layouts obtained at the highest working frequencies for both MIXED and ORIG versions, compared to the related frequency improvements. The black line shows the linear regression of the area increase with respect to the frequency gain. The offset and the slope of the line are stated in the                  |    |

|     | legend                                                                                                                                                                                                                                                                                                                                                       | 46 |

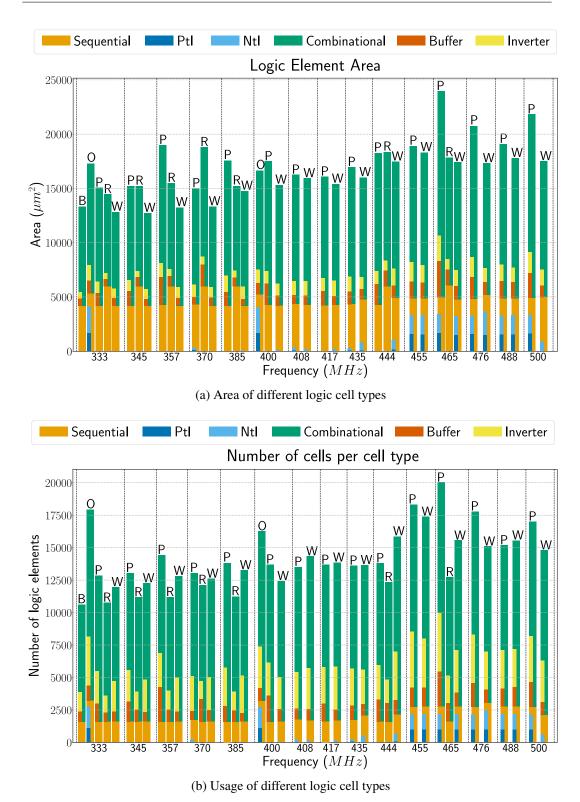

| 4.3 | Total area at different frequencies for baseline (B), original <i>Mix &amp; Latch</i> flow (O), post-synthesis <i>Mix &amp; Latch</i> (P), retiming (R), worst path (W), split into sequential and combinational contributions highlighting the fractions related to PTLs, NTLs, buffers, and inverters (Fig. 4.3a) and number of logic elements (Fig. 4.3b) | 47 |

|     |                                                                                                                                                                                                                                                                                                                                                              | 4/ |

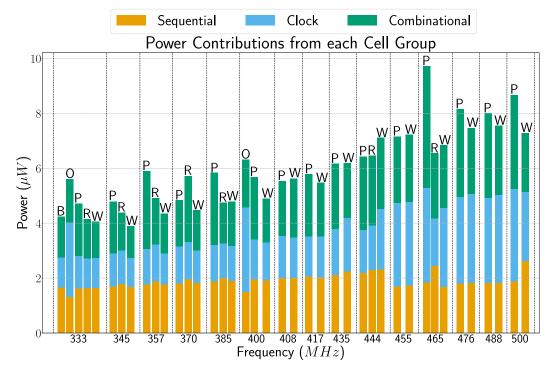

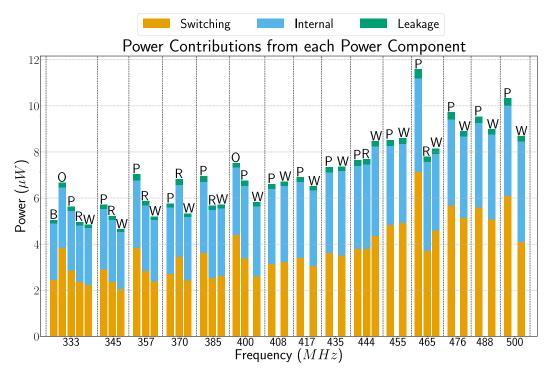

| 4.4 | Power consumption for original <i>Mix &amp; Latch</i> (O), post-synthesis <i>Mix &amp; Latch</i> (P), and retiming (R) at different operating frequencies, split by cell group (Fig. 4.4a) and by type of power (Fig. 4.4b)                                                                                                                                  | 48 |

# **List of Tables**

| 2.1 | Maximum frequency of the configurations                                                                                                                                                                                                                                                                                                 | 14  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Timing computed by Algorithm 2 with data from static timing analysis                                                                                                                                                                                                                                                                    | 24  |

| 3.2 | Variable definitions for Alg. 3. (ILP Model)                                                                                                                                                                                                                                                                                            | 28  |

| 4.1 | Operating frequency and sequential resources for designs from ISCAS°, CEP° and ITC99° benchmarks. Columns labeled 'Original' refer to PETF-based layouts, while those labeled "mixed" refer to the optimized ones.                                                                                                                      | 36  |

| 4.2 | ILP execution time (s) and layout times (s). Orig layout refers to the starting PETF netlist, PTL layout to the netlist without hold constraints and with only PTLs, and mixed layout to the final step after NTL insertion. The columns #SEQ. and #COMB. report the number of sequential and combinational elements in the PTL layout, | 2.5 |

|     | which is the netlist analyzed and provided to the ILP solver                                                                                                                                                                                                                                                                            | 37  |

| 4.3 | Performance comparison of implementation flows                                                                                                                                                                                                                                                                                          | 41  |

# **Chapter 1**

## **Motivations**

## 1.1 Challenges in sequential circuits design

Aggressive pipelining is common, in modern digital circuits, to push the maximum operating frequency. However, the addition of pipeline stages increases the number of registers and impact timing analysis complexity [1]. Furthermore, the addition of register stages caused by the extreme pipelining causes an increased use of resources translated in a higher area and power consumption.

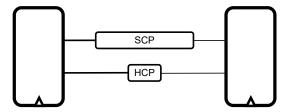

Timing analysis ensures the correct operation of digital circuits at a specified frequency. These timing requirements can be categorized into two distinct classes of constraints: 1. Setup timing constraints: These constraints primarily relates to slow-propagating signals along the setup critical paths (SCPs). They are concerned with determining the maximum clock speed and rely on the assessment of the longest signal paths within the circuit. 2. Hold timing constraints: These constraints are centered around fast-propagating signals along the hold critical paths (HCPs). Their primary objective is to prevent early-sampling errors between pipeline stages and hinge on the evaluation of the shortest signal paths.

In the realm of design methodologies, those based on FFs are the most prevalent due to their advantages in terms of simplified timing analysis and robust support within commercial electronic design automation (EDA) tools. Regarding the aspect of hold timing constraints, the primary concern revolves around managing clock skew between consecutive stages. It is imperative for this skew to be less than the delay of the shortest signal path. In FF-based designs, this issue typically does not pose

2 Motivations

a significant bottleneck. However, when employing aggressive pipelining, which entails increasing the number of sequential elements and consequently introducing a greater number of timing constraints, the complexity of the optimization problem can worsen. Setup timing constraints limit the maximum clock frequency of FF-based design. Splitting the logic in balanced pipeline stages, the longest paths are divided in shorter sub-paths, which timing is satisfied by smaller clock periods. However, exactly like for hold timing rules, the number of constraints to be satisfied increases with the addition of new pipeline stages.

Fig. 1.1 FF-based design

Latches offer advantages, primarily because they can operate at higher frequencies, thanks to a feature known as time borrowing [2]. Time borrowing permits slow-propagating signals to traverse a pipeline stage even after the clock edge, a limitation that exists in FF-based approaches. However, it's important to note that latch-based pipelines with a single-phase clocking scheme suffer from stringent minimum timing constraints.

Fig. 1.2 latch-based design

The potential for an early-sampling error condition between consecutive registers is amplified due to the presence of time borrowing. This extended window offers fast signals a larger time window to generate the race condition [3]. As a consequence, single-phase latch-based designs are notably challenging to employ and are generally avoided in industrial applications. Nevertheless, the inherent challenges of increasing the number of pipeline stages in digital circuits, drive the exploration of innovative

design and implementation approaches aimed at enhancing performance without necessitating additional stages.

## 1.2 Latch-based designs

Sequential circuits use FFs or latches for data storage. Latches can be used in error-resilient applications [4, 5], work at lower supply voltages, reduce power consumption [6–8], and can increase operating frequency [9, 10]. Different approaches have been proposed to solve the problem of implementing digital circuits using latches instead of FFs. Because of the complexity in designing latch-based circuits at register transfer level (RTL), it is more efficient to transform FF-based netlist in latch-based ones.

The seminal work of [11, 12] provides the formal definition of the system of equations which describe the timing behavior of a latch-based design. The authors show that the optimal timing analysis of a latch-based design can be performed by solving a system of equations similar to the one used for FF-based designs. After a linearization process, the system of equations is composed by linear equations and inequalities which can be solved using linear programming techniques. However, the increasing time to solve the linear programming model with bigger circuits strongly limit the applicability of this method.

A sub-group of solutions rely on generating a finite number of non-overlapping clocks, with optimized phases and duty cycles, fed to latches. The clocks definition is usually done using post-synthesis timing analysis. Zhang *et al.* [13] study the distribution of errors caused by sub-threshold voltage supply and propose a two-phase clocked latch-based method to solve the timing violations. Fojtik *et al.* [4] analyze a two clock-phase latch-based implementation of Razor flops to detect errors in an ARM Cortex-M3 processor. Cheng *et al.* [14] discuss a conversion algorithm using three clock phases to improve area and power consumption.

Another approach fully exploit duty cycle selection through the concept of *pulsed latch* introduced in [15–21]. These are composed by latches and pulse generators which shape the clock in input to latches in order to reduce their duty cycles to pre-computed value that respect min and max contraints. To limit the area cost, the pulse generators are shared by PTL groups and they are integrated either in a single

4 Motivations

sequential cell for pulsed FF (P-FF) (P-Ls with the pulse generator within the latch cell) or in a cell containing multiple sequential blocks for pulsed registers (P-Rs).

Nevertheless, with shared pulse generators it is very difficult to prevent pulse signal degradation in all operating conditions [15], and the additional retimed registers for solving the remaining hold violations further increase the area.

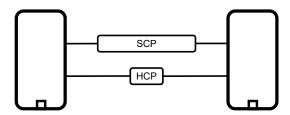

Another noteworthy set of solutions is the retiming-based approach. Retiming is a technique that aims to achieve optimal balancing of combinational paths between two registers by relocating the sequential element along the combinational paths. This concept bears resemblance to pipelining but is executed automatically during the implementation process, eliminating the need for manual intervention by the designer. In most cases, flip-flops (FF) are modeled using the master-slave approach, which employs two latches operating at opposite clock level polarities. Retimingbased approach moves master and slave latches in order to balance the combinational paths between them. These pairs of latches are working at opposite phases [22] avoiding the addition of complexity to the min-timing constraints because, exactly as in FF-based solutions, the requirement depends on the clock skew and the shortest path delay without the time borrowing addition. The additional register stages introduced by retiming can increase the complexity of the timing analysis and the area of the design. Yoshikawa et al. [23] present a single-phase forward retiming algorithm for FF-based design conversion, using commercial tools for retiming. Hassan et al. [7] and Singh et al. [6] present implementation flows to transform FF-based designs into latch-based or mixed designs. In almost all previous cases, the optimization uses post-synthesis timing information that may substantially differ from the post-layout one, thus potentially leading to grossly sub-optimal post-layout performance. Furthermore, [7, 23] evaluate the performance only on post-synthesis data, thus ignoring the place and route (P&R) overheads.

Fig. 1.3 dual\_latch-based design

#### 1.3 Problem statement

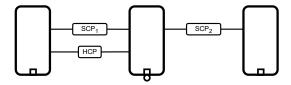

Latch-based circuits have the potential to enhance the performance of digital circuits by leveraging time borrowing, which allows longer paths to navigate through a pipeline stage. Despite these advantages, their adoption in commercial solutions is limited due to the intricate timing requirements stemming from stringent hold timing constraints imposed by the same time borrowing mechanism that boosts frequency. Various approaches have been proposed to address these challenges, often beginning with the formulation of the clocking problem using clocks featuring different duty cycles and phases. However, these approaches exhibit drawbacks that hinder their applicability within industrial implementation workflows. Multi-phase solutions necessitate the generation of multiple clocks, introducing a substantial overhead. On the other hand, pulsed-latch based solutions entail the inclusion of on-chip pulse generators, which result in added area overhead and complexity in ensuring the signal integrity of the numerous clocks supplied to the sequential elements. In contrast, retiming-based solutions have achieved state-of-the-art performance without complicating the implementation process. Nevertheless, since they involve relocating sequential elements within the circuit, they do not provide guarantees for formal verification and design correctness.

Fig. 1.4 Mix & Latch-based design

This thesis introduces a methodology known as *Mix & Latch*, which effectively tackles the issues discussed. This approach converts at first the FFs-based netlist in a single-phase latch-based circuit, and within it, places retention barriers to address the intricate minimum-timing constraints, thus alleviating the complexities in the implementation process. These retention barriers comprise latches that operate at the opposite polarity compared to the functional ones. Notably, there's no necessity to generate additional clocks because the retention barriers are synchronized with the same clock used by the functional latches. Importantly, the proposed methodology ensures the accuracy of the design and the feasibility of formal verification, as it maintains the original register positions intact.

# **Chapter 2**

# Preliminary analysis

## 2.1 Timing analysis

The timing analysis process in sequential circuits defines the critical paths and helps ensuring the correct sampling of the signals generated by the combinational logic. Depending the nature of the sequential elements, the analysis is different. For each different nature, the hold and setup constraints must be defined.

The simplest case is the one of the *flip-flops*, which are edge-triggered elements, i.e. the sampling of the data is performed at the rising or falling edge of the clock signal. Given a flip-flop (FF) j the longest path in input to the cell  $(\overline{d_{i,j}})$  contributes to the clock period (T) lower bound:

$$T - T_{setup_j} \ge \max_{i} \left\{ \overline{d_{i,j}} - \Delta_i \right\}$$

(2.1)

with  $\Delta_i$  equal to the maximum clock-to-Q delay of the sequential element *i*. The shortest path in input to the cell  $(\underline{d_{i,j}})$  do not introduce bounds to the clock in FFs-based systems, however it is important to consider it in order to avoid the early sampling of the signal:

$$T_{hold_j} \le \min_{i} \left\{ \underline{d_{i,j}} + \delta_i \right\} \tag{2.2}$$

with  $\delta_i$  equal to the minimum clock-to-Q delay of the sequential element *i*.

In latch-based circuits, that are level-sensitive elements, the analysis is more difficult. As already discussed in the previous chapter they allow for higher performance even though the possible early sampling caused by the transparent phase can lead to an error in the dataflow. The seminal works [11, 12] formalize the problem of the level-sensitive sequential circuits clocking, taking also into account the possible phase shifts between the sampling stages, and provide a *linear programming* model to find a solution to the optimal period clocking problem. The first additional degree of complexity is related to the computation of the maximum  $(D_i)$  and minimum  $(d_i)$  departure time of the signal from the launching latch i. They can happen in any time instant of its transparent phase, defined by the latch phase  $x_i$ :

$$D_i = \max_i \left\{ A_i, x_i \right\} \tag{2.3}$$

$$d_i = \max_i \left\{ a_i, x_i \right\} \tag{2.4}$$

Starting from these definitions, the minimum  $(a_j)$  and maximum  $(A_j)$  arrival times of the signal at the capturing latch:

$$A_{j} = \max_{i,j} \left\{ D_{i} + \Delta_{i} + \overline{d_{i,j}} + x_{i} \right\}$$

(2.5)

$$a_{j} = \min_{i,j} \left\{ d_{i} + \delta_{i} + \underline{d_{i,j}} + x_{i} \right\}$$

(2.6)

The setup Eq. (2.7) and hold Eq. (2.8) constraints now takes into account the transparent phase of the latches. Considering the *time borrowing* on the positive clock level, the setup constraints become less stringent by a factor of duty cycle (DC).

$$T \cdot (1 + DC) + x_j \ge A_j + T_{setup_j} \tag{2.7}$$

And the hold constraints worsen by the same factor:

$$T \cdot (DC) + x_j \le a_j - T_{hold_i} \tag{2.8}$$

#### 2.2 Clock skew

In sequential circuits, each sequential element is connected to a clock signal which is used to synchronize the operation of the circuit. During the synthesis step, in circuits using edge-triggered flip-flops, the optimization focuses in optimizing the logic paths in order to reduce the delay of the longest paths. However, the physical synthesis of the clock tree introduces delays in the arrival time of the clock signal at the different sequential elements. Considering two flip-flops i,j connected by combinational logic, and their phases  $x_i$ ,  $x_j$ , the clock skew is defined as the difference of the two phases:

$$\Delta x_{i,j} = x_j - x_i \tag{2.9}$$

These unbalances in the sampling instant of the sequential elements introduce the possibility of early sampling, *hold constraints violation*, or late sampling, *setup constraints violation*, of the data.

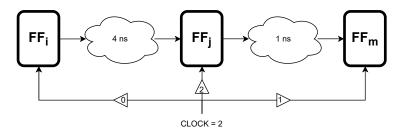

The first approaches to the implementation of the clock tree tried to minimize the clock skew, *zero skew* [24], in order to meet the hold and setup analysis performed at synthesis time. However, by correctly scheduling the clock phases [25–27], *fixed skew*, it is possible to achieve a lower clock period thanks to cycle borrowing, i.e. delaying the capturing time for long paths. Fig. 2.1 shows an example of useful skew applied to a sequence of pipeline stages.

Fig. 2.1 Useful skew example

[27] proposes a method to find the minimum clock period of a circuit computing if there is a possible clock schedule that satisfies the timing constraints. Given a circuit composed of N sequential elements, the clock period T, the clock phases  $x_i$ ,  $x_j$  of two sequential elements i,j, two inequalities are defined to avoid the early and late sampling of the data. To avoid late sampling the capturing time of the sequential element j should be greater than the latest arrival time  $(\overline{d_{i,j}})$  of the data:

2.2 Clock skew 9

$$x_j + T \ge x_i + \overline{d_{i,j}} + T_{setup} \tag{2.10}$$

To avoid early sampling instead, the capturing time of the sequential element j should be less than the earliest arrival time  $(d_{i,j})$  of the input data:

$$x_j \le x_i + \underline{d_{i,j}} - T_{hold} \tag{2.11}$$

Considering the two inequalities, it possible to formulate the minimization of the clock period problem as:

minimize

$$T$$

(2.12)

subject to

$$x_j - x_i \ge \overline{d_{i,j}} - T + T_{setup}$$

(2.13)

$$x_i - x_j \le T_{hold} - d_{i,j} \tag{2.14}$$

$$\forall i \in \{1, \dots, N\} | x_i | \le T \tag{2.15}$$

The constraints 2.10 and 2.11 constitutes the first two inequalities of the problem, the last one ensures that the maximum phase shift is lower than the clock period.

To solve this problem, [27] proposes a binary search algorithm which iterates on the clock period, tracing the minimum and maximum limit of the search interval and looking if the minimum proposed value for the clock period is feasible or not. If a specific clock period is feasible then the maximum value of the considered interval will be updated, if not then the minimum value will be updated. The feasibility check is done through a Bellman-Ford like algorithm that looks for *positive cycles* after the clock schedule.

To reduce the number of iterations, the low and high bounds are defined. The minimum bound  $(T_{low})$  is computed as:

$$T_{i,j} = \overline{d_{i,j}} - d_{i,j} + T_{setup} + T_{hold}$$

(2.16)

$$T_{low} = \max_{i,j} \left\{ T_{i,j} \right\} \tag{2.17}$$

and depends on the time window in which the data can be sampled.

The maximum bound  $(T_{high})$  is defined as:

$$T_{high} = \max_{i,j} \left\{ \overline{d_{i,j}} + T_{setup} \right\}$$

(2.18)

and depends on the maximum delay of the combinational paths. The iterative search algorithm is shown in Algorithm 1.

#### Algorithm 1 Binary search algorithm for the clock period

```

1: T_{min} \leftarrow T_{low}

2: T_{max} \leftarrow T_{high}

3: while T_{max} - T_{min} > \varepsilon do

4: T \leftarrow \frac{T_{min} + T_{max}}{2}

5: feasible \leftarrow \text{Bellman-Ford}(T)

6: if feasible then

7: T_{max} \leftarrow T

8: else

9: T_{min} \leftarrow T

10: end if

11: end while

```

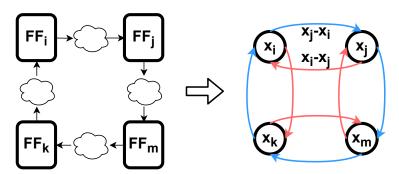

Given the computed  $T_{max}$ , any clock period  $T \ge T_{max}$  is feasible. To evaluate the *Bellman-Ford* algorithm, the circuit is represented as a graph where the vertices are the clock phases of the sequential elements and the edges are the relations defined by 2.10 and 2.11. Figure 2.2 shows the constraints graph of an example circuit.

Fig. 2.2 Constraint graph of the circuit

Another problem which should be considered when optimizing the skew scheduling is the *wave pipelining*, which is the coexistence of two different propagating values in the same combinational path caused by the unbalanced sampling time at different stages of the pipeline. As proposed by [28], starting from the model

2.3 Retiming

proposed in [25] specific constraints should be applied to avoid the overlap of the two propagations.

## 2.3 Retiming

Retiming is a technique that aims to achieve optimal balancing of combinational paths between two registers by relocating the sequential element moving them across the logic gates. This technique do not change the number of registers on a path

Fig. 2.3 Retiming example

from primary inputs to primary outputs, thus not changing the total latency of the considered block or the behaviour of the circuit.

It could lead to further optimization in the delay of the combinational logic because it changes the boundaries of the combinational paths. Retiming could be applied to optimize multiple metrics, this work introduces only the clock period minimization. It can be applied to both edge-triggered based sequential circuits and level-sensitive based ones.

The ASTRA approach [29] shows the relations between retiming and clock skew scheduling in minimum period optimization. The example figures 2.1 and 2.3, describes the same circuit with different optimization techniques applied; the first one shows how increasing the latency applied to the  $FF_j$  to 2 reduces the clock period to 2 units, the second one shows how moving the  $FF_j$  backward in the combinational logic reaches the same result with a lower delay  $x_j$ . From the examples, the equivalence between the two methods is clear. The reduction in the clock latency is equivalent to the time delay of the combinational logic moved to the second stage of the pipeline.

The formal definition from [29] describes the equivalnce as:

- *Backward Retiming*: moving a register backward in the combinational logic corresponds to decreasing the delay of the clock signal feeding it.

- *Forward Retiming*: moving a register forward in the combinational logic corresponds to increasing the delay of the clock signal feeding it.

The generalization of the equivalence to a multi-input and multi-output combinational circuit is straightforward:

• Given a circuit that has a double sampling stage at the input, one of the two stages is forward retimed to the output. For each sequential element *j* retimed to the output, the delay of the clock signal feeding it is:

$$x_j = \max_i \left\{ x_i + \overline{d_{i,j}} \right\} \tag{2.19}$$

Which is equivalent to the clock phase able to satisfy the setup constraints at the output of the combinational block.

• Similarly, given a circuit that has a double sampling stage at the output and one of the two stages is backward retimed to the input. For each sequential element *k* retimed to the input, the delay of the clock signal feeding it is:

$$x_k = \min_{j} \left\{ x_j - \overline{d_{k,j}} \right\} \tag{2.20}$$

Which is equivalent to the clock phase able to satisfy the setup constraints.

The ASTRA approach uses this equivalence to efficiently perform the retiming of the circuit. The algorithm looks for a feasible clock schedule for the sequential elements of the circuit, and then moves the registers accordingly over the logic. Once that a register is moved, the clock schedule is updated accordingly. If at the end of the procedure the clock delays of all the flip-flops are zero, then the optimal clock period is reached.

## 2.4 Analyzing different optimization models

As discussed in the previous sections, it becomes evident that optimization through skew scheduling yields the lower bound for period minimization, which extends to the retiming problem as well. Utilizing the methodology proposed by [27] for determining the lower bound of the clock period also results in optimal performance for the retiming problem. The presented *constraint graph* considers both setup and hold constraints to enable the determination of the scheduling of various clock phases. It's essential to note that the combinational delay of the most critical cycle has a finite margin for optimization, thus establishing a limit on the circuit's maximum frequency. Fig. 2.4 illustrates the critical paths within the same constraint graph, excluding the edges accounting for the short paths.

Fig. 2.4 Critical paths of the circuit

This configuration serves the purpose of determining the lower bound for the clock period using the same database that was initially computed for the original algorithm. If a disparity arises between the maximum frequency identified in the initial configuration and the frequency determined by exclusively considering setup critical paths, the variance is attributed to the hold critical paths. A remaining scope for improvement exists that cannot be fully realized through clock skew adjustments and retiming alone. A potential approach to address this issue involves introducing delay padding to the combinational logic, specifically on the segments of the hold critical paths that do not overlap with setup critical paths. The work by [30] introduces a linear programming (LP) model to identify the optimal amount of delay padding required on short paths to mitigate the issues related to hold constraints.

To evaluate the potential benefits of this approach for optimizing the clock period, one possible solution is to incorporate the delay padding into the constraint graph and employ the Bellman-Ford algorithm to determine the circuit's maximum frequency. Fig. 2.5 depicts the constraint graph with delay-padded paths, extending up to a predetermined value equal to the high time of the clock cycle  $(DC \cdot T)$ .

This model is valid for both FF-based and latch-based circuits. Despite the information presented in Eq. (2.7), the setup constraints for latch-based circuits are

Fig. 2.5 Delay padded circuit

the same of FF-based approach. The maximum setup optimization through latch time borrowing overlaps with the one obtainable by retiming. As shown by Eq. (2.8) latch-based circuits, the main problem is the early sampling of the data caused by the extended transparent phase of the clock signal. The delay padding enables solving this problem and allows the scheduling of the clock. The table 2.1 shows the maximum frequency of the different configurations for the circuits considered in this work. The duty cycle for this analysis is set to 50%.

| Circuit | Original (ns) | Setup Opt. (ns) | <b>Delay padded</b> (ns) |

|---------|---------------|-----------------|--------------------------|

| s1196   | 0.182         | 0.182           | 0.218                    |

| s1423   | 0.469         | 0.469           | 0.469                    |

| s5378   | 0.324         | 0.324           | 0.324                    |

| s15850  | 0.739         | 0.645           | 0.645                    |

| s38584  | 0.632         | 0.632           | 0.632                    |

| des3    | 0.729         | 0.486           | 0.646                    |

Table 2.1 Maximum frequency of the configurations

The results indicate that with the exception of two cases, namely s15850 and des3, the primary limiting factor for the maximum circuit frequency are the setup critical paths. This observation relies from the fact that both the analysis of the original constraint graph and the configuration focusing solely on setup critical paths yield identical outcomes. The delay padding approach is capable of achieving, at a minimum, the same frequency as the original configuration, except in the case of s1196. In the context of the s15850 and des3 circuits, the delay padding approach surpasses the original configuration's frequency. This superiority is attributed to the constraints imposed by the hold critical paths. Consequently, this benchmarking exercise highlights the need to explore solutions that can assist the scheduling of clock delays in order to attain higher frequencies.

# **Chapter 3**

# Methodology

## 3.1 Original flow

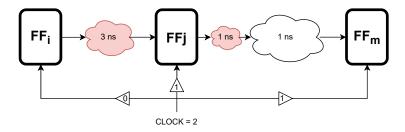

This chapter proposes the *Mix&Latch* method, which uses a conventional 50% duty cycle (DC) single-phase clock. Hold time violations are solved by inserting NTLs driven by the same clock tree as the PTLs. First *the resulting clock period is optimized* by combining time borrowing and NTL retiming. Then, as a *secondary objective, area recovery is used to reduce the area overhead* by creating NTL-PTL sequences whenever possible. These primary/secondary pairs are then converted into either PETFs or NETFs, thus obtaining an optimized *mixed* design with PTL, PETF, NTL, and NETF sequential elements. *Mix&Latch* also preserves a sequential element in each of the original FF locations. This enables a 1-to-1 mapping from FFs to sequential elements and ensures that equivalence checking can be performed using conventional methods comparing combinational clouds.

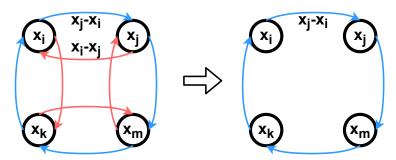

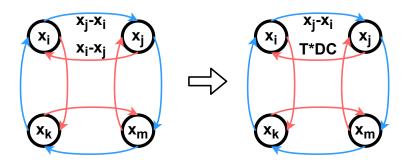

Fig. 3.1 shows the application of this optimization algorithm to a simple case  $^1$ . The original arbitrary PETF circuit is shown in Fig. 3.1a. All pins are annotated with a parenthesized number pair indicating the (*minimum arrival time at pin p* ( $AT_p^{\min}$ ), *maximum arrival time at pin p* ( $AT_p^{\max}$ )). For simplicity, the assumption in this figure is of unitary delays for combinational gates, zero delays for the sequential elements, and zero setup/hold FF constraints, while this algorithm uses delays from timing analysis. In a PETF-based circuit, the minimum clock period,  $T_{\min}$ , is set to the

<sup>&</sup>lt;sup>1</sup>The circuit in Fig. 3.1 do not account for interactions with I/O pins because they are always modeled as being sampled by FFs and this would increase the complexity of the example.

16 Methodology

positive transparent latch (PTL) (3.1b). Optimization for sequences of PTL-to-negative transparent latch (NTL) (3.1c) or NTL-to-PTL (3.1d).  $(minimum\ arrival\ time\ (AT^{min}),\ maximum\ arrival\ time\ (AT^{max})).$  Gate delays are unitary and sequential delays are zero. Conversion of complementary latch sequences (3.1e) into positive-edge-triggered flops (PETFs) (3.1f) or NETFs. Pins are annotated with

3.1 Original flow

longest maximum arrival time at the endpoint pin  $(AT_{\rm end}^{\rm max})$ , hence  $T_{\rm min}=6$  in this example. After the PTL conversion shown in Fig. 3.1b, the circuit can use time borrowing up to half a clock period (for DC=50%) for  $AT_{\rm end}^{\rm max}$

$$AT_{\text{end}}^{\text{max}} = T_{\text{min}} \left( 1 + DC \right) \Longrightarrow T_{\text{min}} = \frac{6}{1 + 0.5} = 4. \tag{3.1}$$

Note that there is an additional critical path with delay 6, PTL B  $\rightarrow$  PTL Z, due to time borrowing at PTL B.

Despite the desirable  $T_{\min}$  reduction by 33% compared to the PETF version, there are hold violations at the inputs of PTLs X, Y, and Z because their minimum arrival time ( $AT^{\min}$ ) is lower than the positive pulse width,  $PPW = DC \cdot T_{\min}$ . To solve the hold violations, a group of nets is selected using the mathematical model described below, and an NTL is placed in front of the endpoint pin of the selected nets. As the NTLs become transparent after the positive pulse, they guarantee a delay longer than the PPW for all paths.

However, the added NTLs can reduce performance. For example, Fig. 3.1c shows that while placing the NTL too close to the source PTL solves the hold violation at the input of PTL X, the additional delay causes a setup violation at the input of PTL Z, which now requires a longer period,  $T > T_{\min}$ . Fig. 3.1d shows that a NTL can solve the hold violations at the input of PTL Z, but it causes a new setup violation at the input of the NTL that closes at T. Hence, the signal cannot reach PTL Z in time, which also requires a longer  $T > T_{\min}$ .

This algorithm optimizes the position of NTLs to reach a solution that, as shown in Fig. 3.1e, solves all hold violations without performance penalty, under the assumptions discussed in Section 3.1.4.

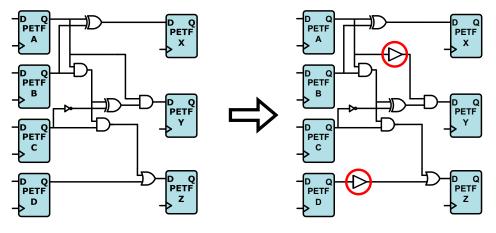

Next, adjacent NTL-PTL pairs are merged as PETF to reduce the area, and PTL-NTL pairs as NETF, as shown in Fig. 3.1f. This solution has the same  $T_{\min}$  and area as the one in Fig. 3.1b, no hold violations, and uses the same number of sequential elements as the original version. In some cases part of the latches cannot be merged, which leads to area penalty (discussed in the experimental results). In other cases the PTLs do not need hold time fixing, yielding both faster and smaller circuits.

Several works propose design optimization using a mix of PETF and PTL. Here there are described the main ones, in order to set the stage for this chapter. Hassan 18 Methodology

et al. [7] propose to start from an FF-based netlist, analyze sequences of three FFs, and replace the middle one with a PTL retimed to match the timing constraints. This approach seems to increase the clock frequency, reduce the power consumption and the cell area, but the experimental data cover only logic synthesis, without considering placement and routing. Furthermore, equivalence checking may be more difficult because retiming changes the original position of the sequential elements [31].

Singh *et al.* [6] describe a retiming method to generate a PTL-NTL-based netlist starting from a FF-based one. Because the synthesis tools have poor support for latch retiming, they propose replacing the primary/secondary latches with FF pairs, doubling the frequency and finally retiming the design using a commercial tool. Although they focus on reducing the power consumption, the results are poor in terms of both power and area because the algorithm is effective for only one frequency due to a sub-optimal retiming strategy. Moreover, experimental results are shown only for one circuit.

The main contributions to the state-of-the-art are:

- A two-step implementation flow to obtain a working layout for an optimized version (Fig. 3.1f) of the PETF-based netlist (Fig. 3.1a). The implementation is fully based on commercial EDA tools and fully exploiting useful skew, both in the baseline against which this chapter compares and in the obtained results.

- A methodology to reduce the sequential resources and generate the NTL allocation, using post-layout timing data and exploiting incremental placement and routing starting from the post-layout netlist. The NTLs work as retention barriers for signals in short paths, reducing the hold constraints complexity. To recover area, the PTL-NTL pairs are merged into FFs.

- Maintaining a 1-to-1 correspondence between each original FF and a FF or a latch in the final circuit, to allow equivalence checking for design verification with traditional tools.

## 3.1.1 Mix & Latch Optimization Flow

Fig. 3.2 shows the optimization flow, which starts from a RTL description and produces a layout with mixed sequential resources. It includes four main steps:

3.1 Original flow

Fig. 3.2 Implementation flow starting from the register transfer level (RTL) description using positive-edge-triggered flops (PETFs), positive transparent latches (PTLs), and negative transparent latches (NTLs). Synthesis steps are in red, post-synthesis netlists in orange, layout steps in green, and post-layout netlists in blue. The PETF layout is only used to provide the baseline results.

20 Methodology

• Generate the PTL-based layout by replacing all sequential elements with PTLs (shown in the second column in Fig. 3.2 and discussed in Section 3.1.2).

- Create a graph representation of the timing and positional information extracted from the PTL-based layout (discussed in Section 3.1.3, Section 3.1.4, and Section 3.1.5).

- Define the circuit location of NTLs, PETFs, and NETFs using an ILP formulation, and inserting them in the PTL-based netlist.

- Generate the layout of this new circuit (see the right column in Fig. 3.2 and the discussion in Section 3.1.6).

The NTL selection using ILP is similar to backward retiming [23] in a primary/secondary FF netlist. However, the formulation and graph representation are different because they consider the post-layout timing data and avoid the redundant NTLs. The designs are synthesized and implemented at several clock frequencies to determine iteratively the highest possible operating frequency for both the mixed design and of the PETF design.

We leave to future work the in-depth analysis of design for testability (DFT) needed for the practical adoption of our methodology. We note however that DFT can be implemented with traditional tools by adding some scan-only NTLs to the PTLs [32].

Retiming techniques have the drawback that equivalence checking for design verification cannot be solved in a reasonable amount of time even for relatively small circuits, such as the s38584 from the ISCAS benchmark [31], which we also use in our experiments as shown in Section 4.1. *Mix & Latch* does not have this problem because it preserves a 1-to-1 correspondence with the FFs in the original design using either FFs or PTLs. The 1-to-1 correspondence also helps solving the initialization problem for the netlist, i.e., finding a consistent initial value of the circuit registers that maintains the circuit equivalence [33].

## 3.1.2 Positive transparent latch-based circuit

The first processing step generates the PTL-based layout. The RTL description of the target design is synthesized using a commercial tool. The considered circuits have only PETFs to ease the analysis, but the same methodology can be extended to circuits based on NETFs or mixed. Once the netlist is synthesized, all the PETFs are replaced with PTLs using the same commercial tool. Because cell resizing will be automatically done by the layout tool (if needed), the PETFs are replaced with the smallest PTLs from the technological libraries.

The netlist modified this way is provided to the layout tool, which produces the post-P&R design. Unlike [11, 12], all hold constraints are temporarily ignored (using a standard design constraint command of the tool) to obtain a layout of the PTL-based netlist that meets the setup constraints.

The generated layout thus potentially violates hold conditions, which will be solved afterwards.

#### 3.1.3 Graph model

The state-of-the-art circuit graph representations [34, 12] are not suitable for our optimization algorithm because they either exclude the sequential elements [34], or aggregate pin data for the worst case delay [12].

For our method, the circuit is represented as a graph (V, E), where V represents the set of all pins and I/O ports and E the connections (wires or cells) between them. The nets and pins of the clock tree are not included. All sampling of input and output ports is defined as synchronous, coinciding with the rising edge of the system clock. This means that no borrowing of time from the environment is permitted and the new circuit uses the same boundary conditions as the original one.

Fig. 3.3 shows an example of two graphs which are discussed later. Static timing analysis (STA) timing information is a three-value tuple associated to graph edges (see Section 3.1.4), while latch location is a value associated to edges of a different graph (see Section 3.1.5).

## 3.1.4 Timing Graph

We create a timing graph (TG) that drives our optimization algorithm to limit the setup slack (SS) degradation due to potential NTL insertions before gate input pins in the PTL-based netlist. The computation of the edge attributes of this graph

22 Methodology

Fig. 3.3 Graph generation: (a) TG of the example in Fig. 3.1b. The attribute is a 3-tuple with elements computed using Alg. 2, Eqn. (3.6), and Eqn. (3.5), respectively. The first value is an estimation of the setup slack caused by NTL insertion, the second and third values are the lengths of the sub-paths generated by NTL insertion. (b) SPG of the same circuit: it has fewer edges and vertices than TG because it considers only pins and connections that belong to short paths.

uses the timing data extracted from static timing analysis (STA), shown in Fig. 3.4, Fig. 3.5, and Table 3.1. Unlike Fig. 3.4, all arrival times are obtained from the STA considering the clock latencies of the PTL-based layout. The pin (p) for which STA extracts the info is the endpoint of the edge (e) to which the related attribute is associated. From the STA timing data we obtain three values: (1) the *Estimated Setup Slack for pin p*  $(ESS_p)$ , (2) the p to  $SCP_p$  endpoint delay  $(D_{ptl}^p)$ , and (3) the  $SCP_p$  startpoint to p delay  $(D_p^{ptl})$ . These three values are assigned as a 3-tuple attribute to the edges of timing graph (TG).

#### **Estimated Setup Slack**

The Estimated Setup Slack  $(ESS_p)$  is computed for each edge (e) endpoint pin (p) using Algorithm 2, which estimates the value of the setup slack (SS) related to the pin (p) if an NTL were placed in front of it. It receives in input the timing info from STA for the considered pin and returns the attribute  $ESS_p$ . It is important to highlight

Fig. 3.4 Timing diagram, showing the arrival times and the slacks related to an ideal clock. During attribute computations the clock latencies are real and referred to the clock tree built in the PTL-based netlist. Because  $AT_{\rm end}^{\rm max}$  arrives during the PTL transparent window,  $SS_p$  is 0

Fig. 3.5 Circuit showing how the information from the STA tool is extracted.

24 Methodology

Table 3.1 Timing computed by Algorithm 2 with data from static timing analysis

| DEFINITION                                                     |

|----------------------------------------------------------------|

| Hold critical path passing through pin p                       |

| Setup critical path passing through pin p                      |

| Clock latency of the considered HCP <sub>p</sub> launching PTL |

| Clock latency of the considered $SCP_p$ launching PTL          |

| Maximum arrival time at pin p                                  |

| Minimum arrival time at pin p                                  |

| Setup slack at pin p                                           |

| Hold slack at pin p                                            |

| Clock latency of the considered $HCP_p$ endpoint PTL           |

| Maximum arrival time at endpoint PTL                           |

| Minimum arrival time at endpoint PTL                           |

| Time borrowing margin at endpoint PTL of $SCP_p$               |

| Time borrowing at endpoint PTL of $SCP_p$                      |

| Clock positive pulse width                                     |

|                                                                |

that the computation of  $AT_p^{\text{max}}$  takes into account the possible time borrowed by the launching PTL. It relies on the following assumptions:

- To estimate the  $SS_p$  degradation caused by the NTL insertion, we need the NTL opening time,  $t_{\rm open}^{\rm ntl}$ , and closing time,  $t_{\rm close}^{\rm ntl}$ . They depend on the NTL clock latency ( $t_{\rm del}^{\rm ntl}$ ), from PPW and from T. Since it is difficult to know  $t_{\rm del}^{\rm ntl}$  at this stage, we assume that it is equal to  $t_{\rm capture}^{\rm HCP}$ , unless an NTL is merged into a NETF when we use the latency  $t_{\rm launch}^{\rm HCP}$ .

- In Fig. 3.4, the NTL would have the clock latency of PTL X. Lines 4–10 implement these computations. The condition on line 4 checks if the pin is the output of a PTL, thus the resulting NTL would be merged into a NETF.

- The additional delay from NTL insertion is ignored because it is usually small compared to the SCP<sub>p</sub> delay and because it is hard to estimate before the layout. Note that we ignore it only to simplify the TG generation, but in the final layout step the P&R tool does consider the NTL delays.

3.1 Original flow 25

#### **Algorithm 2** Estimated Setup Slack attribute for pin p

```

Inputs: Parameters from Table 3.1 Output: ESS_p

1: if HS_p \ge 0 then

2:

ESS_p \leftarrow \infty

3: else

if p is output of PTL then

4:

t_{\mathrm{del}}^{\mathrm{ntl}} \leftarrow t_{\mathrm{launch}}^{\mathrm{HCP}}

5:

6:

t_{\text{del}}^{\text{ntl}} \leftarrow t_{\text{capture}}^{\text{HCP}}

7:

end if

8:

t_{	ext{open}}^{	ext{ntl}} \leftarrow t_{	ext{del}}^{	ext{ntl}} + PPW

t_{	ext{close}}^{	ext{ntl}} \leftarrow T + t_{	ext{del}}^{	ext{ntl}}

if AT_p^{	ext{max}} < t_{	ext{open}}^{	ext{ntl}} then

9:

10:

11:

ESS_p \leftarrow SS_p - t_{\text{open}}^{\text{ntl}} + AT_p^{\text{max}} + mTB_{\text{end}}

12:

13:

if AT_p^{\text{max}} > t_{\text{close}}^{\text{ntl}} then

14:

ESS_p \leftarrow t_{\text{close}}^{\text{ntl}} - AT_p^{\text{max}}

15:

16:

ESS_p \leftarrow SS_p + mTB_{\text{end}}

17:

18:

end if

19:

20: end if

```

We explain the steps in Algorithm 2 analyzing the four cases which cover all the possible combinations, while in Fig. 3.3a we illustrate an example of TG for the circuit of Fig. 3.1b:

Case 1 — Positive hold slack If the considered p has positive hold slack,  $HS_p$ , then there is no violation to fix. To reduce the number of NTLs that will be used after retiming, all the NTLs that would be placed close to pins not belonging to short paths will not be added to the PTL netlist. Avoiding NTL insertion means no  $SS_p$  degradation, hence in this case we set weight (W) to  $\infty$  (lines 6–7 of Algorithm 2). An example is the edge  $D1O \rightarrow N3I$  in Fig. 3.3a, corresponding to the edge  $D1 \rightarrow N3I$  in Fig. 3.1b, which does not belong to a short path.

Case 2 — NTL close to the source PTL The additional delay caused by the late opening of the NTL may cause a setup violation, as shown in Fig. 3.1c. Attribute computation estimates the degradation of the pin setup slack, taking into account the late arrival time at the selected pin  $(AT_p^{\text{max}})$ ,  $SS_p$ ,  $t_{\text{open}}^{\text{ntl}}$ , and the margin for time

26 Methodology

borrowing ( $mTB_{\rm end}$ ). The delay introduced by the NTL can be tolerated up to  $mTB_{\rm end}$ . Lines 11–12 of Algorithm 2 perform these computations. An example is edge  $AQ \rightarrow NII$  from Fig. 3.3a, corresponding to the edge from PTL A to NI in Fig. 3.1c.

Considering that the SCP for this edge ends in PTL Z, the parameters  $SS_p$ ,  $AT_p^{\text{max}}$  and  $mTB_{\text{end}}$  are all equal to 0 because the SCP delay is equal to the T added to the maximum time borrowing.  $t_{\text{open}}^{\text{ntl}}$  is equal to 2 for all the cases shown in Fig. 3.3a because the clock is considered ideal. Given the previous considerations, compute  $ESS_p$ :

$$ESS_p = 0 - 2 + 0 + 0 = -2 (3.2)$$

Case 3 — NTL close to the sink PTL If the input signal of the sink PTL belongs to a critical path, then the setup constraints added by the early NTL closing will likely prevent satisfying the setup constraints. If the late arrival time at the pin,  $AT_p^{\max}$ , exceeds  $t_{\text{close}}^{\text{ntl}}$ , then the signal will not pass through the NTL. The  $SS_p$  degradation is computed as the difference between these two values (lines 14–15 of Algorithm 2). An example is edge  $D2O \rightarrow ZD$  from Fig. 3.3a, corresponding to the edge from D2 to PTL Z in Fig. 3.1d.  $t_{\text{close}}^{\text{ntl}}$  is equal to 4 for all the cases because the clock is considered ideal and  $AT_p^{\max}$  is 6. Given the previous considerations,  $ESS_p$  is computed as:

$$ESS_n = 4 - 6 = -2 \tag{3.3}$$

Case 4 — General case If none of the previous cases occurs, then  $AT_p^{\text{max}}$  at the NTL input falls into the NTL transparency interval and there is no  $SS_p$  degradation (line 17 of Algorithm 2). An example is edge  $DIO \rightarrow YD$  from Fig. 3.3a, corresponding to the edge from DI to PTL Y in Fig. 3.1d.

Considering that the SCP for this edge ends in PTL Y,  $SS_p = 1$  because the signal arrives 1 time unit before the rising edge of the clock, while  $mTB_{\rm end} = 2$  because there is no time borrowing. Given the previous considerations,  $ESS_p$  can be computed as:

$$ESS_p = 1 + 2 = 3 (3.4)$$

3.1 Original flow

#### Sub-path delays

The second value of the tuple,  $D_{\text{ptl}}^p$ , shows the delay of the path between the pin p and the endpoint PTL of SCP $_p$ . It is equal to the difference between  $AT_{\text{end}}^{\text{max}}$  and  $AT_p^{\text{max}}$

$$D_{\text{ptl}}^{p} = AT_{\text{end}}^{\text{max}} - AT_{p}^{\text{max}}.$$

(3.5)

The third value of the tuple,  $D_p^{\rm ptl}$ , shows the delay of the path between the start point PTL of the SCP $_p$  and the pin p. It is computed as the difference between  $t_{\rm launch}^{\rm SCP}$  and  $AT_p^{\rm max}$

$$D_p^{\text{ptl}} = AT_p^{\text{max}} - t_{\text{launch}}^{\text{SCP}}.$$

(3.6)

#### 3.1.5 Short-Path Graph

The Short-Path Graph (short-path subgraph (SPG)) is a subgraph of the TG that only contains the pins and edges that belong to short paths, i.e., all those pins p such that  $HS_p < 0$ . Hold violations will be fixed by finding a cut (subset of edges) of the SPG where the NTLs will be inserted.

Two types of edges can be distinguished in the SPG:

$$E = E_{\text{cells}} \cup E_{\text{wires}}$$

whereas  $E_{\text{cells}}$  correspond to those edges that connect input-to-output pins in combinational cells and  $E_{\text{wires}}$  correspond to the remaining edges. The cut of the SPG must be defined using edges in  $E_{\text{wires}}$ .

The insertion of an NTL in an edge may benefit from the presence of an adjacent PTL at the start or end point of the edge. Thus, both latches can be merged into an FF, either PETF (NTL-PTL) or NETF (PTL-NTL), as shown in Fig. 3.1f. Thus, we can define

$$E_{\text{wires}} = E_{\text{ff}} \cup E_{\text{lat}}$$

to distinguish these edges, with  $E_{\rm ff}$  representing the edges in which the merging is possible and  $E_{\rm lat}$  representing the remaining edges. Additionally, two parameters are defined to represent the cost of inserting an NTL,  $c_{\rm ff}$  and  $c_{\rm lat}$ , with  $c_{\rm ff} < c_{\rm lat}$ , since merging implies area savings. For the considered technology, when comparing

28 Methodology

latches and flip-flops with lower fanouts, the ratio of the area  $\frac{A_{lat}}{A_f f}$  is approximately 50%. However, when considering cells with higher fanouts, the ratio significantly increases, reaching around 75% in the worst cases. Additionally, taking into account the extra cells required to route the clock tree of the additional sequential elements and the greater variety of cells available in the flip-flop library, merging appears to be a more favorable choice. These parameters can be tuned to control the area overhead of the solution.

Graph 3.3b shows the SPG of the example circuit from Fig. 3.1b.

| NAME                 | DEFINITION                                                      |

|----------------------|-----------------------------------------------------------------|

| SPG                  | Short-Path Graph                                                |

| T                    | Cycle period                                                    |

| δ                    | Fraction of <i>T</i> to meet setup constraints                  |

| $c_{ m ff}$          | Cost of merging an NTL with a PTL                               |

| $c_{lat}$            | Cost of not merging an NTL ( $c_{\text{lat}} > c_{\text{ff}}$ ) |

| $E_{\mathrm{cells}}$ | Edges between pins of the same cell                             |

| $E_{ m wires}$       | Edges between pins of different cells                           |

| $E_{ m ff}$          | Edges where NTL would be merged in PETF/NETF                    |

| $E_{\text{lat}}$     | Edges where NTL would not be merged                             |

| R(e,X)               | Edge selection value                                            |

|                      |                                                                 |

Table 3.2 Variable definitions for Alg. 3. (ILP Model)

#### 3.1.6 Integer Linear Programming model

Starting from the SPG and the attributes computed from static timing analysis of the PTL post-layout netlist, an ILP model is defined to fix the hold violations and select the NTL locations. Alg. 3 and Tab. 3.2 show the ILP model and the definition of the algorithm variables.

For each pin (p) of the SPG, a binary variable p is created. For each edge (e),  $p_{\text{end}}(e)$  and  $p_{\text{start}}(e)$  represent the variables associated to the endpoint and the start point of e, respectively. Each edge is characterized by the edge selection value, R(e,X), defined as

$$R(e,X) = p_{\text{end}}(e) - p_{\text{start}}(e). \tag{3.13}$$

3.1 Original flow

#### Algorithm 3 Integer linear programming (ILP) Model

**Inputs:** SPG, T,  $\delta$ ,  $c_{\rm ff}$ ,  $c_{\rm lat}$

**Output:** Location of the NTLs (edges with R(e) = 1)

- 1:  $E \leftarrow \text{Edges}(SPG)$

- 2:  $E_{\text{cells}}, E_{\text{wires}}, E_{\text{ff}}, E_{\text{lat}} \leftarrow E$

- 3:  $ESS_p, D_p^{\text{ptl}}, D_{\text{ptl}}^p \leftarrow \text{TimingAttributes}(E)$

minimize

$$c_{\text{lat}} \sum_{\forall e \in E_{\text{lat}}} R(e) + c_{\text{ff}} \sum_{\forall e \in E_{\text{ff}}} R(e)$$

(3.7)

subject to

$$\forall e \in E_{\text{cells}}$$

:  $R(e) = 0$  (3.8)

$$\forall e \in E_{\text{wires}}: \qquad \qquad R(e) \ge 0$$

(3.9)

29

$$\forall e \in E_{\text{wires}}: \qquad \qquad R(e) \cdot ESS_p(e) \ge 0 \qquad (3.10)$$

$$\forall e \in E_{\text{wires}}$$

:  $R(e) \cdot D_{\text{ptl}}^{p}(e) \le \delta \cdot T$  (3.11)

$$\forall e \in E_{\text{wires}}: \qquad \qquad R(e) \cdot D_p^{\text{ptl}}(e) \le \delta \cdot T \qquad (3.12)$$

The cut (location of the NTLs) is defined for those edges with R(e,X) = 1, i.e.,  $p_{\text{start}}(e) = 0$  and  $p_{\text{end}}(e) = 1$ , as shown in Fig. 3.6.

The cost function (3.7) accounts for the number of new sequential elements added to the circuit, i.e., the number of NTLs inserted in edges not connected to a PTL. This will push the solution of Algorithm 3 to use as many NETFs and PETFs as possible to reduce the final number of sequential elements in the circuit.

The constraint (3.8) avoids that Alg.3 selects edges representing connections between pins of the same cells ( $E_{\text{cells}}$ ).

The constraint (3.9) enforces  $p_{\text{end}}(e) \geq p_{\text{start}}(e)$ , because  $p_{\text{end}}(e)$  and  $p_{\text{start}}(e)$  are binary this restricts R(e,X) to be binary. It also implies that all pins p belonging to a path that reaches  $p_{\text{start}}(e)$  will have p=0, while all pins belonging to a path that crosses  $p_{\text{end}}(e)$ , reaches p, and ends at a PTL will have p=1. Then, the algorithm splits the graph in two partitions, before and after the NTLs, by removing the edges with R(e,X)=1. The partition in which all pins have p=1, i.e. the part of the graph that includes the PTL endpoints, will have no early arriving signals. Fig. 3.6 shows an example of the graph partitioning generated by the model.

Although solving an ILP generally has very high runtime, in this particular case it is very close to a max-flow min-cut problem, which is known to have polynomial complexity. This is the likely reason why the runtime of our algorithm remains very small, as shown in Table 4.2, even for designs with tens of thousands of gates and

30 Methodology

Fig. 3.6 Solution example showing the cut chosen for the SPG from Fig. 3.3b. The vertex attributes correspond to the P variables of the ILP model and the edge attributes represent the edge selection value (R(e,X)) computed for each edge. The vertices with input edge attribute equal to 1 are selected for NTL insertion.

FFs. The development of a heuristic algorithm is left to future work, if the execution time becomes excessive, e.g. comparable to or larger than the physical design time.

The constraint (3.10) guides the model towards solutions that do not worsen setup violations, because the  $SS_p$  for each selected edge for NTL insertion must be greater than zero. The purpose of this constraint is to prevent the insertion of a NTL at a location that would introduce delay to a setup critical path. The estimation done in  $ESS_p$  is an approximation of the final  $SS_p$  that takes into account not only the length of the combinational logic delay, but also the clock tree latency generated by the layout tool, as discussed in Section 3.1.4.

However, this is an approximation and we need two more inequalities, (3.11,3.12), to simplify the problem of meeting the setup constraints. The  $D_{\rm ptl}^p$  and  $D_p^{\rm ptl}$  attributes report the distance, in terms of post-layout delay, between each pin p and the source/sink PTLs. An NTL placed in front of p divides the path in two parts and the two graphs give an estimation of the length of these sub-paths. To make these paths as short as possible, these time intervals are constrained to be a fraction  $\delta$  of T, that is a parameter of our algorithm. The value of  $\delta$ , with  $0 < \delta < 1$ , is discussed in the next section.

3.2 Updated flow 31

Fig. 3.7 Example of *Mix & Latch* optimization on a PETFs-based circuit (Fig. 3.7a). Merge sequences of complementary latches: PTL-to-NTL into NETF, NTL-to-PTL into PETF (Fig. 3.7b). Combinational gates have unit delay only for ease of explanation. We consider as short paths those that cross one gate.

## 3.2 Updated flow