### UNIVERSITÀ DEGLI STUDI DELL'AQUILA

### DIPARTIMENTO DI INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE E DI ECONOMIA

### Dottorato di Ricerca in INGEGNERIA INDUSTRIALE E DELL'INFORMAZIONE E DI ECONOMIA

### Curriculum INGEGNERIA ELETTRONICA

XXXII ciclo

Titolo della tesi

# *Discrete and integrated circuits and systems for interfacing differential type capacitive sensors*

SSD ING\_INF/01

Dottorando

### GIANLUCA BARILE

Coordinatore del corso

Tutor

Prof. Giuseppe Ferri

Prof. Giuseppe Ferri

A.A. 2018/2019

This page is left blank intentionally

This page is left blank intentionally

### **SUMMARY**

In a reality where integrated and highly autonomous systems are adopted in any area of everyday life, great efforts are spent in the research and industrial environments so to design systems able to harvest energy from the environment around them and, in general, to maintain a very high efficiency level across all their possible working conditions. As a matter of fact, measurement subsystems (which are ubiquitous in any application field) play a significant role in this regard since, on one hand the transducer almost inevitably needs a power source to convert the measurand, and, on the other hand, being the electronic interface necessarily analog, it does not gain benefits, in terms of power consumption, from the simple technological scaling, as instead does the processing part of the complex system, typically digital. That said, on one hand it makes sense to use transducers which, by their nature, guarantee a very low power consumption and, on the other, it is worth carrying out research aimed at designing interfacing circuits that maximize readout performances avoiding spoiling the aforementioned constraints. In light of this, capacitive sensors have established in many applications, replacing the piezoresistive counterparts, since they consume virtually zero in terms of dissipated power, while not giving up in terms of robustness to temperature variations and sensitivity.

The doctoral dissertation proposed here, entitled "*Discrete and integrated circuits and systems for interfacing differential type capacitive sensors*", focuses on showing the state of the art and the development of new circuit and systems for the readout of differential capacitive sensors. Being a subset of the capacitive ones, this type of sensors has their same advantages while being inherently excellent at rejecting common mode disturbances.

The first chapter of the thesis is focused on an introduction to standard and differential capacitive sensors, characterizing them from a physical and electronic (circuit) point of view. The corresponding analytical parameterization of this type of sensor is also treated, based on the physical nature of the sensor, offering insights on the advantages and disadvantages of the various alternatives. The following chapter offers, instead, a review on the state of the art, both in terms of interface

architectures and in terms of building block used to implement them. In particular, this chapter is focused on the voltage mode approach. Indeed, there are several alternatives, among which the most common is represented by switched capacitor architectures whose operations, simplifying, depend on the status of a number of internal switches. By changing their status it is possible to perform a sequence of steps which eventually lead to the actual measurement. These interfaces, although effective, suffer from various relevant problems related to the non-ideality of the switches themselves (clock feedthrough and charge injection). In fact, there are "switchless" interfaces, typically based on oscillators, capable of adjusting the frequency (or duty cycle) of the output signal according to the value of the transducer. The limit of these proposals is linked, in particular, to the stability of the oscillator itself and to the almost inevitable mismatch between the passive components that constitute the circuit. Other alternatives are also analysed, comparing them between each other.

The third chapter introduces all the voltage mode readout techniques and circuits for interfacing differential capacitive sensors, derived from the research conducted during the three year doctorate. The innovation factor in this sense lies both in the methodology and in the design of ad hoc discrete and integrated architectures: after a brief introduction on the concepts of synchronous demodulation and self-balanced bridge, it is shown how these have been effectively used for the objectives listed above, and how, thanks to them, it is possible to overcome some limitations of the classic proposals. The designed circuits and the results coming from the simulations and the measurement of the same circuits are then shown, offering an in-depth comparison with the literature. In the second part of the same chapter, a possible methodology, translated into a circuit, to compensate capacitive parasitic elements, is also given. In particular, being it independent from the interface, it is shown how it has been retrofitted to the circuits developed along the chapter.

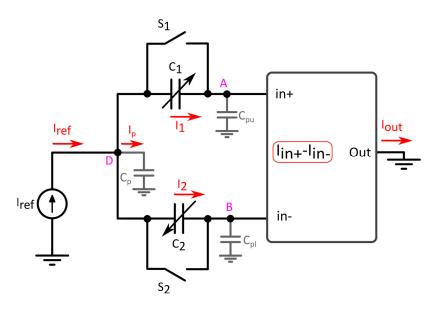

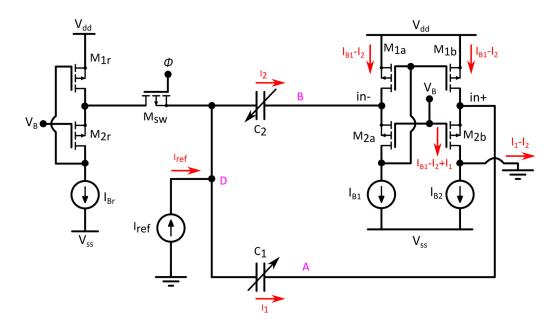

The fourth chapter gives an insight into the status of the art about current mode techniques to evaluate differential capacitance transducers. Unlike the voltage mode approach, the literature, in this topic, is rather standardized, in other words, all proposals are based on a well-defined theory. Although, indeed, encapsulating information in a current has numerous advantages over a purely voltage mode signaling, making it possible to obtain extremely simple architectures, allowing high speed readings and high sensitivity values, at a very low power consumption, it has also crucial drawbacks. In fact, a current mode interface results extremely sensitive to the non-idealities of the sensor and of the electronics itself (parasitic capacitances and offset of the amplifiers). Moreover, the voltage across a capacitor, under the action of a constant reference current, tends to linearly increase, making it necessary for the designer to find a way to periodically discharge it. On these weaknesses, the research work elaborated in the following chapter is justified.

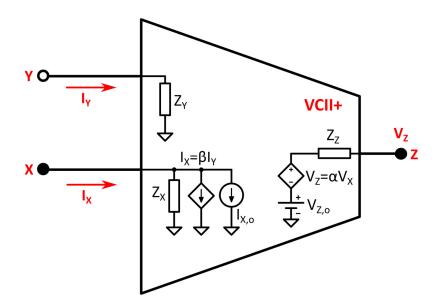

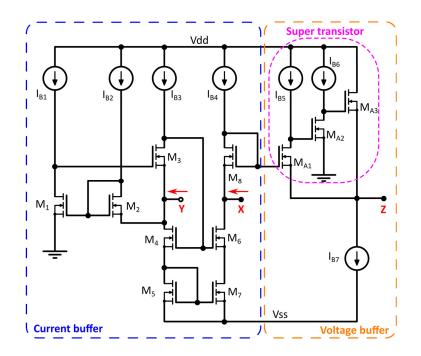

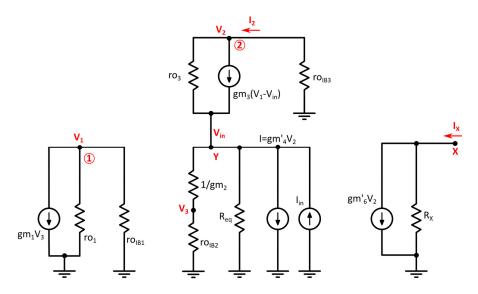

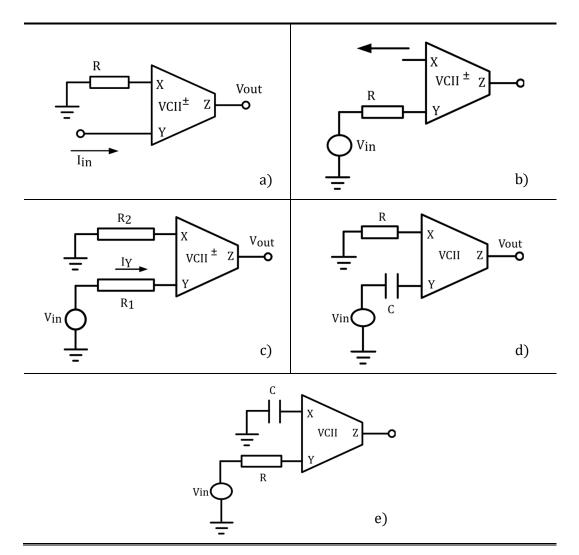

In the fifth chapter, we therefore propose a novel circuit developed for interfacing differential capacitive sensors with a current mode approach. The research in this direction has been twofold: on one hand we have developed an interface circuit which is capable of dynamically eliminate the effects of stray capacitances, on the other, for the first time, we have taken advantage of the benefits coming from a totally new building block, the second generation voltage conveyor (VCII). The theoretical analysis as well as all the measurements conducted on a prototype are shown in the chapter.

In the sixth and last chapter of this thesis we report our contributions on the topic of integrated active blocks that can be profitably employed as building elements for interface circuits and systems. In particular, in the first half of the chapter, after a short literature review, we propose two novel architectures to implement advanced second generation current conveyors (CCIIs). Similarly, in the second half of the chapter we propose many novel topologies to synthesize the aforementioned VCII. Each of the proposals is thoroughly analysed from a theoretical point of view. Simulation results are also given.

A short discussion summarizing the main achievements is given at the end of each paragraph.

v

### **ACKNOWLEDGEMENTS**

Firstly, I would like to express my sincere gratitude to my supervisor Prof. Giuseppe Ferri for his unconditional support that started from the bachelor's degree thesis, through the master's degree one and culminated with my Ph.D. study. I would like to thank Him for his knowledge and for the invaluable motivation that brought me to undertake such a complicated yet rewarding path. His guidance led me in all the time of research and writing of this dissertation.

I would like to thank Prof. Vincenzo Stornelli for His friendly help and for His overflowing enthusiasm that inspired me to expand my knowledge even beyond the topics of my Ph.D. study.

Thank you to Prof. Leonardo Pantoli, whose help and advices have been so precious. His professionalism and seriousness made Him a point of reference to me.

A very special thanks goes to my friends and colleagues Dr. Alfiero Leoni and Dr. Mirco Muttillo with whom I've been so lucky to share this journey. Our talks made even the most intricate problems simple and enjoyable to solve.

### CONTENTS

| 1  | INTRODUCTION                                                             | 20        |

|----|--------------------------------------------------------------------------|-----------|

|    | 1.1 Sensors: A brief review                                              |           |

|    | 1.2 CAPACITIVE SENSORS                                                   |           |

|    | 1.2.1 Physical properties                                                |           |

|    | 1.2.2 Basic interfaces for capacitive sensors                            | 25        |

|    | 1.3 DIFFERENTIAL CAPACITIVE SENSORS                                      |           |

|    | 1.3.1 Physical properties                                                | 29        |

|    | 1.3.2 Parametrization                                                    |           |

|    | 1.3.3 Basic interfaces for differential capacitive sensors               |           |

|    | 1.3.4 Considerations on parasitic capacitances                           |           |

| 2  | VOLTAGE MODE DIFFERENTIAL CAPACITIVE SENSOR INTERFACES: ST               | TATE OF   |

| Τł | HE ART                                                                   |           |

|    | 2.1 Step measurement                                                     |           |

|    | 2.2 Switchless capacitance to time converter                             |           |

|    | 2.3 Switchless capacitance to voltage converters                         | 55        |

|    | 2.4 CAPACITANCE TO DIGITAL INTERFACES                                    | 60        |

| 3  | AUTOBALANCED BRIDGE, SYNCHRONOUS DEMODULATION                            | BASED     |

| D  | IFFERENTIAL CAPACITIVE SENSOR INTERFACES                                 | 65        |

|    | 3.1 The autobalanced bridge                                              |           |

|    | 3.2 Non-linear output interface                                          |           |

|    | 3.2.1 Discrete version                                                   | 69        |

|    | 3.2.2 Integrated version                                                 |           |

|    | 3.2.3 Discussion                                                         |           |

|    | 3.3 LINEAR OUTPUT INTERFACE                                              |           |

|    | 3.3.1 Discrete version                                                   |           |

|    | 3.3.2 Integrated version                                                 |           |

|    | 3.3.3 Discussion                                                         |           |

|    | 3.4 PARASITIC COMPENSATION IN AUTOBALANCED BRIDGE DIFFERENTIAL CAPACITIV | 'E SENSOR |

|    | INTERFACES                                                               | 109       |

| 3.4.1 Theory of operation                              |              |

|--------------------------------------------------------|--------------|

| 3.4.2 Simulation results                               |              |

| 3.4.3 Measurement results                              |              |

| 3.4.4 Discussion                                       |              |

| 4 CURRENT MODE DIFFERENTIAL CAPACITIVE SENSOR INTERFAC | ES: STATE OF |

| THE ART                                                |              |

| 4.1 Current mode theory                                |              |

| 4.2 STANDARD DEVICE INTERFACES                         | 129          |

| 4.3 CCII based interfaces                              | 135          |

| 5 VCII BASED STRAY INSENSITIVE INTERFACE               |              |

| 5.1 INTRODUCTION ON THE VCII                           | 138          |

| 5.2 THEORY OF OPERATION                                | 139          |

| 5.3 SIMULATION RESULTS AND MEASUREMENTS                | 142          |

| 5.4 DISCUSSION                                         | 153          |

| 6 SECOND GENERATION CURRENT AND VOLTAGE CONVEYORS      |              |

| 6.1 Second generation current conveyors                | 154          |

| 6.1.1 Introduction                                     |              |

| 6.1.2 CCII non-idealities                              |              |

| 6.1.3 Differential pair based CCIIs                    |              |

| 6.1.4 Rail to Rail Differential Pair based CCII        |              |

| 6.1.5 Adaptively-biased differential pair based CCII   |              |

| 6.2 Second generation Voltage conveyor                 | 178          |

| 6.2.1 Introduction                                     |              |

| 6.2.2 VCII non-idealities                              |              |

| 6.2.3 Super transistor based VCII                      |              |

| 6.2.4 Flipped Voltage Follower based VCII              |              |

| 6.2.5 Class AB high drive capable VCII                 |              |

| 6.2.6 Rail to rail VCII                                |              |

| 7 REFERENCES                                           |              |

## LIST OF TABLES

| TABLE I COMPARISON TABLE                                                                                                                                                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TABLE II OTA TRANSISTOR DIMENSIONS                                                                                                                                                                    |  |

| TABLE III AMPLIFIER PARAMETERS.   77                                                                                                                                                                  |  |

| TABLE IV MULTIPLIER TRANSISTOR DIMENSIONS AND PARAMETER VALUES                                                                                                                                        |  |

| TABLE V COMPARISON TABLE   82                                                                                                                                                                         |  |

| TABLE VI EXPERIMENTAL EVALUATION OF THE CUTOFF ANGULAR FREQUENCY (RAD/S) ( $C = 2$ NF,<br>$R = 200 \text{ K}\Omega$ )                                                                                 |  |

| Table VII experimental evaluation of the cutoff angular frequency (rad/s) (C = 2 NF, R = 20 K\Omega)                                                                                                  |  |

| TABLE VIII COMPARISON TABLE                                                                                                                                                                           |  |

| TABLE IX OTA TRANSISTOR DIMENSIONS AND FEATURES HIGHLIGHT                                                                                                                                             |  |

| TABLE X MULTIPLIER TRANSISTOR DIMENSIONS AND FEATURES HIGHLIGHT                                                                                                                                       |  |

| TABLE XI COMPARISON BETWEEN SIMULATED AND THEORETICAL INPUT/OUTPUT CHARACTERISTIC         OF THE INTERFACE.         104                                                                               |  |

| TABLE XII MAIN COMPENSATION TECHNIQUES COMPARISON    113                                                                                                                                              |  |

| TABLE XIII SIMULATED RESULTS COMPARING IDEAL, COMPENSATED AND UNCOMPENSATED VB VOLTAGE. SENSOR BASELINE IS EQUAL TO 10 PF, PARASITIC CAPACITANCE TO 6.25 PF 116                                       |  |

| Table XIV Performance of the proposed compensation circuit with NIC feedback capacitor $C_{\text{NIC}}=20$ pF; estimated baseline stray capacitance is $C_{\text{PO}}\approx31.9$ pF 121              |  |

| Table XV Performance of the proposed compensation circuit with NIC feedback capacitor $C_{\text{Nic}}=47$ pF; estimated baseline stray capacitance is $C_{\text{P0}}\approx 29.9$ pF 121              |  |

| TABLE XVI RELATIVE LINEARITY ERROR OF THE READOUT SYSTEM INCLUDING THE STRAY         CAPACITANCE COMPENSATION.       LINEARIZATION IS PERFORMED ON THE SYSTEM WITHOUT         COMPENSATION.       123 |  |

| TABLE XVII RELATIVE LINEARITY ERROR OF THE READOUT SYSTEM INCLUDING THE STRAY<br>CAPACITANCE COMPENSATION. LINEARIZATION IS PERFORMED ON THE SYSTEM WITH                                              |  |

| TABLE XVIII THE USED VCII PARAMETERS.                                                                 | 144 |

|-------------------------------------------------------------------------------------------------------|-----|

| TABLE XIX COMPARISON TABLE                                                                            | 152 |

| TABLE XX TRANSISTOR VALUES OF THE IMPLEMENTED IA (BOTH CCIIS ARE EQUAL)                               |     |

| TABLE XXI IA MAIN PERFORMANCE AND COMPARISON.                                                         |     |

| TABLE XXII TRANSISTORS SIZES OF THE DYNAMIC BIASED CIRCUIT                                            | 171 |

| TABLE XXIII TRANSISTORS SIZES OF THE CCII MAIN CIRCUIT                                                |     |

| TABLE XXIV NODE IMPEDANCE PARASITIC VALUES                                                            | 177 |

| TABLE XXV COMPARISON BETWEEN THE DB-CCII CHARACTERISTICS AND THOSE OF         WITHOUT DYNAMIC BIASING |     |

| TABLE XXVI TRANSISTORS ASPECT RATIOS.                                                                 |     |

| TABLE XXVII THE VALUE OF CURRENT SOURCES.                                                             |     |

| TABLE XXVIII THE PROPOSED VCII PERFORMANCE PARAMETERS                                                 |     |

| TABLE XXIX TRANSISTORS ASPECT RATIOS                                                                  |     |

| TABLE XXX VCII PERFORMANCE PARAMETERS                                                                 |     |

| TABLE XXXI TRANSISTORS ASPECT RATIOS                                                                  | 202 |

| TABLE XXXII TRANSISTOR DIMENSIONS AND PARAMETER VALUES                                                | 208 |

| TABLE XXXIII THE PROPOSED VCII PERFORMANCE PARAMETERS                                                 | 213 |

# LIST OF FIGURES

| FIGURE 1.1 A) SINGLE TRANSDUCER SENSOR, B) MULTIPLE TRANSDUCER PLUS INTERFACE SENSOR. |

|---------------------------------------------------------------------------------------|

|                                                                                       |

| FIGURE 1.2 A PARALLEL PLATES CAPACITIVE SENSOR CONFIGURATION                          |

| Figure 1.3 Three different use cases for a parallel plates capacitive sensor: a)      |

| DISTANCE VARIATIONS; B) OVERLAPPING SURFACE VARIATIONS; C) DIELECTRIC CONSTANT        |

| VARIATION24                                                                           |

| FIGURE 1.4 DC READOUT TECHNIQUE                                                       |

| FIGURE 1.5 RC OSCILLATOR BASED READOUT INTERFACE                                      |

| FIGURE 1.6 SINGLE-ENDED SYNCHRONOUS DEMODULATION TECHNIQUE APPLIED TO CAPACITIVE      |

| SENSING                                                                               |

| FIGURE 1.7 FULLY DIFFERENTIAL SYNCHRONOUS DEMODULATION TECHNIQUE                      |

| FIGURE 1.8 IDEAL EQUIVALENT MODEL FOR A DIFFERENTIAL CAPACITANCE SENSOR               |

| FIGURE 1.9 A LINEAR DIFFERENTIAL CAPACITIVE SENSOR                                    |

| FIGURE 1.10 A HYPERBOLIC DIFFERENTIAL CAPACITIVE SENSOR                               |

| Figure 1.11 Definition of the sign of x according to the sensor type: A) linear; B)   |

| HYPERBOLIC                                                                            |

| FIGURE 1.12 OSCILLATOR BASED DIFFERENTIAL CAPACITIVE SENSOR INTERFACE A) FOR LINEAR   |

| SENSORS; B) FOR HYPERBOLIC SENSORS                                                    |

| FIGURE 1.13 DIFFERENTIAL CAPACITIVE SENSORS ASYNCHRONOUS DEMODULATION READOUT: A)     |

| SINGLE-ENDED; B) FULLY DIFFERENTIAL                                                   |

| FIGURE 1.14 REAL-WORLD DIFFERENTIAL CAPACITIVE SENSOR EQUIVALENT MODEL: A) GENERIC,   |

| B) DRIVEN BY AN AC SOURCE                                                             |

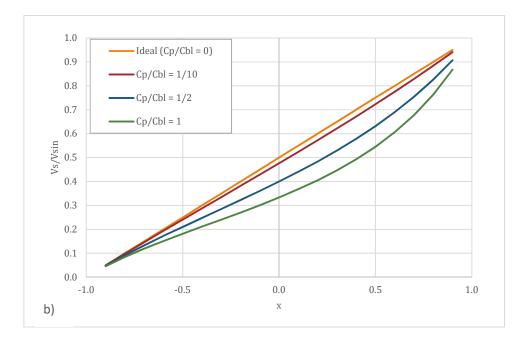

| FIGURE 1.15 EFFECTS OF CP ON THE READOUT OF A) LINEAR SENSORS, B) HYPERBOLIC SENSORS. |

|                                                                                       |

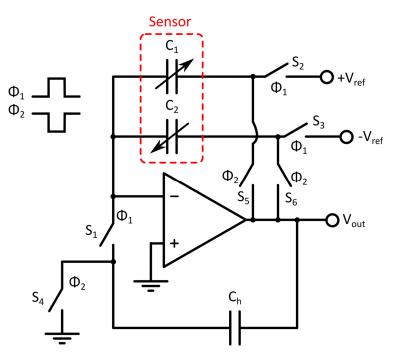

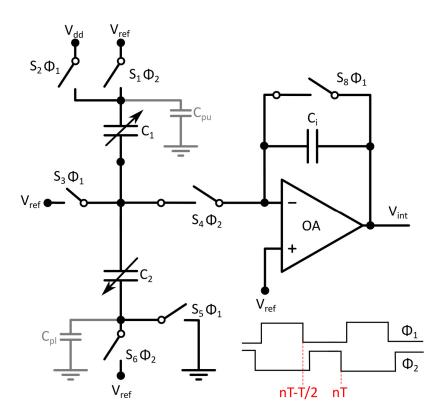

| FIGURE 2.1 SAMPLE AND HOLD BASED INTERFACE [13]                                       |

| FIGURE 2.2 SWITCHED CAPACITOR OSCILLATOR BASED C TO V INTERFACE [16]                  |

| Figure 2.3 Interface behavior when $C_1 > C_2 [16]$ 44                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

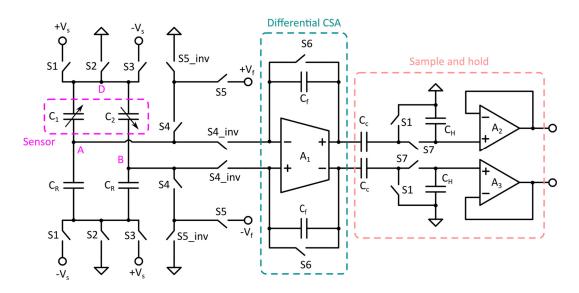

| FIGURE 2.4 SWITCHED CAPACITOR CSA INTERFACE WITH PARASITIC CANCELLATION [17]46                                                                                          |

| FIGURE 2.5 FULLY DIFFERENTIAL SWITCHED CAPACITOR CSA INTERFACE [19]47                                                                                                   |

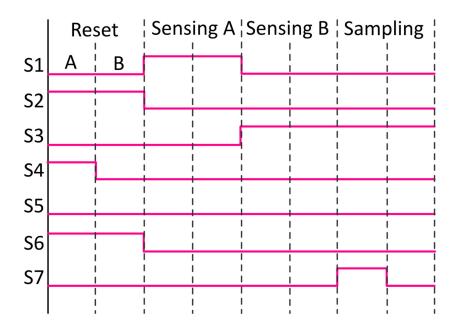

| FIGURE 2.6 SWITCHES STATUS OF THE ANALYSED INTERFACE ACCORDING TO THE RELATIVE PHASE<br>OF THE READOUT [19]                                                             |

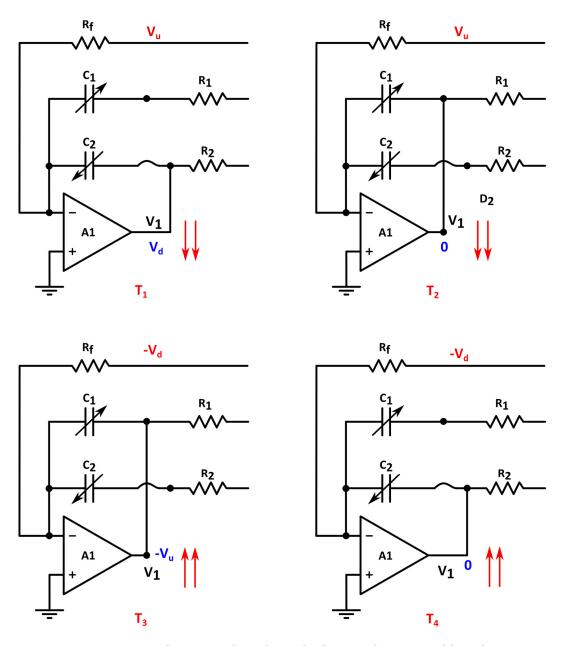

| FIGURE 2.7 CAPACITANCE TO TIME RELAXATION OSCILLATOR BASED INTERFACE [21]50                                                                                             |

| Figure 2.8 Circuit configuration based on diodes conditions: in blue the starting condition for V1, the red arrows show the tendency of V1 during each phase. $51$      |

| FIGURE 2.9 TIME DOMAIN BEHAVIOR OF THE INTERFACE SIGNALS [21]                                                                                                           |

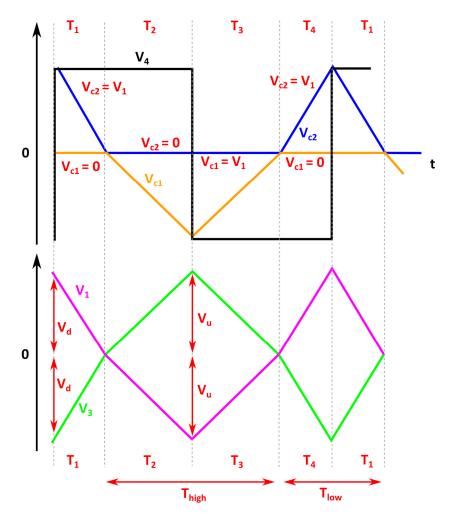

| FIGURE 2.10 MULTIPLE FEEDBACK C TO T INTERFACE [22]53                                                                                                                   |

| FIGURE 2.11 TIME DOMAIN BEHAVIOR OF THE ANALYZED INTERFACE (VCOMP1 AND VCOMP2 SUITABLY SCALED FOR A BETTER VIEW) [22]                                                   |

| FIGURE 2.12 RELAXATION OSCILLATOR BASED C TO V INTERFACE [23]55                                                                                                         |

| FIGURE 2.13 TIME DOMAIN BEHAVIOR OF THE ANALYZED INTERFACE [23]                                                                                                         |

| FIGURE 2.14 SYNCHRONOUS DEMODULATION C TO V INTERFACE IN OPEN LOOP CONDITIONS [25]                                                                                      |

| FIGURE 2.15 SYNCHRONOUS DEMODULATION C TO V INTERFACE IN CLOSED LOOP CONDITIONS [25]                                                                                    |

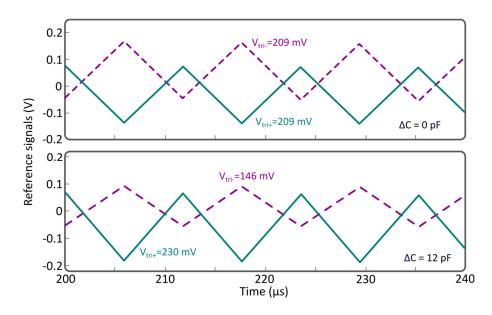

| FIGURE 2.16 DIFFERENCE BETWEEN EXCITING WAVES DURING AN OPEN LOOP (TOP) AND CLOSED LOOP (BOTTOM) OPERATION, SUPPOSING THAT C1 IS GREATER THAN C2 [25]59                 |

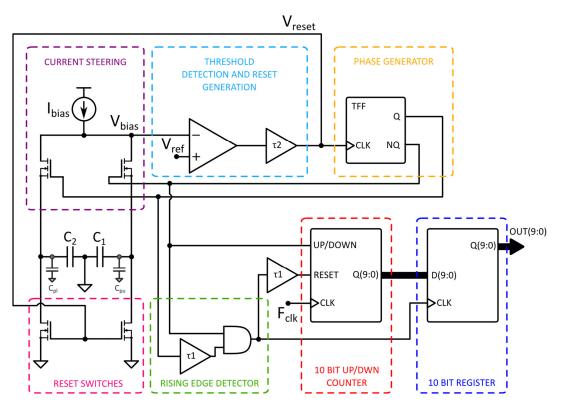

| FIGURE 2.17 CAPACITANCE TO DIGITAL INTERFACE USING A DIGITAL COUNTER [26]60                                                                                             |

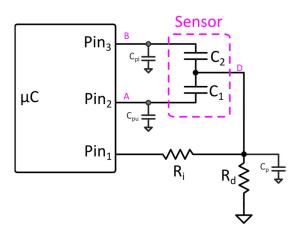

| FIGURE 2.18 DIRECT MICROCONTROLLER-BASED INTERFACE [27].                                                                                                                |

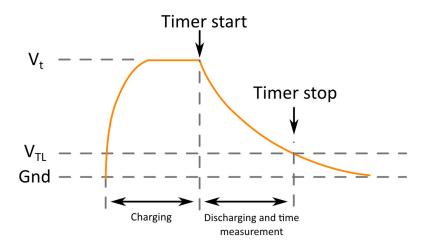

| FIGURE 2.19 VOLTAGE AT NODE 1 DURING THE CHARGE AND DISCHARGE PHASES [27]62                                                                                             |

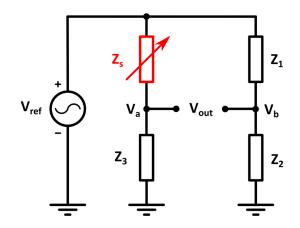

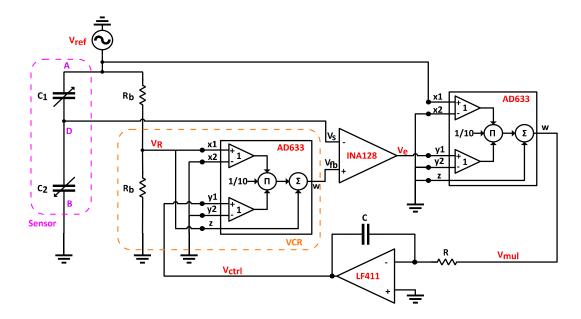

| FIGURE 3.1 GENERIC IMPEDANCE BRIDGE                                                                                                                                     |

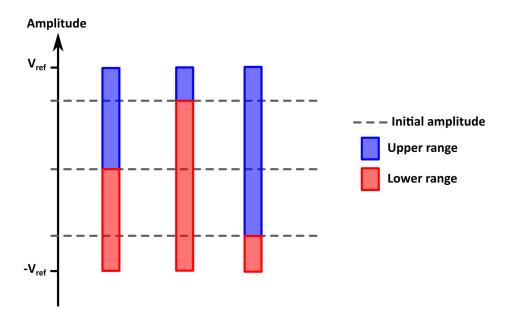

| FIGURE 3.2 DYNAMIC RANGES AVAILABLE AT DIFFERENT VALUES OF IMPEDANCES: ALL EQUAL VALUE (LEFT); Z3 <zs (center);="" and="" z2<z1="" z3="">ZS AND Z2&gt;Z1 (RIGHT)67</zs> |

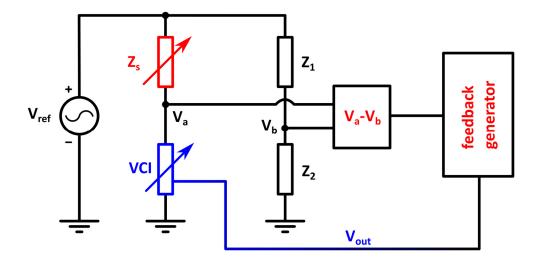

| FIGURE 3.3 BLOCK DIAGRAM OF AN AUTOBALANCED BRIDGE                                                                                                                      |

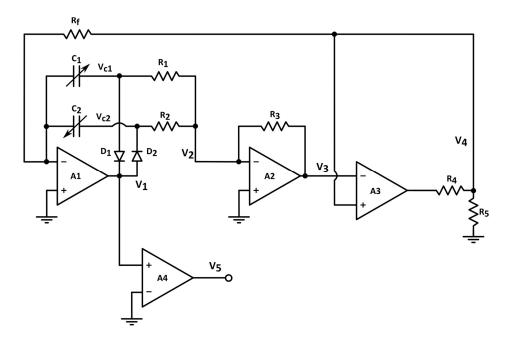

| FIGURE 3.4 AUTOBALANCED BRIDGE INTERFACE PROPOSED IN [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

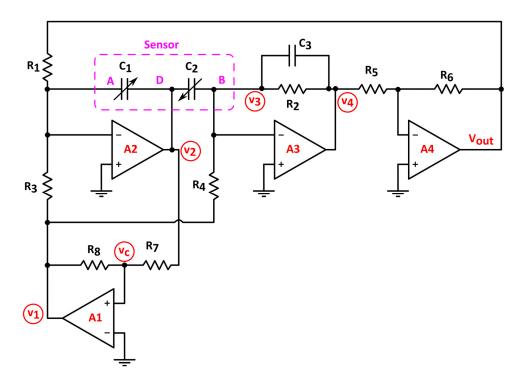

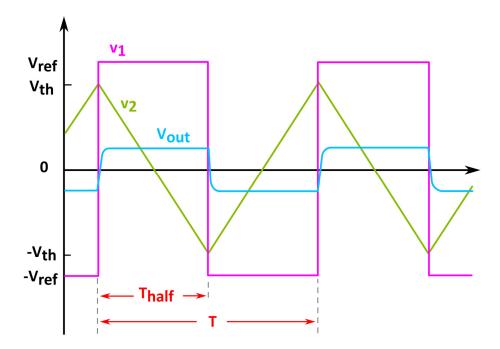

| FIGURE 3.5 CIRCUITAL DIAGRAM OF THE INTERFACE ANALYSED IN [35]70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

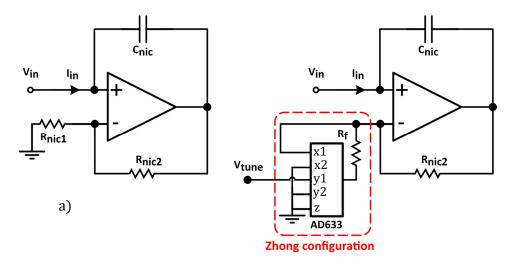

| FIGURE 3.6 VCR IMPLEMENTED BY MEANS OF A ZHONG CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

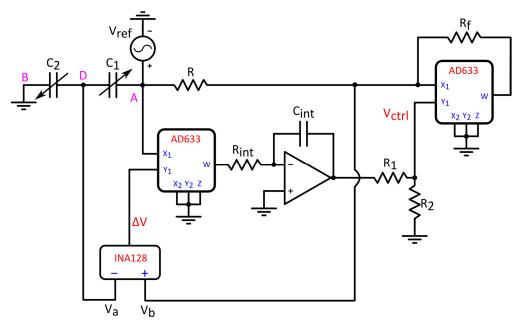

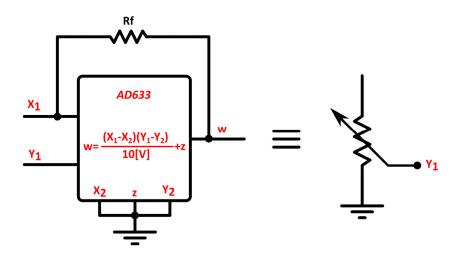

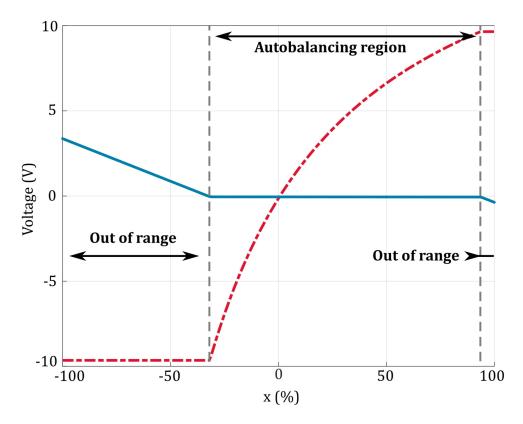

| Figure 3.7 VCTRL and $\Delta V$ behaviors vs x: simulated results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

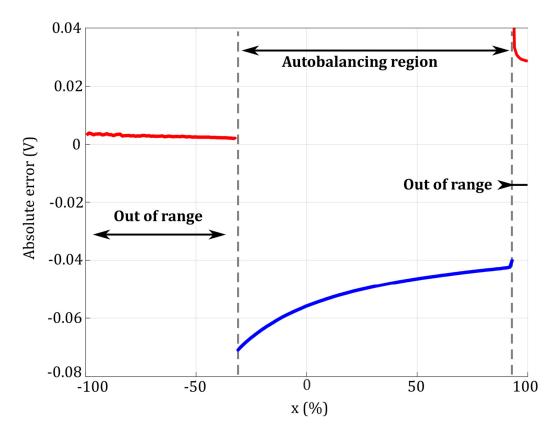

| FIGURE 3.8 ABSOLUTE ERROR IN "AUTOBALANCING" INTERVAL AND "OUT-OF-RANGE" VS. X%:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| THEORETICAL VS. SIMULATED RESULTS73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

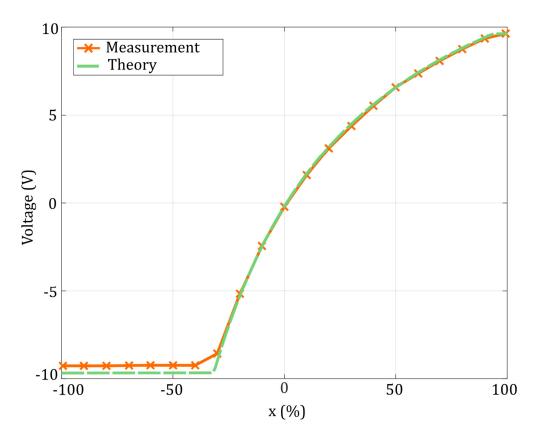

| FIGURE 3.9 VCTRL BEHAVIOR VS X: THEORETICAL AND EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 3.10 Percentage relative error vs. x: theoretical vs. experimental results .74 $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIGURE 3.11 USING A MOSFETS IN LINEAR REGION AS A VCR [42]76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

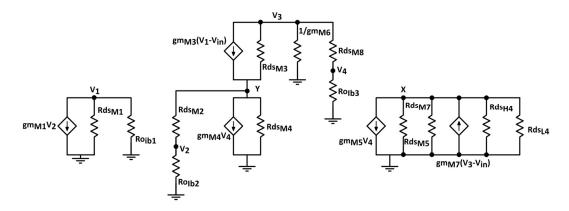

| FIGURE 3.12 DUAL STAGE, SYMMETRICAL OPERATIONAL TRANSCONDUCTANCE AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

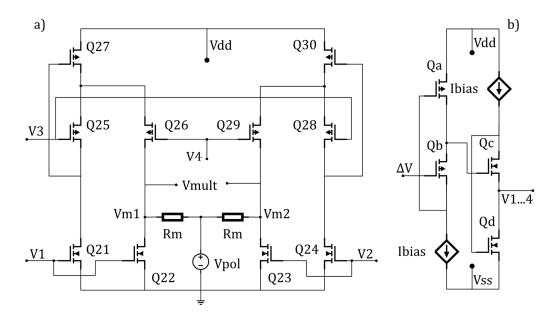

| FIGURE 3.13 A) MULTIPLIER CORE, B) MULTIPLIER BIASING CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FIGURE 3.14 SIMULATED EQUIVALENT RESISTANCES VS. LINEAR REGION RDS THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

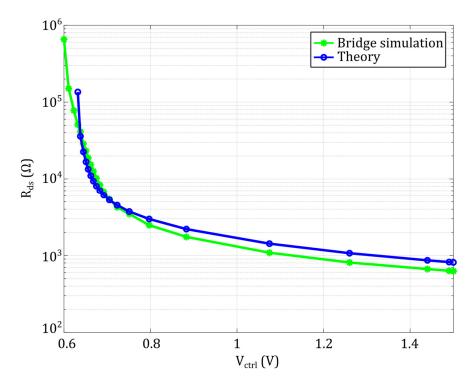

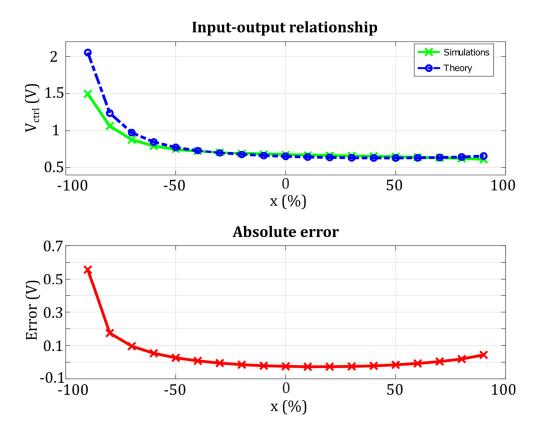

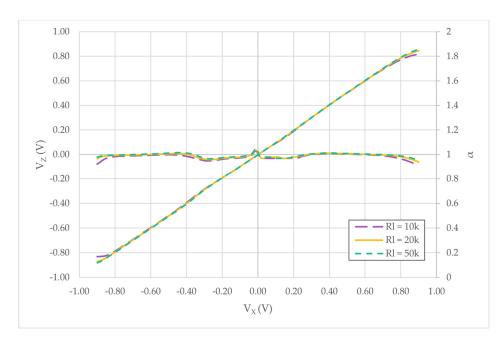

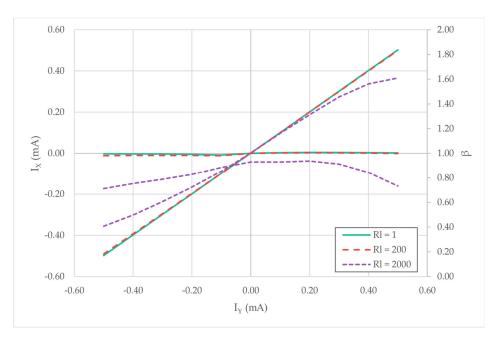

| FIGURE 3.15 INTERFACE STATIC PERFORMANCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

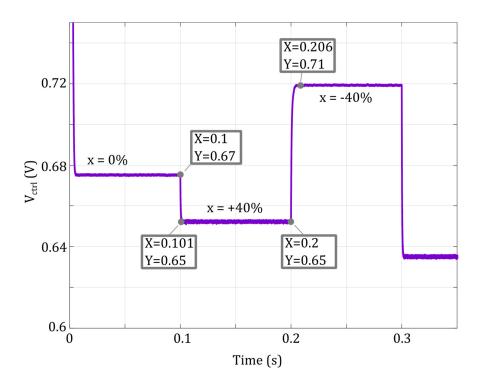

| FIGURE 3.16 INTERFACE DYNAMIC PERFORMANCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FIGURE 3.16 INTERFACE DYNAMIC PERFORMANCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

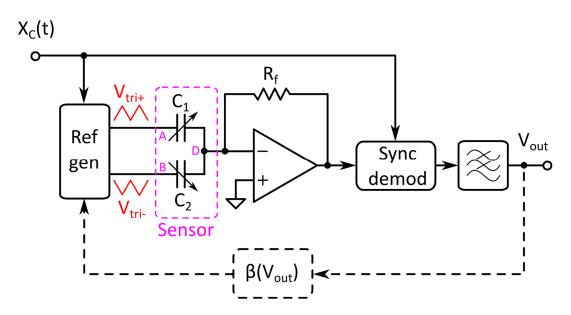

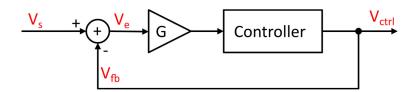

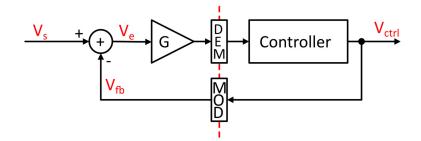

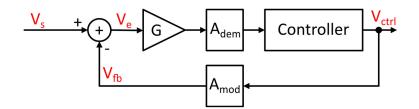

| FIGURE 3.17 SCHEMATIC REPRESENTATION OF THE GENERIC AUTOBALANCING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIGURE 3.17 SCHEMATIC REPRESENTATION OF THE GENERIC AUTOBALANCING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 3.17 Schematic representation of the generic autobalancing system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIGURE 3.17 SCHEMATIC REPRESENTATION OF THE GENERIC AUTOBALANCING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FIGURE 3.17 SCHEMATIC REPRESENTATION OF THE GENERIC AUTOBALANCING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

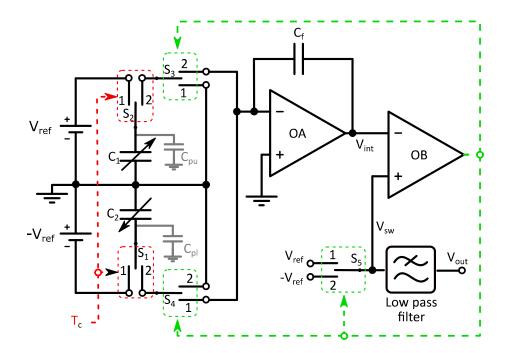

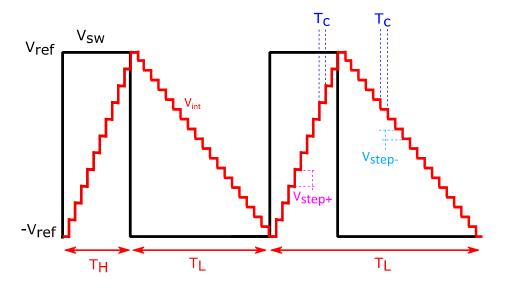

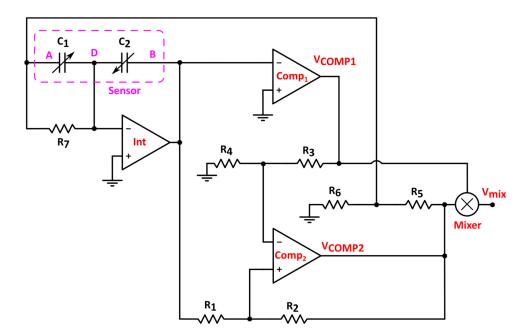

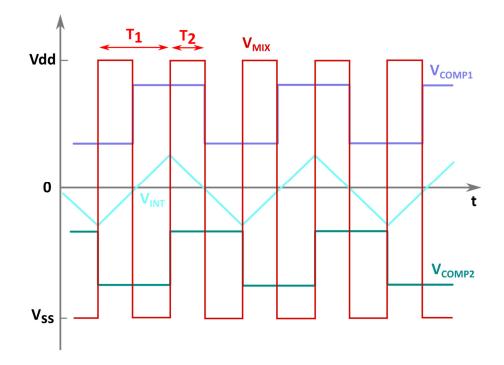

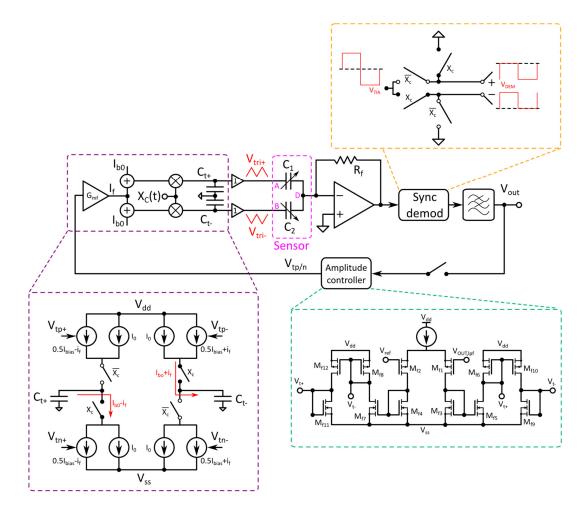

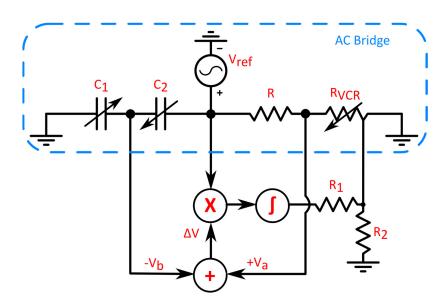

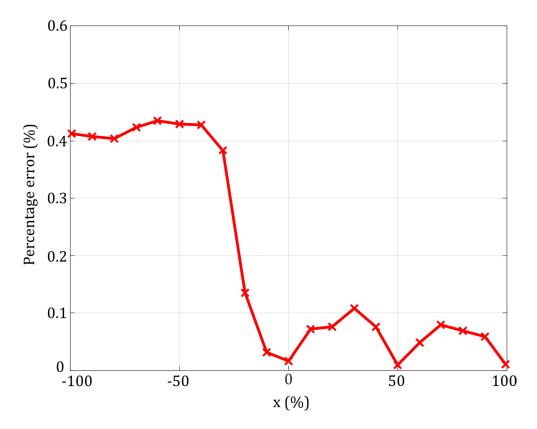

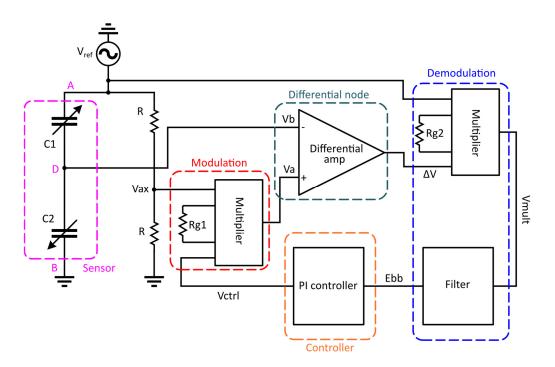

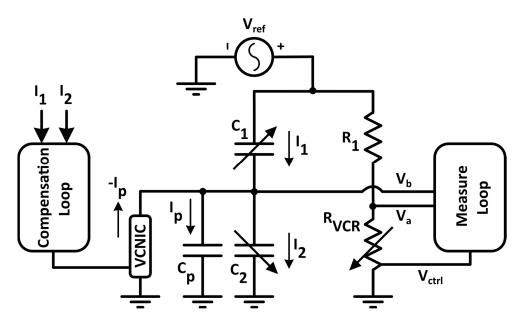

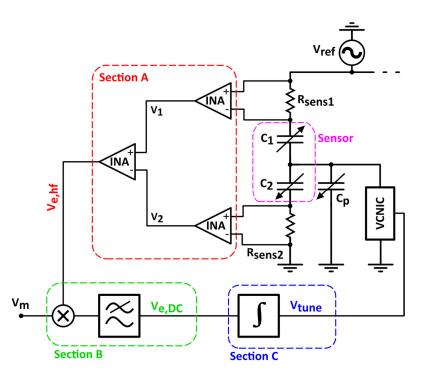

| Figure 3.17 Schematic representation of the generic autobalancing system.       84         Figure 3.18 Schematic representation of the baseband vs bandpass signals in the interface analysed in [48].       84         Figure 3.19 Simplification of the analysed interface feedback circuit in the time domain.       84         Figure 3.20 Schematic diagram of the proposed interface.       85                                                                                                                                                                                |

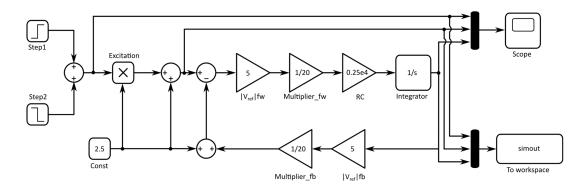

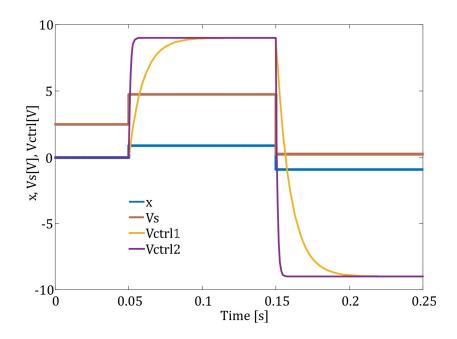

| Figure 3.17 Schematic representation of the generic autobalancing system.       84         Figure 3.18 Schematic representation of the baseband vs bandpass signals in the interface analysed in [48].       84         Figure 3.19 Simplification of the analysed interface feedback circuit in the time domain.       84         Figure 3.20 Schematic diagram of the proposed interface.       85         Figure 3.21 Simulink model of the proposed system.       87                                                                                                            |

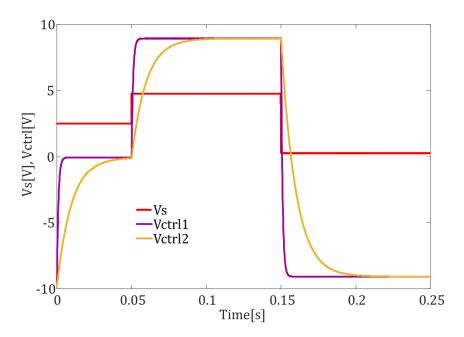

| Figure 3.17 Schematic representation of the generic autobalancing system.       84         Figure 3.18 Schematic representation of the baseband vs bandpass signals in the interface analysed in [48].       84         Figure 3.19 Simplification of the analysed interface feedback circuit in the time domain.       84         Figure 3.20 Schematic diagram of the proposed interface.       85         Figure 3.21 Simulink model of the proposed system.       87         Figure 3.22 Simulink simulation results for different cutoff frequency (V <sub>ctrrl1</sub> @ Ωco1 |

| Figure 3.17 Schematic representation of the generic autobalancing system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 3.17 Schematic representation of the generic autobalancing system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

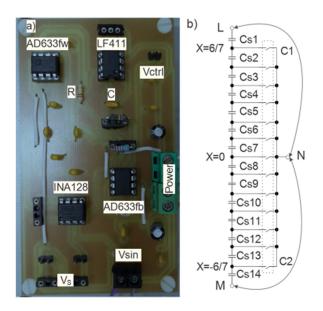

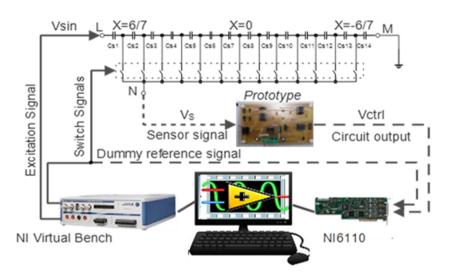

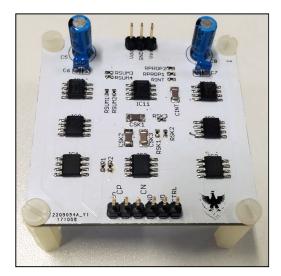

| FIGURE 3.24 A) THE PCB OF THE REALIZED PROTOTYPE. B) THE DIFFERENTIAL CAPACITIVE                |

|-------------------------------------------------------------------------------------------------|

| SENSOR EMULATOR; L, M AND N REFERS TO THE SCHEME IN FIG. $1.11$ B89                             |

| FIGURE 3.25 THE EXPERIMENTAL SETUP90                                                            |

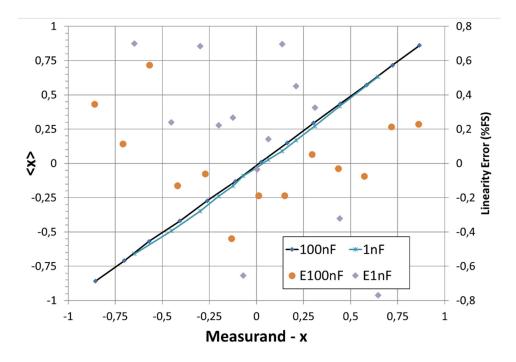

| Figure $3.26$ The calibration curve and the linearity error for extreme values of the           |

| $C_s \in [1, 100]$ NF. Linearity errors for other Cs values are in the between91                |

| FIGURE 3.27 SCHEMATIC DIAGRAM OF THE INTERFACE PROPOSED IN [49]94                               |

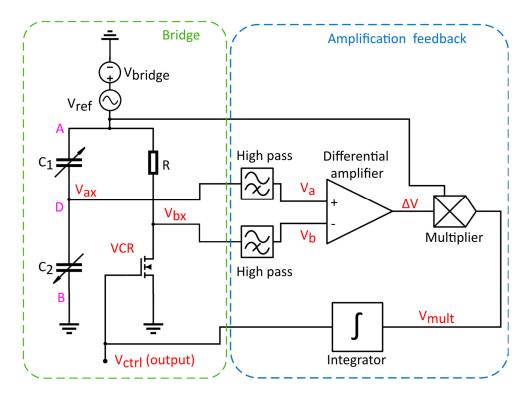

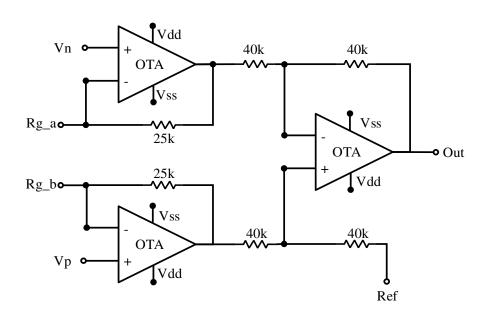

| FIGURE 3.28 OPERATIONAL TRANSCONDUCTANCE AMPLIFIER SCHEMATIC. FROM THE LEFT: THE                |

| BIASING CURRENT MIRROR, THE SYMMETRICAL OTA AS INPUT STAGE, THE CASCODED INVERTER AS GAIN STAGE |

| FIGURE 3.29 INSTRUMENTATION AMPLIFIER SETUP                                                     |

| FIGURE 3.30 MULTIPLIER SCHEMATIC: DASHED BLUE LINE HIGHLIGHTS THE BIASING CIRCUITS,             |

| DASHED RED LINE HIGHLIGHTS THE MULTIPLIER CORE, DASHED ORANGE LINE HIGHLIGHTS THE               |

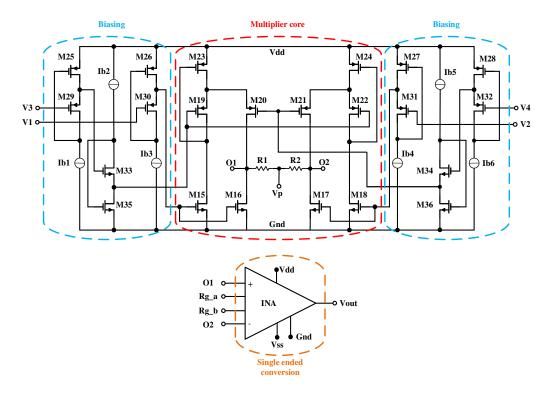

| OUTPUT STAGE WHICH TAKES $01$ and $02$ as inputs and performs the subtraction99                 |

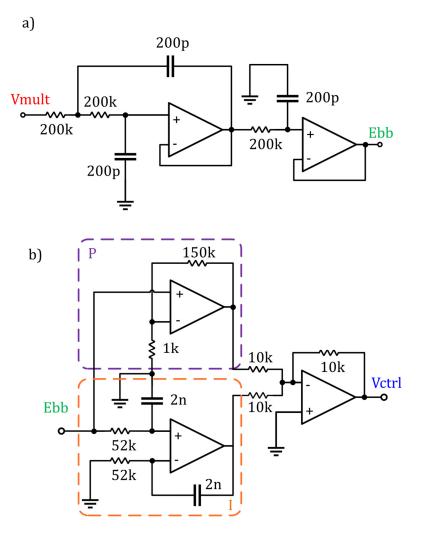

| FIGURE 3.31 A) DEMODULATION FILTER SCHEMATIC, B) PROPORTIONAL AND INTEGRAL                      |

| CONTROLLER SCHEMATIC                                                                            |

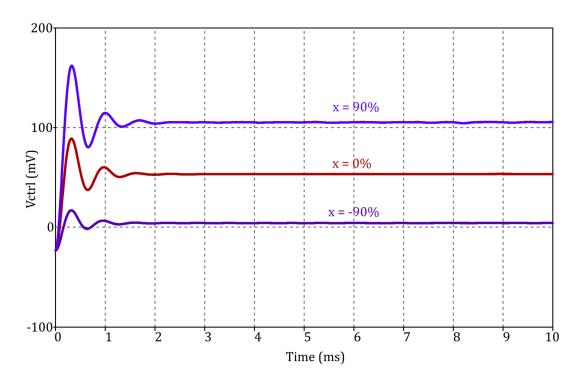

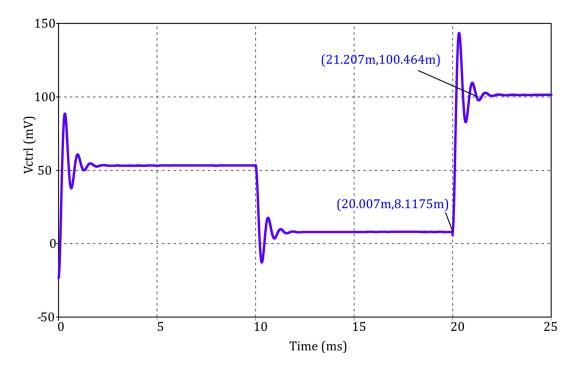

| Figure 3.32 Interface time domain behavior for three different x values103 $\!\!\!\!$           |

| FIGURE 3.33 INTERFACE DYNAMIC RESPONSE103                                                       |

| FIGURE 3.34 FABRICATED DISCRETE INTERFACE106                                                    |

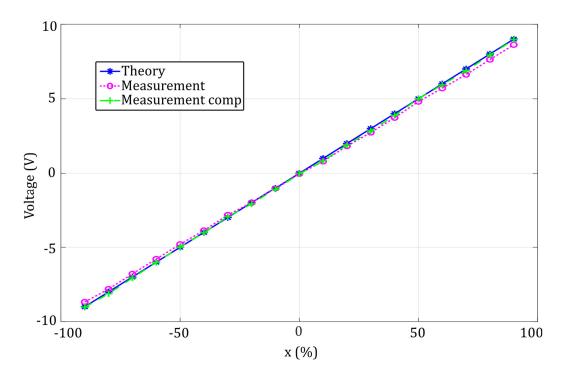

| FIGURE 3.35. COMPARISON BETWEEN THEORETICAL AND MEASURED INTERFACE STATIC                       |

| BEHAVIOUR107                                                                                    |

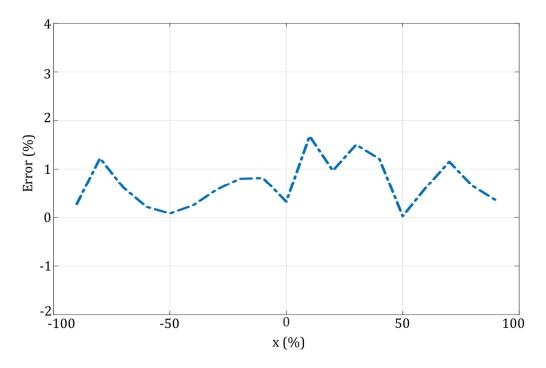

| FIGURE 3.36. THEORY VS MEASUREMENTS ABSOLUTE RELATIVE ERROR                                     |

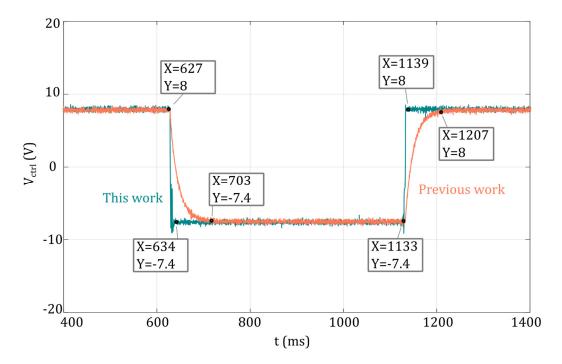

| FIGURE 3.37. COMPARISON BETWEEN TWO MEASURED DYNAMIC RESPONSES: THE INTEGRAL                    |

| RESPONSE (RED) VS THE INTEGRAL AND PROPORTIONAL ONE (GREEN) OF THE PRESENTED                    |

| WORK                                                                                            |

| FIGURE 3.38 REAL-WORLD DIFFERENTIAL CAPACITIVE SENSOR A) EQUIVALENT MODEL; B) DRIVEN            |

| BY AN AC SOURCE                                                                                 |

| FIGURE 3.39 COMPENSATION FEEDBACK LOOP APPLIED TO AN AUTO-BALANCED BRIDGE INTERFACE             |

| [50]110                                                                                         |

| FIGURE 3.40 THE FEEDBACK LOOP SCHEMATIC DIAGRAM [50]                                                         |

|--------------------------------------------------------------------------------------------------------------|

| FIGURE 3.41 A) THE UTILIZED NEGATIVE IMPEDANCE CONVERTER; B) THE COMPLETE VCNIC.                             |

|                                                                                                              |

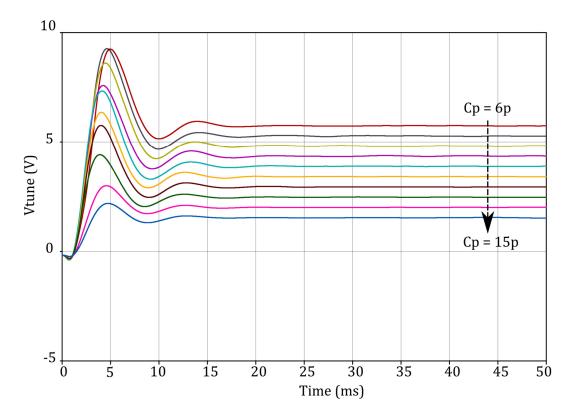

| Figure $3.42$ Dynamic response of the simulated compensation loop at different values                        |

| OF CP                                                                                                        |

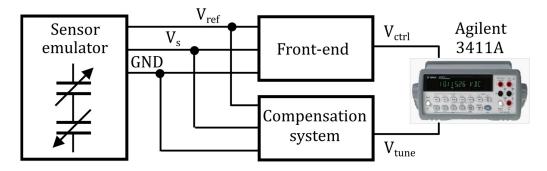

| FIGURE 3.43 THE BLOCK SCHEME OF THE EMPLOYED EXPERIMENTAL SETUP 117                                          |

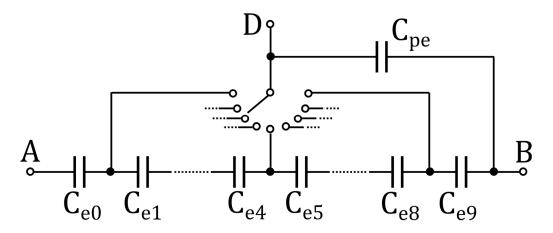

| FIGURE 3.44 SCHEMATIC OF THE EMULATED DIFFERENTIAL CAPACITIVE SENSOR                                         |

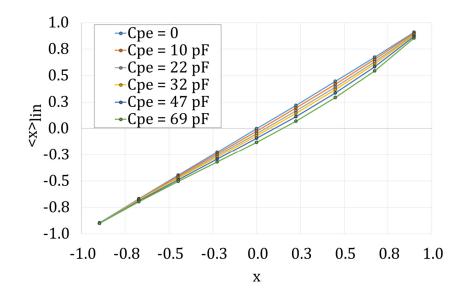

| Figure 3.45 The estimated linearized sensor measurand $$ versus the emulated                                 |

| VALUE X, WITH DIFFERENT SCENARIOS OF CPE VALUES                                                              |

| FIGURE 4.1 IDEAL CURRENT MODE APPROACH                                                                       |

| FIGURE 4.2 CURRENT MODE APPROACH IN PRESENCE OF PARASITIC CAPACITANCES                                       |

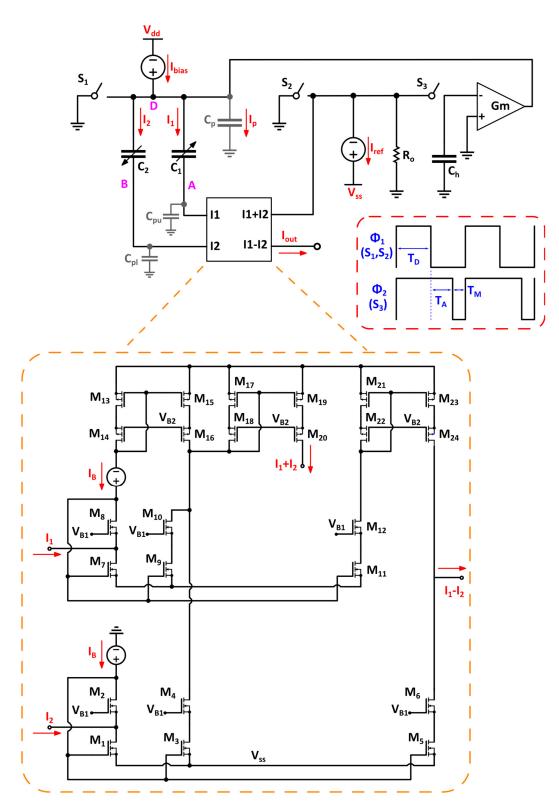

| FIGURE 4.3 BLOCK DIAGRAM OF THE PROPOSED INTERFACE [55]                                                      |

| FIGURE 4.4 ACTUAL IMPLEMENTATION OF THE INTERFACE UNDER ANALYSIS [55]                                        |

| Figure 4.5 Block diagram of the interface proposed in $\left[56 ight]$ and a focus on the summing            |

| SUBTRACTING BLOCK AND CLOCK SIGNALS TIMINGS                                                                  |

| FIGURE 4.6 BLOCK DIAGRAM OF THE INTERFACE DURING THE AUTOTUNE PHASE [56]                                     |

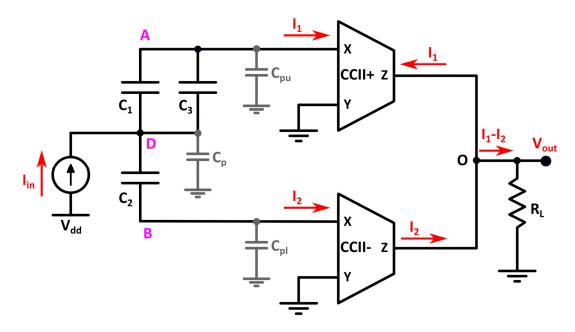

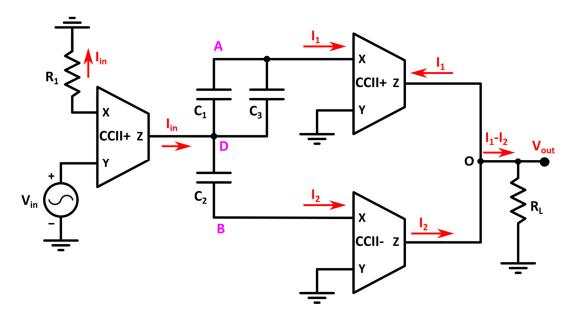

| FIGURE 4.7 CCII BASED DIFFERENTIAL CAPACITIVE SENSOR INTERFACE [57]                                          |

| FIGURE 4.8 CCII BASED INTERFACE WITH A REFERENCE VOLTAGE GENERATOR [57]                                      |

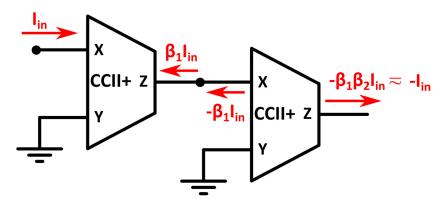

| FIGURE 4.9 A NEGATIVE CCII IMPLEMENTED BY MEANS OF TWO POSITIVE CCIIS; IT IS SUPPOSED                        |

| THAT THE B PARAMETER IS CLOSE TO UNITY SO THAT CAN BE NEGLECTED IN THE INPUT-                                |

| OUTPUT RELATIONSHIP                                                                                          |

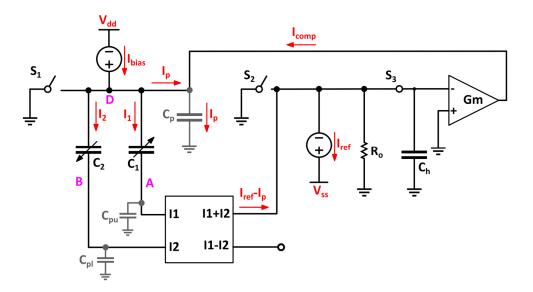

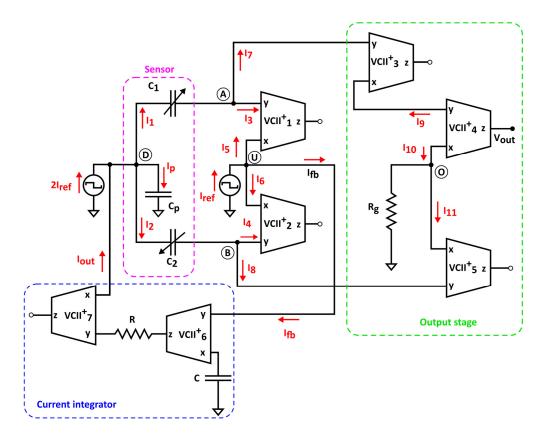

| FIGURE 5.1 THE PROPOSED VCII BASED INTERFACE WITH AUTOMATIC PARASITIC COMPENSATION                           |

| [63]                                                                                                         |

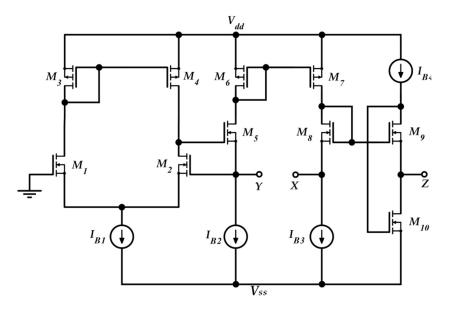

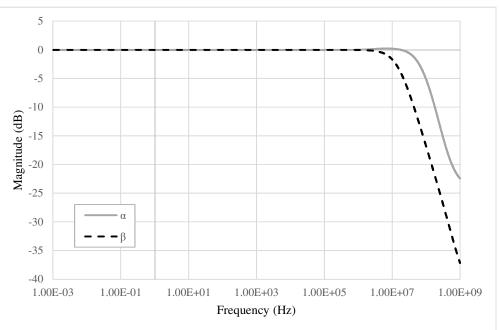

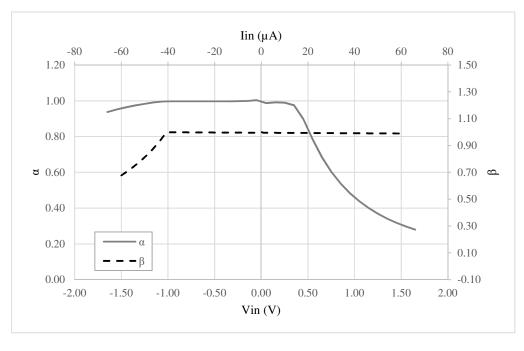

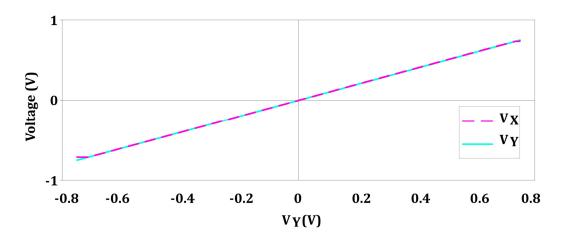

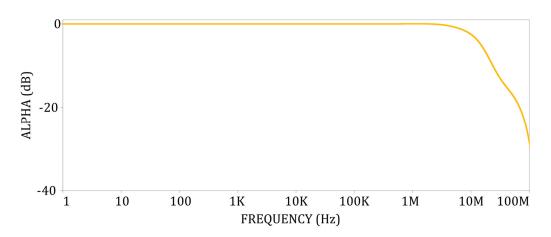

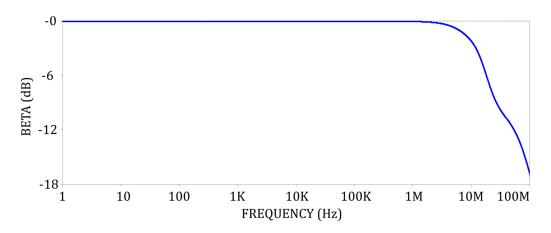

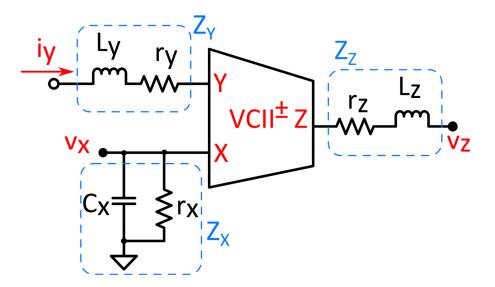

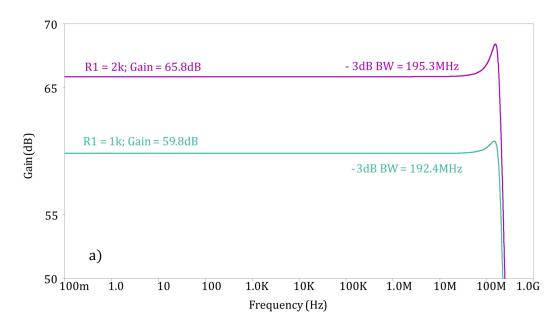

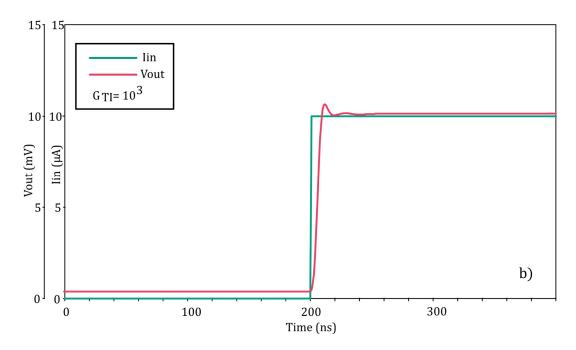

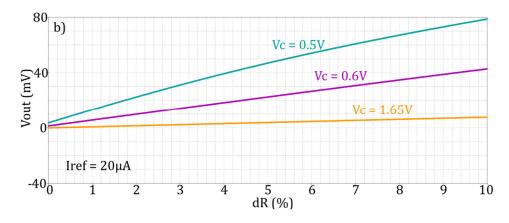

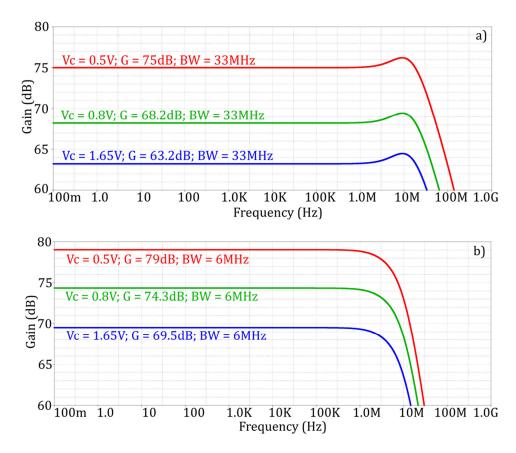

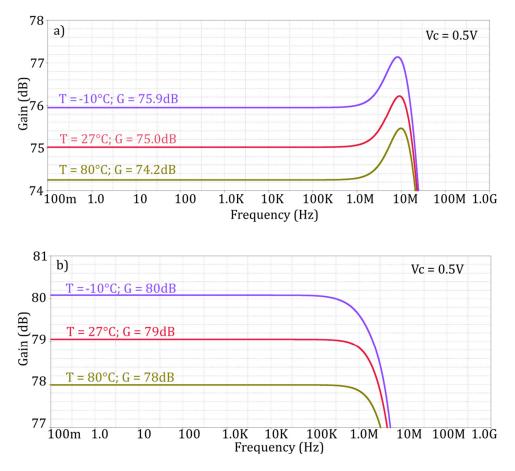

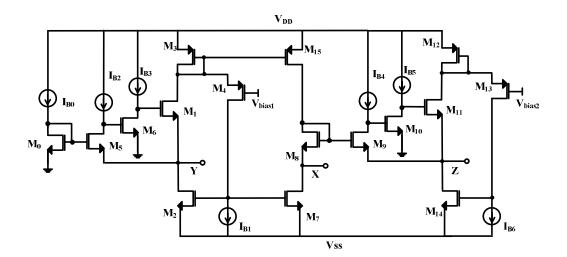

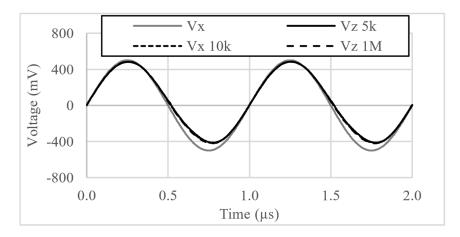

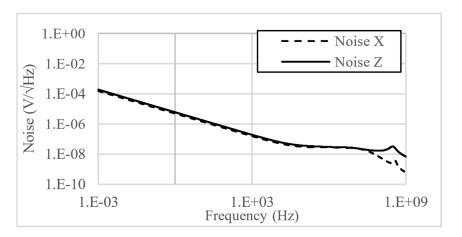

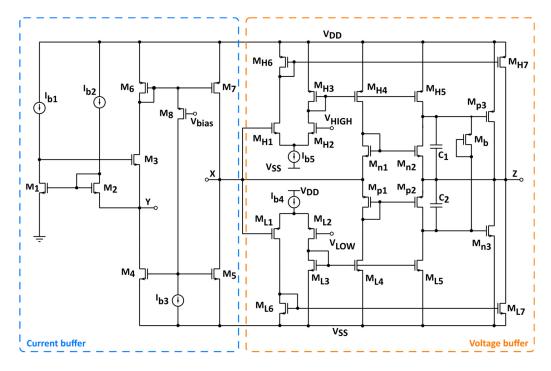

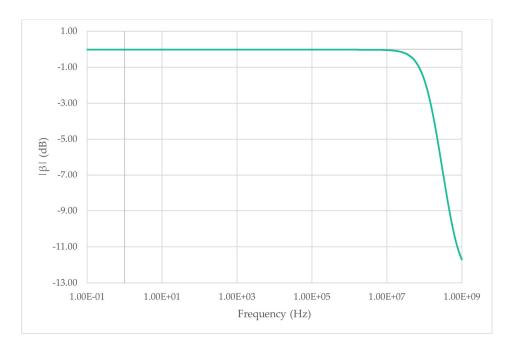

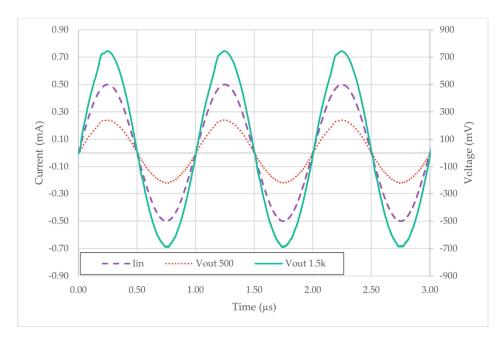

| Figure 5.2 The VCII used in the simulations: A) topology (see [101]) B) AC                                   |

| performances (determined with a $3 \text{ pF}$ load at X) c) DC performances                                 |

| (determined with A $1$ K $\!\Omega$ load at $Y$ for B simulations, and with A $100$ K $\!\Omega$ load at $Z$ |

| FOR A SIMULATIONS)                                                                                           |

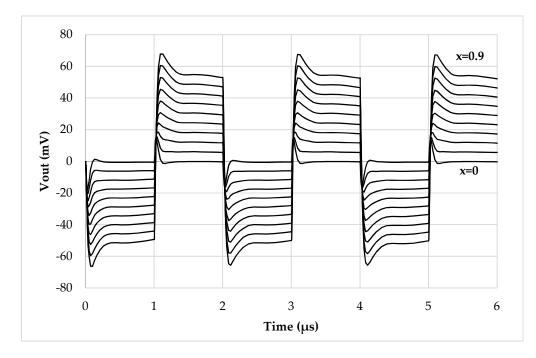

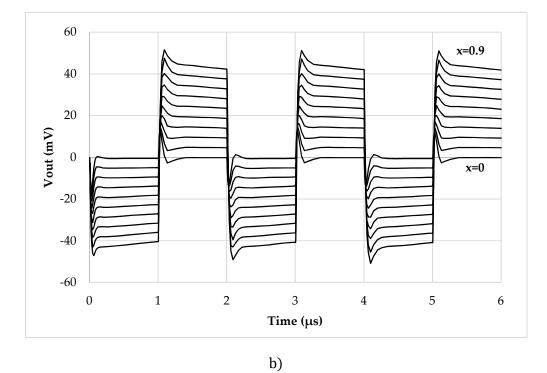

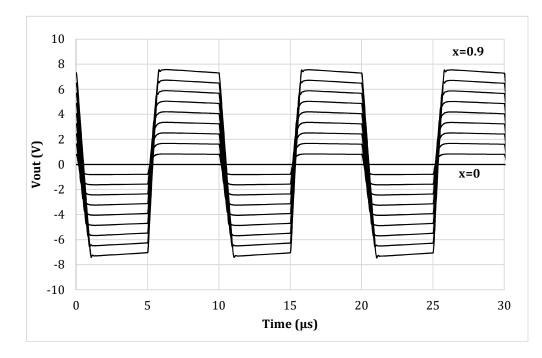

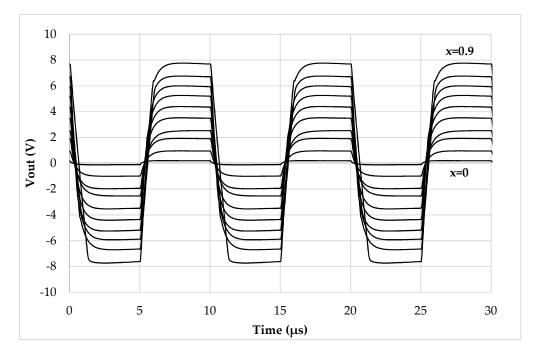

| FIGURE 5.3 TIME DOMAIN OUTPUT VOLTAGE WITH A) COMPENSATION ENABLED B) COMPENDISABLED.   |         |

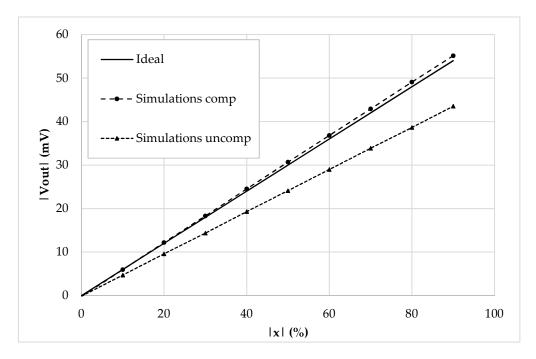

|-----------------------------------------------------------------------------------------|---------|

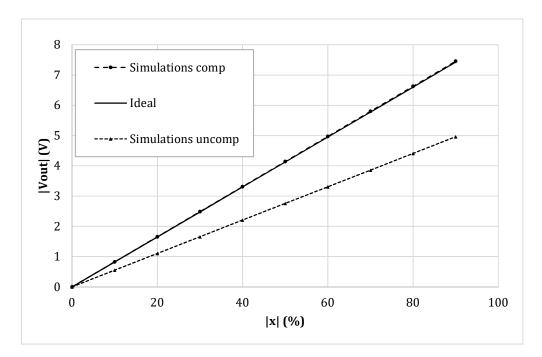

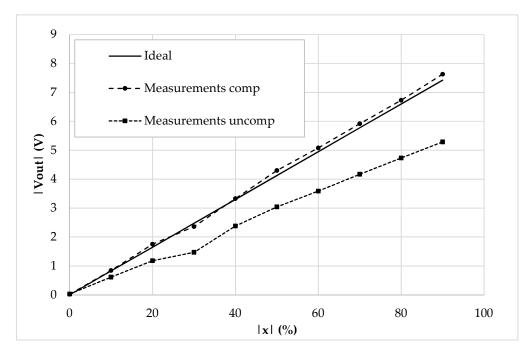

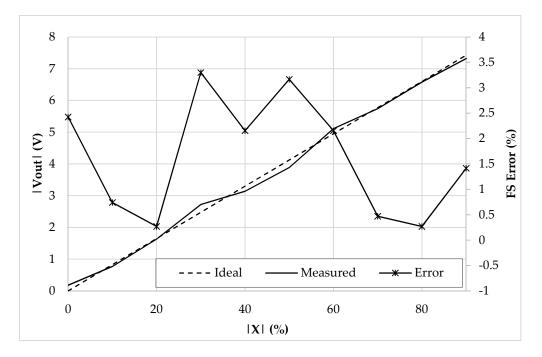

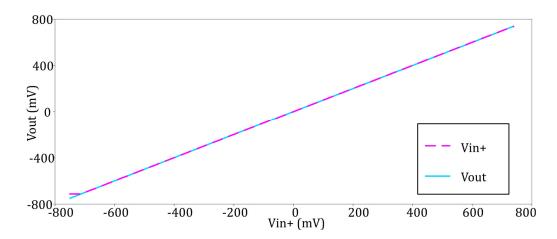

| FIGURE 5.4 DC CHARACTERISTIC ( VOUT  VS  X ) OF THE INTEGRATED INTERFACE                | 146     |

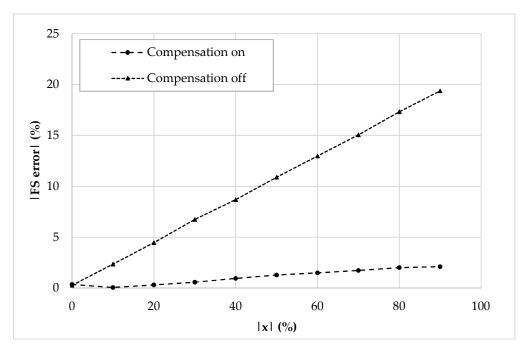

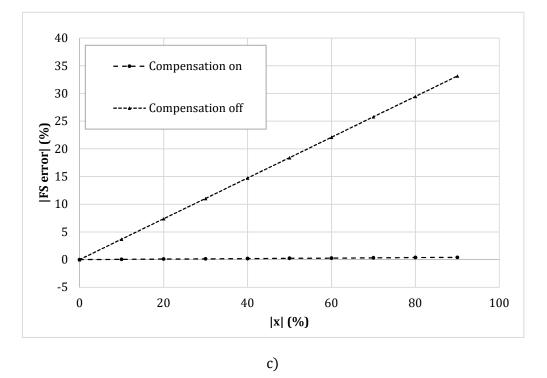

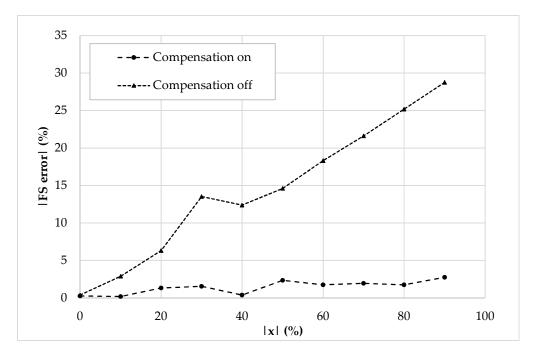

| FIGURE 5.5 FULL-SCALE ERROR (%) OF THE COMPENSATED AND UNCOMPENSATED INTE INTERFACE.    |         |

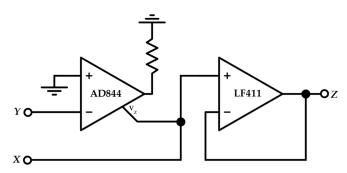

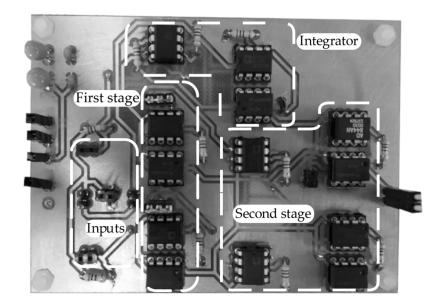

| FIGURE 5.6 DISCRETE VCII IMPLEMENTATION                                                 | 147     |

| FIGURE 5.7 DISCRETE INTERFACE SIMULATIONS: A) TIME DOMAIN OUTPUT VOLTA                  | AGE, B) |

| EXTRACTED DC CHARACTERISTIC, C) FULL-SCALE ERROR (%)                                    | 148     |

| FIGURE 5.8 THE PROTOTYPED INTERFACE.                                                    | 149     |

| FIGURE 5.9 TIME DOMAIN OUTPUT VOLTAGE OF THE PROTOTYPED INTERFACE                       | 150     |

| FIGURE 5.10 DC CHARACTERISTIC ( $ VOUT  vs  x $ ) of the prototyped interface           | 150     |

| FIGURE 5.11 FULL-SCALE ERROR (%) OF THE COMPENSATED AND UNCOMPENSATED PROT<br>INTERFACE |         |

| Figure 5.12 DC characteristic ( $ Vout $ vs $ x $ ) and full-scale error (%)            | OF THE  |

| PROTOTYPED INTERFACE WITH A $10~{ m pF}$ sensor baseline                                | 152     |

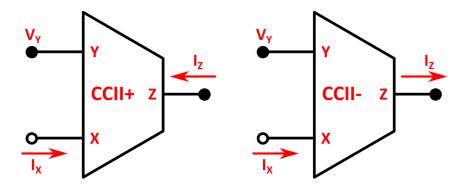

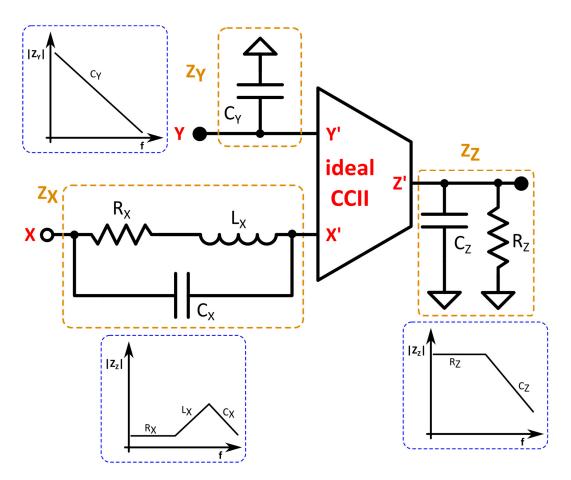

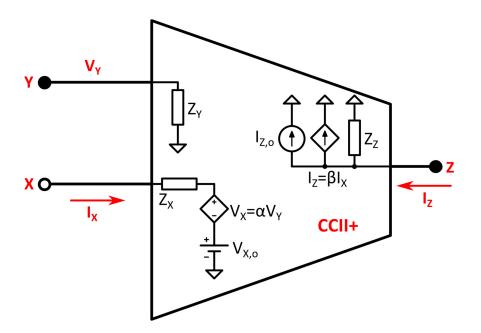

| FIGURE 6.1 HIGH LEVEL REPRESENTATION OF A A) CCII+; B) CCII                             | 155     |

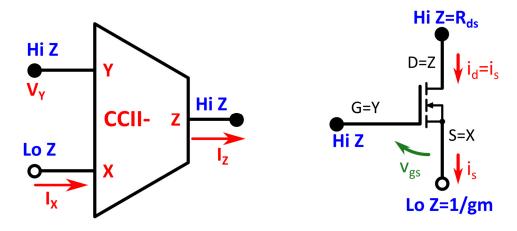

| FIGURE 6.2 ANALOGY BETWEEN A CCII AND A MOSFET.                                         | 156     |

| FIGURE 6.3 CCII IMPEDANCES AT EACH TERMINAL.                                            | 157     |

| FIGURE 6.4 REAL CCII EQUIVALENT CIRCUIT.                                                | 158     |

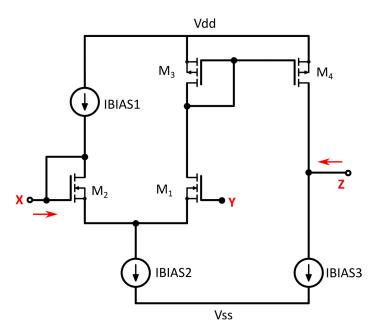

| FIGURE 6.5 CLASS A CCII BASED ON A DIFFERENTIAL PAIR.                                   | 159     |

| FIGURE 6.6 CLASS AB CCII BASED ON A DIFFERENTIAL PAIR.                                  | 160     |

| FIGURE 6.7 RTR CONSTANT GM CCII BASED ON A DIFFERENTIAL PAIR [81]                       | 161     |

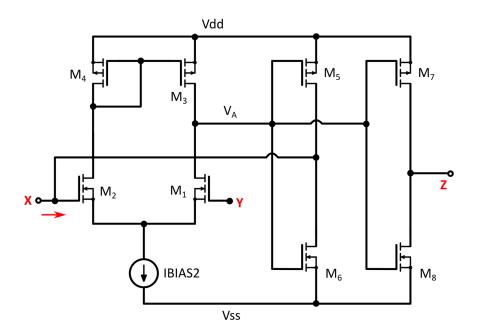

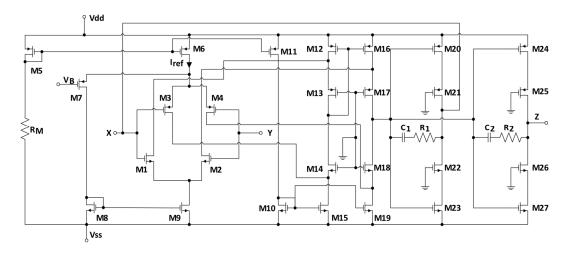

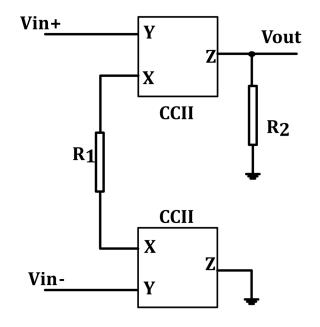

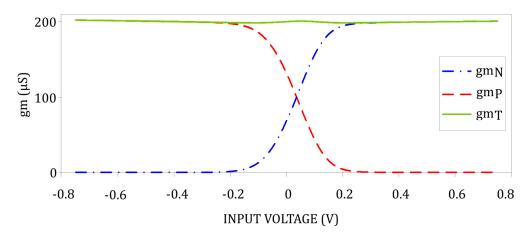

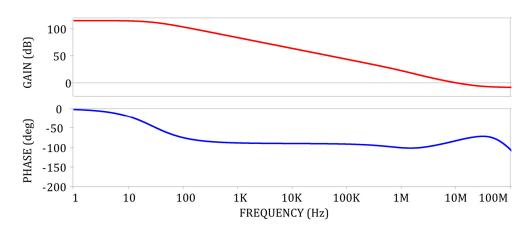

| FIGURE 6.8 BLOCK SCHEME OF THE UTILIZED CCII BASED IA                                   | 163     |

| FIGURE 6.9 CCII OPEN LOOP GM BEHAVIOR VS. INPUT COMMON MODE VOLTAGE.                    | 164     |

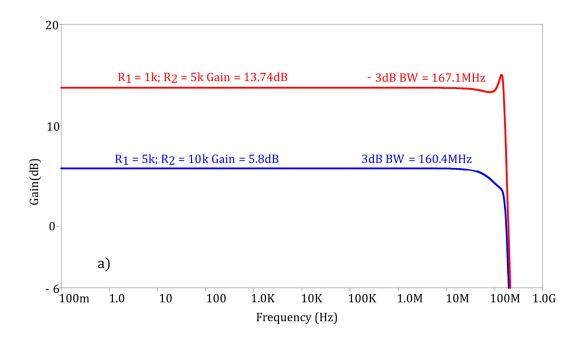

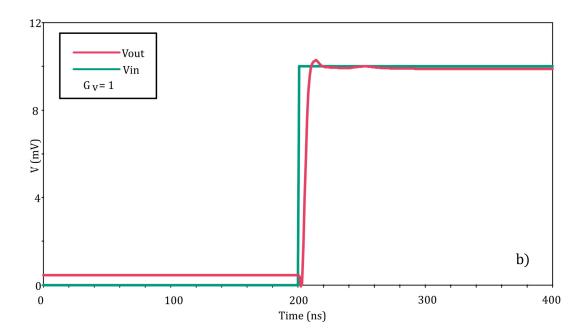

| FIGURE 6.10 CCII OPEN LOOP GAIN AND PHASE RESPONSE.                                     | 164     |

| FIGURE 6.11 CCII DC INPUT VOLTAGE CHARACTERISTICS.                                      | 165     |

| FIGURE 6.12 PARAMETER A VS. FREQUENCY.                                                  | 165     |

| FIGURE 6.13 PARAMETER B VS. FREQUENCY                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 6.14 IA DC INPUT VOLTAGE CHARACTERISTICS                                                                                                                                                                                                                                                                |

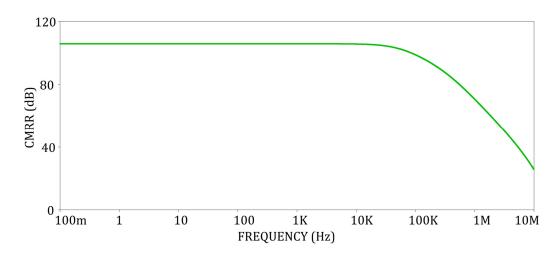

| FIGURE 6.15 IA COMMON MODE REJECTION RATIO                                                                                                                                                                                                                                                                     |

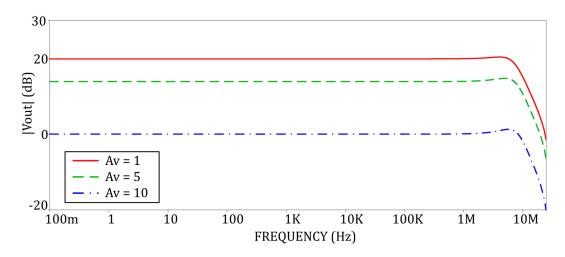

| FIGURE 6.16 IA AC PERFORMANCES AT DIFFERENT GAIN LEVELS                                                                                                                                                                                                                                                        |

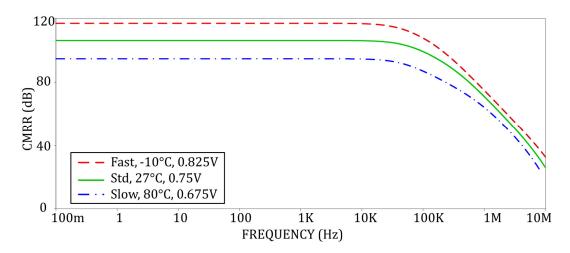

| FIGURE 6.17 CMRR CORNER ANALYSIS                                                                                                                                                                                                                                                                               |

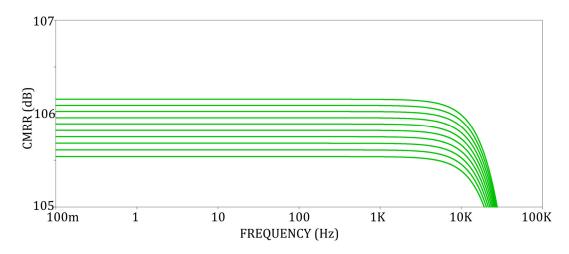

| Figure 6.18 CMRR variations for a $\pm 10\%$ input transistors mismatch                                                                                                                                                                                                                                        |

| FIGURE 6.19 THE PROPOSED DYNAMIC BIASING TOPOLOGY [91]170                                                                                                                                                                                                                                                      |

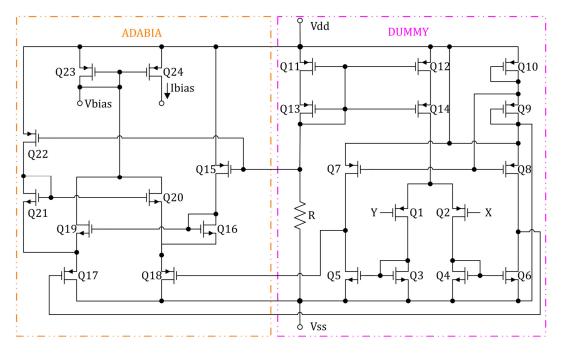

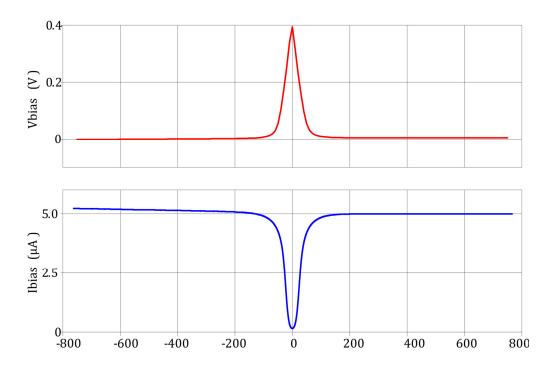

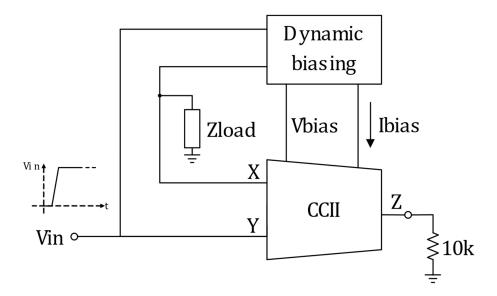

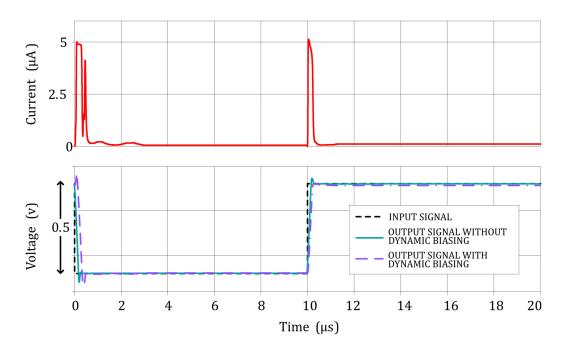

| Figure 6.20 Output voltage (above) and output current (below) of the dynamic biased circuit as a function of the input differential voltage [91] 172                                                                                                                                                           |

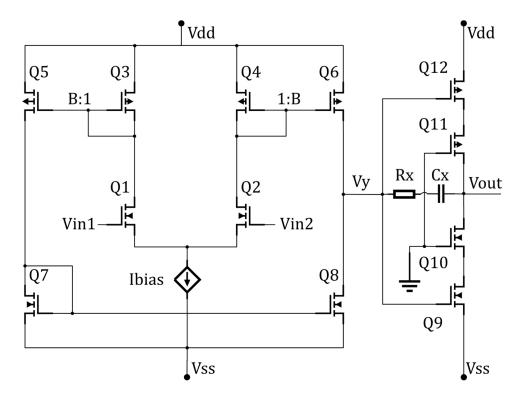

| FIGURE 6.21 THE PROPOSED CCII TOPOLOGY [91]                                                                                                                                                                                                                                                                    |

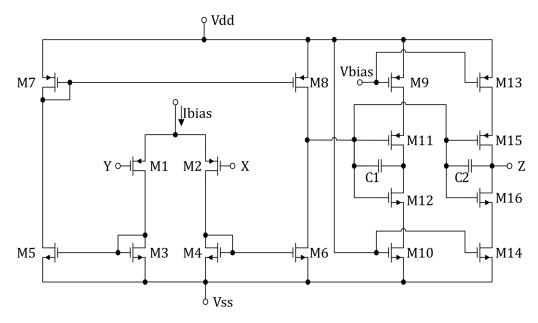

| FIGURE 6.22 THE DB-CCII ARCHITECTURE [91] 174                                                                                                                                                                                                                                                                  |

| Figure 6.23 Extra-current behavior (top) and comparison (bottom) on the step<br>response between the DB-CCII solution and a classical CCII circuit with a static<br>bias current equal to the maximum value of the extra current managed by the<br>adaptive solution. Input signal has been also depicted [91] |

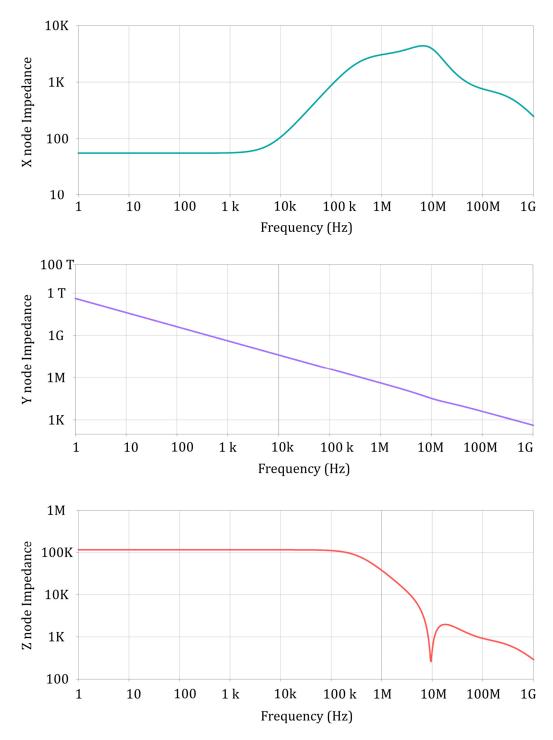

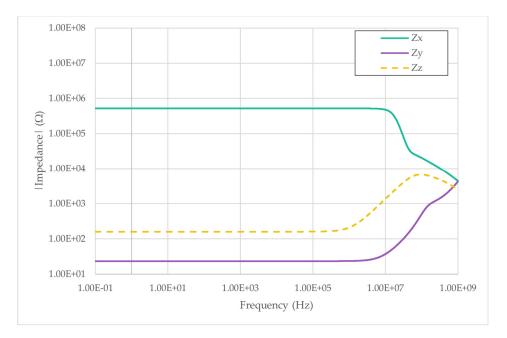

| Figure 6.24 Node impedances determined for a 5 $\mu A$ bias current [91] 176                                                                                                                                                                                                                                   |

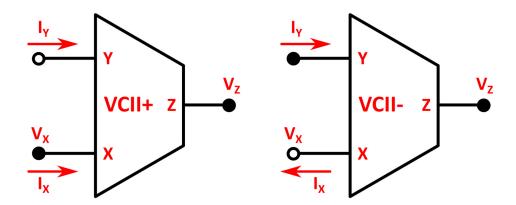

| FIGURE 6.25 HIGH LEVEL REPRESENTATION OF A A) VCII+; B) VCII                                                                                                                                                                                                                                                   |

| FIGURE 6.26 VCII IMPEDANCES AT EACH TERMINAL                                                                                                                                                                                                                                                                   |

| FIGURE 6.27 REAL VCII EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                       |

| FIGURE 6.28 SUPER TRANSISTOR-BASED VCII ARCHITECTURE [99]                                                                                                                                                                                                                                                      |

| FIGURE 6.29 SMALL SIGNAL EQUIVALENT CIRCUIT FOR X AND Y TERMINALS OF THE PROPOSED VCII [99].                                                                                                                                                                                                                   |

| Figure 6.30 VCII based configurations: A) I to V converter, B) V to I converter, C) voltage amplifier, d) voltage differentiator, e) voltage integrator                                                                                                                                                        |

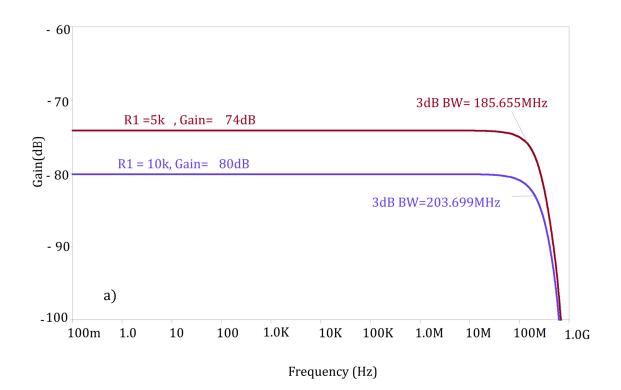

| Figure 6.31 VCII based I-to-V converter a) Frequency response and b) step response to a current input with amplitude of $10\mu A$                                                                                                                                                                              |

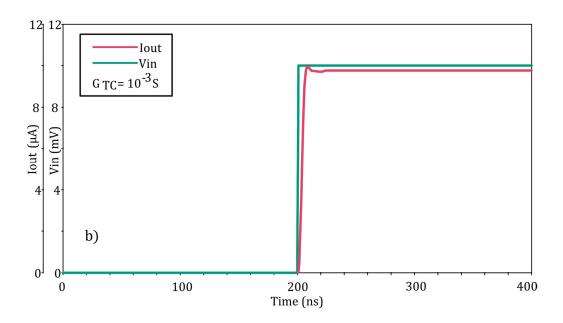

| FIGURE 6.32 VCII BASED V-TO-I CONVERTER A) FREQUENCY PERFORMANCE AND B) STEP RESPONSE TO A VOLTAGE STEP INPUT WITH AMPLITUDE OF 10MV                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 6.33 VCII BASED VOLTAGE AMPLIFIER A) FREQUENCY PERFORMANCE AND B) STEP<br>RESPONSE TO A VOLTAGE STEP INPUT OF 10MV                                        |

| FIGURE 6.34 TIME DOMAIN RESPONSE OF VCII BASED VOLTAGE DIFFERENTIATOR                                                                                            |

| FIGURE 6.35 TIME DOMAIN RESPONSE OF VCII BASED VOLTAGE INTEGRATOR                                                                                                |

| FIGURE 6.36 FLIPPED VOLTAGE FOLLOWER BASED VCII ARCHITECTURE [101]191                                                                                            |

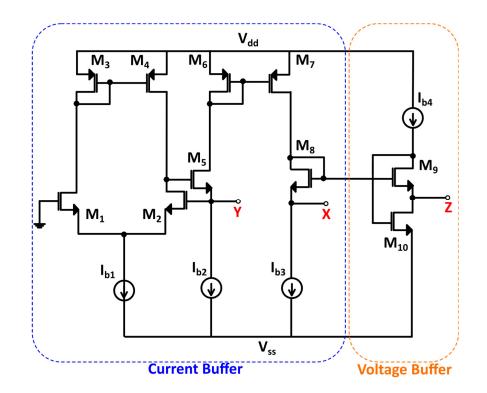

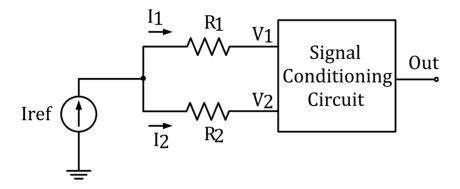

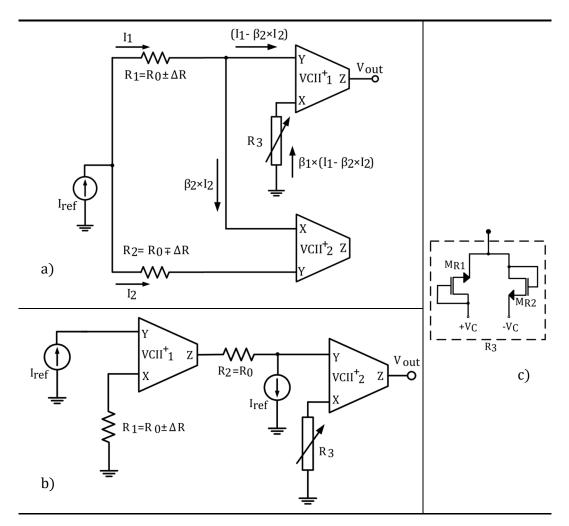

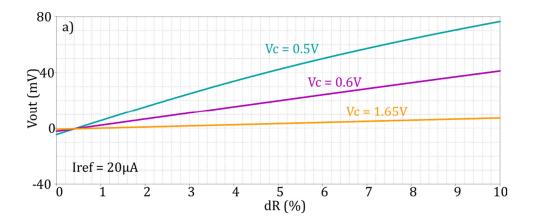

| FIGURE 6.37 CURRENT MODE WHEATSTONE BRIDGE193                                                                                                                    |

| FIGURE 6.38 PROPOSED VCII BASED CMWB CONFIGURATION FOR A) TWO SENSORS APPLICATIONS                                                                               |

| and b) single sensor applications; c) implementation of variable resistor $R_3$ [107]194                                                                         |

| FIGURE 6.39 DC RESPONSE OF THE PROPOSED CMWB OF A) FIG. 6.38A B) FIG. 6.38B                                                                                      |

| FIGURE 6.40 DIFFERENTIAL MODE FREQUENCY RESPONSE OF THE PROPOSED CMWB OF A) FIG. 6.38A B) FIG. 6.38B                                                             |

| Figure 6.41 Differential mode response of the proposed CMWBs of A) Fig. 6.38A b) Fig. 6.38B with R1=10 k $\Omega$ and R2=20 k $\Omega$ at different temperatures |

| FIGURE 6.42 CLASS AB HIGH DRIVE VCII ARCHITECTURE [108]199                                                                                                       |

| FIGURE 6.43 MODIFIED CLASS AB FVF CELL [108]200                                                                                                                  |

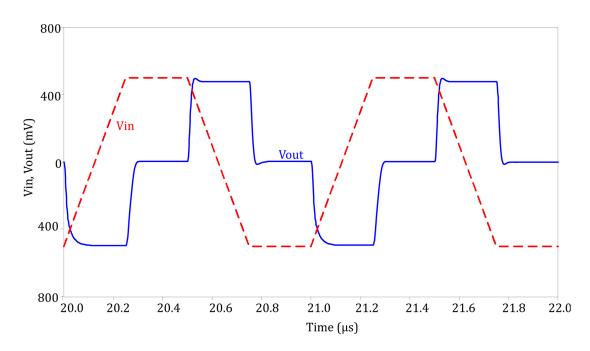

| FIGURE 6.44 Y TO X CURRENT TRANSIENT RESPONSE TO A STEP INPUT: FOCUS ON RISING (LEFT SIDE) AND FALLING (RIGHT SIDE) EDGES                                        |

| FIGURE 6.45 Y TO X CURRENT TRANSIENT RESPONSE TO A SINUSOIDAL INPUT203                                                                                           |

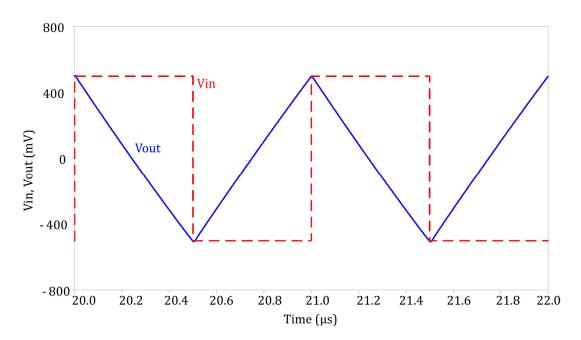

| FIGURE 6.46 X TO Z VOLTAGE TRANSIENT RESPONSE TO A STEP INPUT: FOCUS ON RISING (LEFT SIDE) AND FALLING (RIGHT SIDE) EDGES                                        |

| FIGURE 6.47 X TO Z VOLTAGE TRANSIENT RESPONSE TO A SINUSOIDAL INPUT204                                                                                           |

| FIGURE 6.48 NOISE PERFORMANCE OF THE PROPOSED VCII AT A) X B) Z204                                                                                               |

|                                                                                                                                                                  |

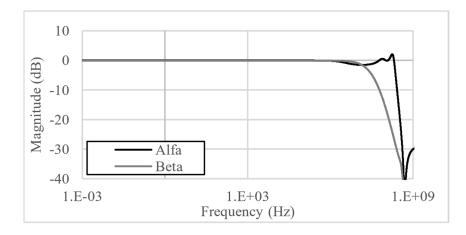

| FIGURE 6.49 FREQUENCY PERFORMANCE OF THE PROPOSED VCII FOR B (CURRENT GAIN BETWEEN Y AND X) AND A (VOLTAGE GAIN BETWEEN X AND Z)                                 |

| FIGURE 6.51 SMALL SIGNAL EQUIVALENT MODEL OF THE RTR VCII ARCHITECTURE [109] 207            |

|---------------------------------------------------------------------------------------------|

| Figure $6.52 \text{ DC}$ performances of the a parameter at different load levels connected |

| TO THE Z NODE                                                                               |

| FIGURE 6.53 DC PERFORMANCES OF THE B PARAMETER AT DIFFERENT LOAD LEVELS CONNECTED           |

| TO THE X NODE                                                                               |

| Figure 6.54 AC performances of the a parameter with a 1 pF capacitor connected to           |

| THE Z NODE                                                                                  |

| FIGURE 6.55 AC PERFORMANCES OF THE B PARAMETER                                              |

| FIGURE 6.56 PROPOSED VCII TERMINAL IMPEDANCES                                               |

| FIGURE 6.57 VCII USED AS A TIA                                                              |

# 1 INTRODUCTION

The need of electronic devices able to *sense and manipulate* magnitudes of different nature, such as mechanical, chemical, hydraulic or electromagnetic, is nowadays ubiquitous. Indeed, may it be the driving of an industrial process, or the monitoring of biological parameters of a patient, or even a simple data collection of the health of civilian infrastructures, a device or system able to translate the magnitude of interest into a signal that is actually understandable by the end user, is obviously essential.

### 1.1 Sensors: a brief review

Generally speaking, the name given to devices able to detect real phenomena is "transducers". A transducer is a device capable of converting a magnitude, often called measurand, from an energy domain to another, which does not necessarily correspond to the electrical one. Signal processing, however, needs electrical inputs to be acquired, this means that the energy domain in which a "sensing" process always aims to is the electrical one.

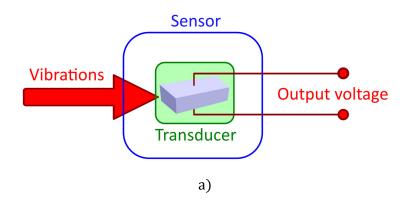

Devices or systems, which convert energy from a given domain to the electrical, are called "sensors". A sensor either can correspond to a single transducer (see Fig. 1.1a) or can be seen as a complex system made of multiple transducers, followed by an electronic circuit which carries out the final conversion (see Fig. 1.1b). For instance, a piezoelectric device is both a transducer and a sensor, since is capable of

converting vibrations into an electrical signal. On the other hand, a hot wire anemometer, like the name suggests, evaluates the wind speed by measuring how much a heater gets cooled down from a starting temperature. Therefore, the wind speed is converted into heat, which in turn varies a thermistor resistance whose changes are sent to an electronic readout interface (for example a Wheatstone bridge in Fig. 1b).

The final information coming from a sensor (or from a sensing system) can be of different nature. In fact, it can be fully analog, but also digital, ready to be processed by a microcontroller. In particular, in the latter case, analog-to-digital converters are required. Moreover, it is often necessary to equip the

Figure 1.1 a) single transducer sensor, b) multiple transducer plus interface sensor.

overall system with dual devices, i.e. digital-to-analog converters that supply one or more actuators, which carry out an inverse transduction, from an electrical domain to a non-electric one (the "actuator").

Capacitive sensors, in general, present important advantages over their counterparts such as resistive and piezoresistive sensors. Indeed, they show better sensitivity, temperature and drift performances and, most importantly, they consume virtually no power. Another noticeable advantage is that they can be micromachined together with the readout electronics over a silicon substrate (MEMS capacitive sensors), making them miniaturized without losing key features like sensitivity and resolution [1-4].

### 1.2 Capacitive sensors

#### 1.2.1 Physical properties

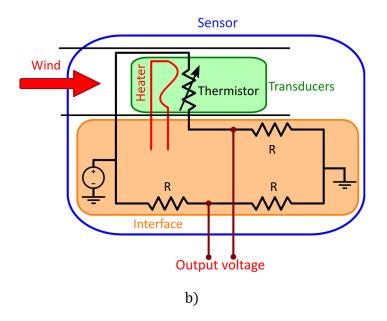

An interesting aspect of a capacitor, from a sensing point of view, is that capacitance value is influenced by its geometrical and physical properties. Taking into consideration two parallel plates facing each other, which is the most used geometry due to its ease of fabrication, it is possible to define its capacitance as:

$$C = \varepsilon_0 \varepsilon_r \frac{S}{d} \tag{1.1}$$

where  $\varepsilon_0$  and  $\varepsilon_r$  are the dielectric constants of the vacuum and of a specific medium respectively, *S* is the overlapping surface between the two electrodes and *d* is the distance between them (see Fig. 1.2). If an external magnitude is capable of modifying one of these parameters, a consequent variation in the capacitance value is experienced and, hence, can be read by a suitable electronic interface.

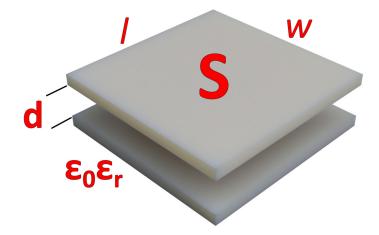

It is called '*spacing variation capacitive sensor*' a device (see Fig. 1.3a) where the variable magnitude is the distance between the two plates (Eq. 1.2). In this case, the space variation changes the value of the same capacitance according to the following relation:

$$C = \varepsilon_0 \varepsilon_r \frac{S}{(d + \Delta d)} \tag{1.2}$$

Figure 1.2 A parallel plates capacitive sensor configuration.

Since often one of the two plates is fixed, while the other is a vibrating conductive membrane, rather than the pure distance, the mean value of this magnitude across the entire plate area is given by:

$$C = \iint_{x,y} \varepsilon_0 \varepsilon_r \frac{1}{(d + \Delta d)} dx dy$$

(1.3)

Obviously, in Eq. 1.3 the magnitude  $\Delta d$  is a function of x and y. This configuration results to be very sensitive to the measurand since it acts on the smallest dimension of the sensor, so a reduced variation of distance can be reflected in a large variation of the capacitance. It is noticeable that variations of the capacitance with respect to the dimension d are nonlinear (Eq. 1.2); however, if the evaluated parameter is the impedance ( $Zc = 1/j\omega C$ ) the same relationship becomes linear:

$$Z_{C} = \frac{d + \Delta d}{j\omega\varepsilon_{r}\varepsilon_{0}S}$$

(1.4)

Similarly, an 'overlapping area variation capacitive sensor' relies on the modification of the common surface shared by the two electrodes (see Fig. 1.3b). An advantage of this approach with respect to the previous one is that capacitance variation is inherently linearly related to the surface variations. On the other hand, however, since plate dimensions are much larger than the gap between them, the sensitivity of this approach results lower if compared to the previous one (in other words, to produce the same amount of capacitance alteration, the measurand must

have a wider variation). Lastly, it is possible to take advantage of the dielectric constant of different mediums so to achieve a capacitance variation as shown in Fig. 1.3c. This specific scenario is often used to detect liquid or gas levels into a tank, or even to reveal the presence of a particular gas in an environment. Remarkably, these techniques can be used not only for linearly moving electrodes, but also to detect rotation and tilt angles. More complex structures (based on arrays of parallel plates capacitors) can act as multidimensional detectors, which means that they can simultaneously and independently sense more than one measurand variations.

Figure 1.3 Three different use cases for a parallel plates capacitive sensor: a) distance variations; b) overlapping surface variations; c) dielectric constant variation.

#### 1.2.2 Basic interfaces for capacitive sensors

Interface type and performances are strictly related to the designer needs and to the application. The main key points that determine the appropriate choice for the interface are the baseline of the sensor, how broadly it can vary, how much common mode disturbs can affect the measurement (environment), how parasitic capacitances of the interface are placed with respect to the sensor, how much power can be consumed by the circuitry and, in some cases, how much space the circuitry can occupy (or, in other words, how complex the interface is). Also, an accurate analysis of the application scenario is mandatory before designing the sensor interface [4].

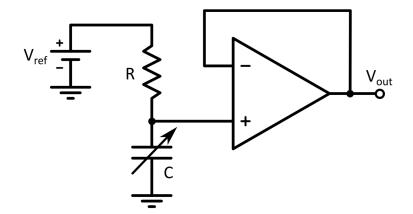

The first and most simple method is based on a DC readout. A basic circuit is given in Fig. 1.4. The working principle is the following: the sensing capacitor is precharged to a reference voltage  $V_{ref}$ , then, by supposing that the signal varies with a frequency greater that 1/RC, it is possible to consider the charge accumulated at the capacitor electrodes as a fixed value equal to:

$$q_{std} = C_{bl} V_{ref} \tag{1.5}$$

where  $C_{bl}$  is the value of the capacitor at the steady state (baseline). Then, by knowing that C = Q/V, it is possible to rewrite Eq. 1.5 as:

$$V_{out} = \frac{C_{bl} V_{ref}}{C_x} \tag{1.6}$$

where  $C_x$  represents the value of the sensing capacitor under the action of the measurand. Although very straightforward, this method lacks robustness with respect to circuital noise, works only for relatively fast capacitor variations and requires an extremely high impedance and low offset amplifying stage. Moreover, owing to the constraint on the time constant, it is not good for wide variations of the sensor from its baseline.

A solution that is particularly suitable for large variations from the baseline is the so-called capacitance to frequency (or period) conversion. The key point of this technique is the employment of the sensor in an oscillator configuration (even a

Figure 1.4 DC readout technique.

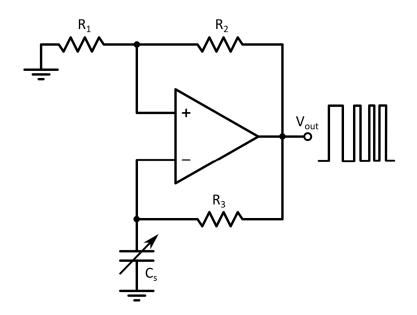

basic RC oscillator) and the tracking of its variations by measuring changes in the output frequency. Sometimes, rather than on the frequency, output variations are induced on the duty cycle of the signal. Fig. 1.5 depicts a simple astable oscillator where  $C_s$  represents the sensing capacitor. The relationship that links the frequency to the capacitor is the following:

$$f_{out} = \frac{1}{2R_3 C_s \ln\left(1 + 2\frac{R_1}{R_2}\right)}$$

(1.7)

According to the oscillator nature (RC, LC and so forth) it is possible to reach different frequency ranges. As noticeable from Eq. 1.7, RC oscillators produce an output frequency that is proportional to 1/RC, whereas for LC oscillators, the output frequency is proportional to  $1/\sqrt{\text{LC}}$ , so the designer has to take into account the output non linearity.

This kind of readout technique has numerous advantages. One of the most noticeable is that they do not require knowing the capacitor baseline to perform the readout, this reflects in the possibility to achieve good measurements even if the sensor drifts with time.

Another benefit is that the output is intrinsically digital: measuring a time, for a microcontroller or a single board computer, does not require the presence of ADCs and hence reduces the system complexity and the conversion error.

On the other hand, drawbacks of oscillator-based interfaces are their sensitivity to stray capacitances and electronic mismatches, and their poor noise rejection. This can lead to accuracy errors and, in general, requires specific precaution at design

Figure 1.5 RC oscillator based readout interface.

stage, like inserting shielding lines and complicating the actual interface. Another critical aspect is that an oscillator based interface has typically a low sensitivity value, which makes it unsuitable for extremely low capacitance variations from the baseline value.

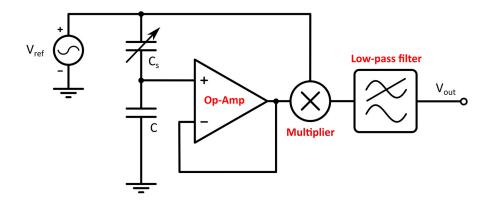

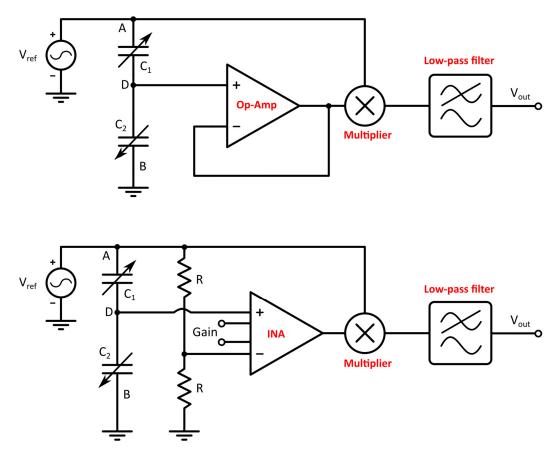

One of the best methods to detect very low measurand variations, maintaining high accuracy levels, is to make use of synchronous demodulation architectures. The basic idea here is to excite the sensor by a high frequency signal (typically a sinusoidal signal with a frequency greater than 10 kHz) and then, through suitable circuitry, to bring back the measurement output to the baseband through a demodulation stage. This process, although intricate at a first glance, has many benefits. First, exciting a capacitor with a sufficiently high frequency reduces its impedance. This allows to relax the high impedance requirements for the primary conversion stage, minimizing matching errors. Second, the presence of a low pass filter during the demodulation process allows to cut down higher frequencies noise. Third, being an AC excited technique, part of the parasitic capacitances are inherently nullified (this will be discussed deeper in the following).

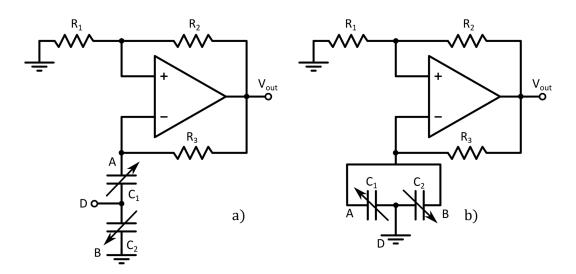

A simple circuit that exploits the synchronous demodulation is given in Fig. 1.6. As visible, the sensor is coupled with a reference capacitor through a voltage divider. A simple non inverting buffer reads the voltage at the output of the divider and feeds it to a demodulator. It consists of a multiplier and a filter: the multiplier uses a

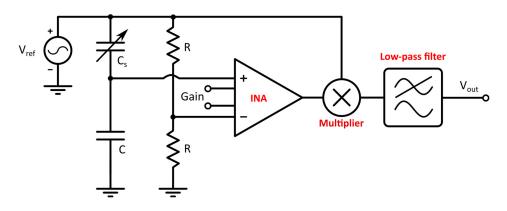

reference signal with the same frequency and phase respect to the buffer output (synchronous) to generate the DC output together with an unwanted high frequency signal, which is removed by the filter. An improved version of the same interface is shown in Fig. 1.7. Rather than relying on a simple voltage divider, it uses a bridge-based architecture to perform a fully differential measurement in order to improve the rejection to common mode disturbs increasing the resolution of the whole interface.

The best choice for the first stage is, in this case, an instrumentation amplifier (INA) since, unlike a simple Op-Amp, offers a suitably high impedance at both inputs while converting the signal to single-ended maintaining a controllable gain.

There are several techniques to use a bridge-based architecture with wide varying capacitive sensors. They will be analysed in the next chapters.

Figure 1.6 Single-ended synchronous demodulation technique applied to capacitive sensing

Figure 1.7 Fully differential synchronous demodulation technique.

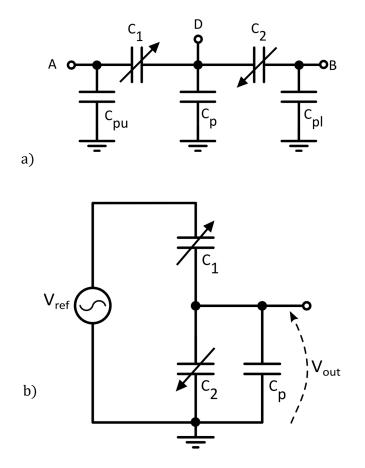

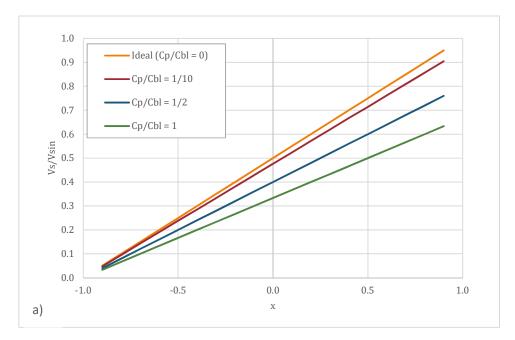

### 1.3 Differential capacitive sensors

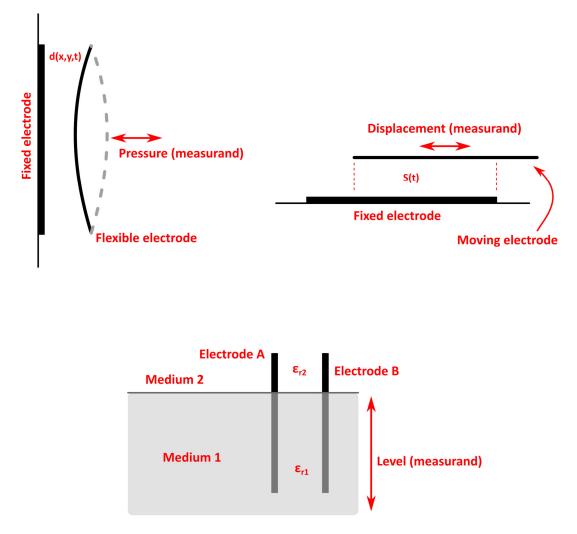

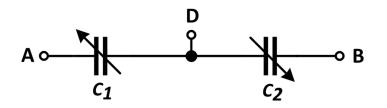

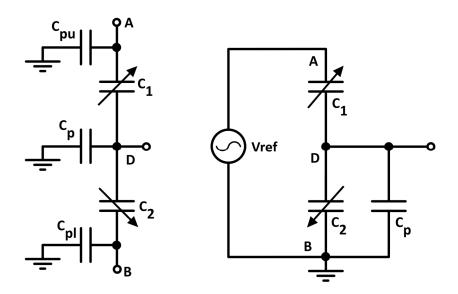

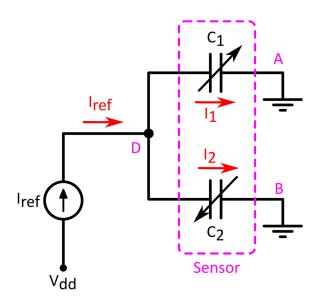

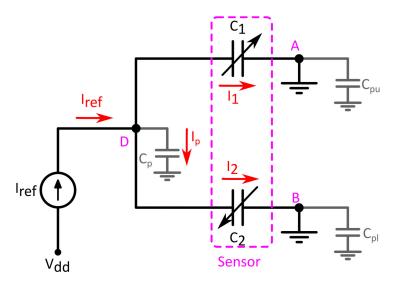

A differential capacitive sensor, depicted in Fig. 1.8, is an important subset of the capacitive sensors family. It is a three terminals device made of a couple of capacitors,  $C_1$  and  $C_2$ , which share a common node (called *D*). The value of these two capacitors vary from a common baseline in a differential fashion under the action of the measurand. The main advantage of this behavior is that it allows to eliminate common mode disturbs from the readout process, thus increasing the overall sensitivity and resolution of the sensor, making them suitable in applications where low capacitive variations are induced by the measurand (such as measurement of acceleration, dielectric characteristics of a medium, angular velocity, displacement and so on [5-7]).

### 1.3.1 Physical properties

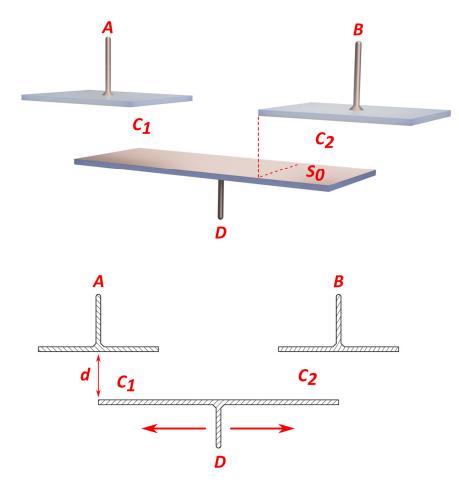

According to the physical behavior of a differential capacitive sensor in response to the measurand, it is possible to divide them into two main categories: linear sensors and hyperbolic sensors. Fig. 1.9 represents a linear differential capacitive sensor: as visible, it consists of three plates, two of them are fixed (the upper ones), while the third one (the bottom one) is free to move. When no external magnitude is applied, they lay at a certain distance *d*, sharing a certain amount of area *S*<sub>0</sub>. These conditions define the baseline of the sensor, *C*<sub>b</sub>, which can be calculated according to Eq. 1.1. The action of the measurand here determines a differential change in the overlapping areas of the three plates.

Unlike the simple capacitive sensors, it is possible to define a range of variations for the sensor uniquely as follows:

$$0 < C_{1,2} < 2C_{bl} \tag{1.8}$$

Figure 1.8 Ideal equivalent model for a differential capacitance sensor.

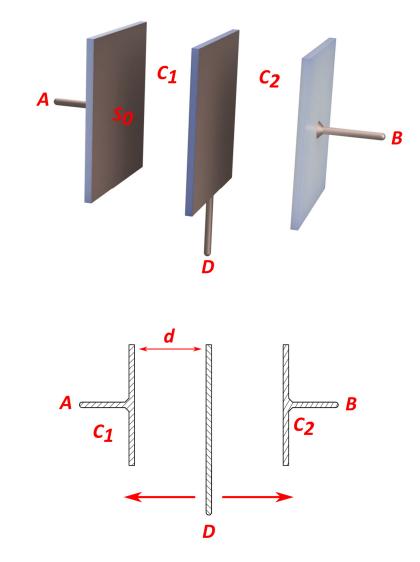

Fig. 1.10 represents a hyperbolic differential capacitive sensor. The baseline condition can be calculated with the same procedure utilized in the linear sensors. However, for this kind of sensors, the measurand acts on the distance between the three plates: the external ones are typically fixed, while the internal one is movable. As a consequence, the range in which a hyperbolic sensor varies can be estimated as:

$$\frac{C_{bl}}{2} < C_{1,2} < \infty \tag{1.9}$$

Based on what analyzed so far, it is possible to make some considerations. As already pointed out in the previous paragraphs, a hyperbolic sensor tends to be more sensitive to the measurand respect to the linear counterpart due to the fact that, for any given displacement, the smallest dimension (d) is much more affected in terms of percentage variation that the largest one.

Figure 1.9 A linear differential capacitive sensor.

Figure 1.10 A hyperbolic differential capacitive sensor.

This makes a linear sensor more suitable for measurands with large variations.

Eq. 1.8 and Eq. 1.9 show the difference in the ranges that the two different options can assume. On one hand, linear sensors are easier to interface with, due to the finite variation span. On the other, however, the fact that one of the two capacitors can assume very low values, makes them more addicted to the effects of parasitic capacitors in some applications. For both of the options, the extreme boundary conditions cannot be reached because the differential capacitor would degenerate into a simple capacitor.

#### 1.3.2 Parametrization

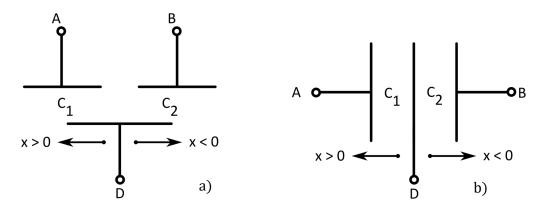

Regardless of the type of sensor, due to the intrinsic differential behavior, the evaluation of the measurand can be pursued by evaluating a dimensionless parameter x, which can be defined as the ratio between the difference of the two capacitors  $C_1$  and  $C_2$  of the sensor, and their sum:

$$x = \frac{C_1 - C_2}{C_1 + C_2} \tag{1.10}$$

In other words, *x* defines how much the sensor value has changed relatively to the baseline, therefore it is often expressed as a percentage. As easily noticeable, its variations are bounded between -1 and 1, values that, as visible from Eq. 1.8 and Eq. 1.9 can be never reached.

From an analytical perspective, it is therefore advantageous to parametrize the behavior of a differential capacitance sensor with respect to *x*. Eq. 1.11 shows how a linear sensor can be expressed as a function of *x*:

$$C_1 = C_{bl}(1+x)$$

(1.11)

$C_2 = C_{bl}(1-x)$

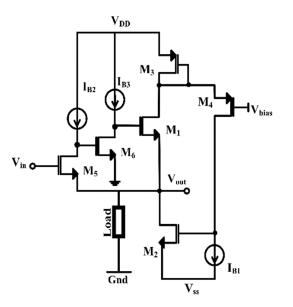

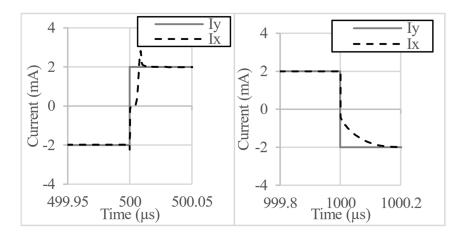

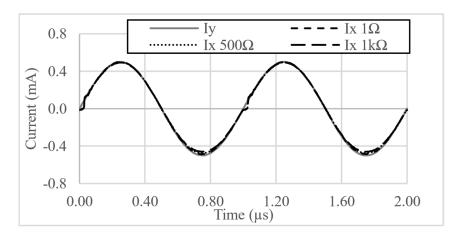

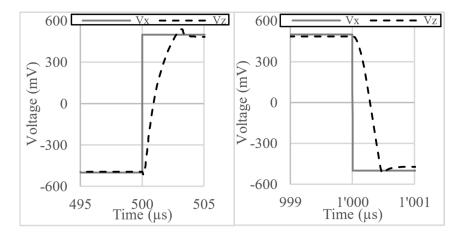

The positive and negative sign are given to the *x* according to Fig. 1.11a. Similarly, Eq. 1.12 shows how a hyperbolic sensor can be parametrized: